- •Федеральное агентство по образованию

- •1. Основы электрических измерений

- •1.1. Основные понятия и определения

- •1.2. Точностные характеристики средств измерений

- •1.3. Анализ статических погрешностей электронных схем

- •2. Простейшие электронные цепи и методы их анализа

- •2.1. Основные понятия и определения

- •2.2. Применение операторного метода к расчету электрических цепей

- •2.2.1. Прямое преобразование Лапласа

- •2.2.2. Обратное преобразование Лапласа

- •3. Типовые структуры электронных устройств и их свойства

- •3.1. Последовательная структура и ее свойства

- •3.2. Параллельная структура и ее свойства

- •3.3. Встречно-параллельное соединение

- •3.4. Задачи

- •4. Пассивные полупроводниковые компоненты электронных цепей

- •4.1. Полупроводниковые диоды и стабилитроны

- •4.2. Примеры применения полупроводниковых диодов

- •4.3. Светодиоды

- •4.4. Фотодиоды

- •5. Активные полупроводниковые компоненты электронных цепей

- •5.1. Биполярные транзисторы и их применение

- •5.1.1. Структура и принцип действия биполярных транзисторов

- •5.1.2. Характеристики и параметры биполярных транзисторов

- •5.1.3. Обеспечение усилительного режима бт в схемах

- •В результате получаем

- •5.1.4. Малосигнальные эквивалентные схемы и усилительные параметры бт

- •5.1.5. Амплитудно-частотные характеристики бт

- •5.1.6. Элементы транзисторной схемотехники

- •5.2. Полевые транзисторы и их применение

- •5.2.1. Классификация и общие особенности полевых транзисторов

- •5.2.2. Статические характеристики и дифференциальные параметры

- •5.2.3. Способы задания смещения в усилительных каскадах на пт

- •5.2.4. Малосигнальные эквивалентные схемы и усилительные параметры пт

- •5.2.5. Температурная стабильность параметров пт

- •5.2.6. Передаточная функция и динамические свойства пт Инерционные свойства пт описываются передаточной функцией вида

- •5.3. Задачи

- •6. Интегральные микросхемы и их классификация

- •7. Аналоговые интегральные микросхемы и их применение

- •7.1. Операционные усилители и их применение

- •7.1.1. Понятие идеального операционного усилителя

- •7.1.2. Принципы и примеры расчета схем с операционными усилителями

- •7.1.3. Динамические свойства устройств на операционных усилителях

- •7.1.4. Точностные характеристики устройств на операционных усилителях

- •7.1.5. Применение операционных усилителей

- •7.1.6. Задачи

- •7.2. Компараторы

- •7.3. Аналоговые ключи и коммутаторы

- •7.4. Устройства выборки-хранения

- •7.5. Интегральный таймер

- •7.5.1. Задачи

- •7.7. Справочные данные на оу

- •8. Цифро-аналоговые и аналого-цифровые преобразователи

- •8.1. Цифро-аналоговые преобразователи (цап)

- •8.2. Аналого-цифровые преобразователи (ацп)

- •9. Цифровые интегральные микросхемы и их применение

- •9.1. Элементы алгебры логики

- •9.2. Основные типы цифровых имс

- •9.3. Параметры цимс

- •9.4. Комбинационные логические цепи

- •9.4.1. Основные разновидности комбинационных логических цепей

- •9.4.2. Синтез комбинационных логических цепей

- •9.5. Последовательностные логические цепи

- •9.5.1. Классификация последовательностных логических цепей

- •9.5.2. Триггеры

- •9.5.3. Регистры

- •9.5.4. Счетчики импульсов

- •9.6. Применение цифровых имс в импульсных цепях

- •9.7. Задачи

- •10. Микросхемы полупроводниковых запоминающих устройств

- •10.1. Классификация полупроводниковых запоминающих устройств

- •10.2. Построение модулей памяти микропроцессорных систем

- •11. Элементы микропроцессорной техники

- •11.1. Общие сведения о микроконтроллерах семейства piCmicro

- •1. Ядро микроконтроллера

- •2. Периферийные модули

- •3. Специальные особенности микроконтроллеров

- •Ядро микроконтроллера

- •Порты ввода-вывода

- •Периферийные модули

- •11.2. Примеры применения микроконтроллеров piCmicro

- •11.2.1. Устройство управления четырьмя светодиодами

- •Incf portb, f ; включить крайний справа светодиод

- •11.2.2. Управление жки с помощью последовательного адаптера

- •11.2.3. Аналого-цифровое преобразование

- •11.3. Общие сведения о микроконтроллерах семейства avr

- •Режимы адресации программ и данных.

- •11.4. Примеры применения микроконтроллеров avr

- •11.4.1. Ик дальномер

- •Библиографический список

- •Оглавление

9.4. Комбинационные логические цепи

9.4.1. Основные разновидности комбинационных логических цепей

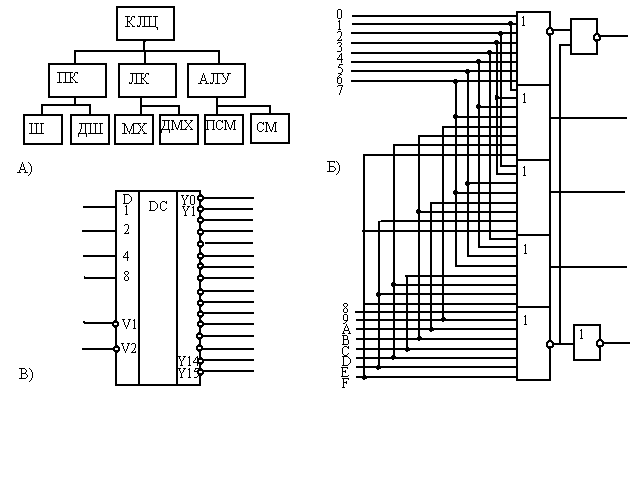

Комбинационные логические цепи (КЛЦ) – это такие цепи, выходные сигналы которых зависят от входных сигналов, действующих в данный момент времени, и не зависят от предыдущего состояния этих цепей. Иначе говоря, КЛЦ – это цепи, в которых отсутствуют ячейки памяти. Основные разновидности КЛЦ можно классифицировать в следующие группы (рис. 9.3а): 1) преобразователи кодов (ПК); 2) логические коммутаторы (ЛК); 3) арифметико-логические устройства (АЛУ). Группу ПК образуют элементы, называемые шифраторами (Ш) и дешифраторами (ДШ), группу ЛК – мультиплексоры (МХ) и демультиплексоры (ДМХ). Основу построения АЛУ составляют полусумматоры (ПСМ) и сумматоры (СМ).

Шифраторами называются КЛЦ, преобразующие М-разрядный код в N-разрядный, причем М > N. Типичным примером является шифратор клавиатуры для ввода в цифровое устройство шестнадцатеричного кода (рис. 9.3б). При ненажатых клавишах на всех входах Ш обеспечивается подача сигнала логического 0. Нажатая клавиша подает на соответствующий вход Ш логическую 1. Шифратор вырабатывает также уведомительный сигнал Х при нажатии любой клавиши. Уравнения, описывающие данную структуру Ш, имеют вид

Y1 = 1 + 3 + 5 + 7 + 9 + B + D + F;

Y2 = 2 + 3 + 6 + 7 + A + B + E + F;

Y4 = 4 + 5 + 6 + 7 + C + D + E + F;

Y 8

= 8 + 9 + A + B + C + D + E + F;

8

= 8 + 9 + A + B + C + D + E + F;

![]() .

.

Д

Рис.

9.3

![]() ;

;

![]() ;

;

![]() ;

;

. . .

![]() ;

;

![]() .

.![]()

При V1 = V2 = 0 ДШ реализует инверсии всех конъюнкций входных переменных, а при остальных наборах V1 и V2 на выходах ДШ будут уровни логической 1.

М

Рис.

9.3

У равнение

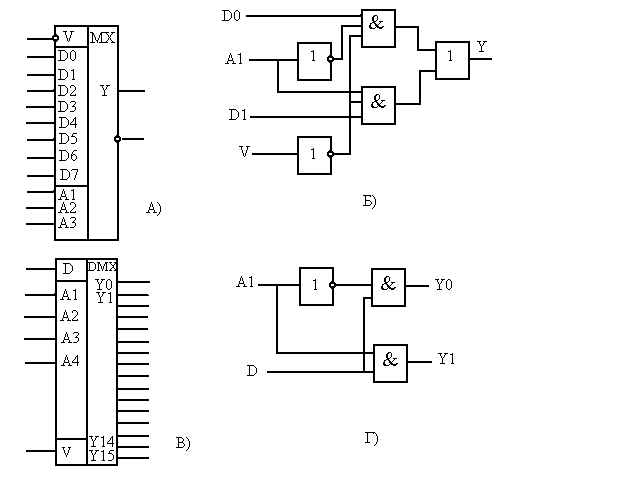

преобразования МХ в этом случае имеет

вид

равнение

преобразования МХ в этом случае имеет

вид

Y

= (AD0

+

![]() D1)

D1)![]() .

.

Рис. 9.4

Вход V используется для стробирования МХ. При подаче логической 1 на этот вход, на выходе МХ устанавливается сигнал логического 0 вне зависимости от наличия каких-либо сигналов на адресных и информационных входах.

Демультиплексор представляет собой КЛЦ, обеспечивающую передачу цифровых сигналов с одного направления на N. На рис. 9.4в показаны функциональное обозначение ДМХ и фрагмент (рис. 9.4г) его внутренней структуры. Логика работы ДМХ такова, что в зависимости от значения сигнала на адресном входе А, входной сигнал D появляется на одном из выходов Y0 или Y1. На основе ДМХ легко реализовать ДШ. Для этого адресные входы надо использовать как информационные (входные), а вход D использовать как вход, поддерживающий выходы в активном состоянии. Подав на D постоянный сигнал и не выводя его наружу, получаем ДШ.

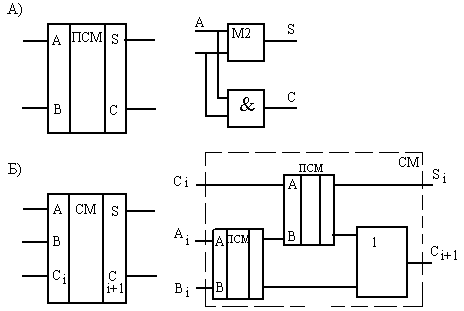

Полусумматор позволяет складывать одноразрядные числа с формированием сигнала переноса в старший разряд. Основу ПСМ составляет схема ИСКЛЮЧАЮЩЕЕ ИЛИ (рис. 9.5а). Сигнал переноса С формируется путем логического умножения значений входных сигналов.

Сумматор используется для реализации операции сложения двух многоразрядных двоичных чисел. СМ можно рассматривать как логическое устройство, имеющее три входа (две цифры слагаемых и цифра переноса из соседнего младшего разряда) и два выхода (значение суммы и перенос в старший разряд).

Рис. 9.5

Структура СМ содержит два полусумматора и схему ИЛИ (рис. 9.5б). Уравнения для суммы и переноса имеют вид

![]() ,

,

![]() .

.