- •Федеральное агентство по образованию

- •1. Основы электрических измерений

- •1.1. Основные понятия и определения

- •1.2. Точностные характеристики средств измерений

- •1.3. Анализ статических погрешностей электронных схем

- •2. Простейшие электронные цепи и методы их анализа

- •2.1. Основные понятия и определения

- •2.2. Применение операторного метода к расчету электрических цепей

- •2.2.1. Прямое преобразование Лапласа

- •2.2.2. Обратное преобразование Лапласа

- •3. Типовые структуры электронных устройств и их свойства

- •3.1. Последовательная структура и ее свойства

- •3.2. Параллельная структура и ее свойства

- •3.3. Встречно-параллельное соединение

- •3.4. Задачи

- •4. Пассивные полупроводниковые компоненты электронных цепей

- •4.1. Полупроводниковые диоды и стабилитроны

- •4.2. Примеры применения полупроводниковых диодов

- •4.3. Светодиоды

- •4.4. Фотодиоды

- •5. Активные полупроводниковые компоненты электронных цепей

- •5.1. Биполярные транзисторы и их применение

- •5.1.1. Структура и принцип действия биполярных транзисторов

- •5.1.2. Характеристики и параметры биполярных транзисторов

- •5.1.3. Обеспечение усилительного режима бт в схемах

- •В результате получаем

- •5.1.4. Малосигнальные эквивалентные схемы и усилительные параметры бт

- •5.1.5. Амплитудно-частотные характеристики бт

- •5.1.6. Элементы транзисторной схемотехники

- •5.2. Полевые транзисторы и их применение

- •5.2.1. Классификация и общие особенности полевых транзисторов

- •5.2.2. Статические характеристики и дифференциальные параметры

- •5.2.3. Способы задания смещения в усилительных каскадах на пт

- •5.2.4. Малосигнальные эквивалентные схемы и усилительные параметры пт

- •5.2.5. Температурная стабильность параметров пт

- •5.2.6. Передаточная функция и динамические свойства пт Инерционные свойства пт описываются передаточной функцией вида

- •5.3. Задачи

- •6. Интегральные микросхемы и их классификация

- •7. Аналоговые интегральные микросхемы и их применение

- •7.1. Операционные усилители и их применение

- •7.1.1. Понятие идеального операционного усилителя

- •7.1.2. Принципы и примеры расчета схем с операционными усилителями

- •7.1.3. Динамические свойства устройств на операционных усилителях

- •7.1.4. Точностные характеристики устройств на операционных усилителях

- •7.1.5. Применение операционных усилителей

- •7.1.6. Задачи

- •7.2. Компараторы

- •7.3. Аналоговые ключи и коммутаторы

- •7.4. Устройства выборки-хранения

- •7.5. Интегральный таймер

- •7.5.1. Задачи

- •7.7. Справочные данные на оу

- •8. Цифро-аналоговые и аналого-цифровые преобразователи

- •8.1. Цифро-аналоговые преобразователи (цап)

- •8.2. Аналого-цифровые преобразователи (ацп)

- •9. Цифровые интегральные микросхемы и их применение

- •9.1. Элементы алгебры логики

- •9.2. Основные типы цифровых имс

- •9.3. Параметры цимс

- •9.4. Комбинационные логические цепи

- •9.4.1. Основные разновидности комбинационных логических цепей

- •9.4.2. Синтез комбинационных логических цепей

- •9.5. Последовательностные логические цепи

- •9.5.1. Классификация последовательностных логических цепей

- •9.5.2. Триггеры

- •9.5.3. Регистры

- •9.5.4. Счетчики импульсов

- •9.6. Применение цифровых имс в импульсных цепях

- •9.7. Задачи

- •10. Микросхемы полупроводниковых запоминающих устройств

- •10.1. Классификация полупроводниковых запоминающих устройств

- •10.2. Построение модулей памяти микропроцессорных систем

- •11. Элементы микропроцессорной техники

- •11.1. Общие сведения о микроконтроллерах семейства piCmicro

- •1. Ядро микроконтроллера

- •2. Периферийные модули

- •3. Специальные особенности микроконтроллеров

- •Ядро микроконтроллера

- •Порты ввода-вывода

- •Периферийные модули

- •11.2. Примеры применения микроконтроллеров piCmicro

- •11.2.1. Устройство управления четырьмя светодиодами

- •Incf portb, f ; включить крайний справа светодиод

- •11.2.2. Управление жки с помощью последовательного адаптера

- •11.2.3. Аналого-цифровое преобразование

- •11.3. Общие сведения о микроконтроллерах семейства avr

- •Режимы адресации программ и данных.

- •11.4. Примеры применения микроконтроллеров avr

- •11.4.1. Ик дальномер

- •Библиографический список

- •Оглавление

9.5. Последовательностные логические цепи

9.5.1. Классификация последовательностных логических цепей

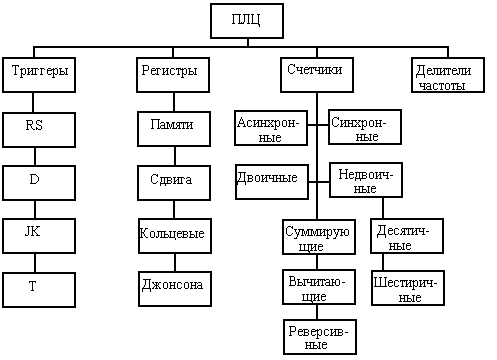

Последовательностными называются логические цепи (ПЛЦ), выходной сигнал которых зависит как от входных сигналов, действующих в данный момент времени, так и от предыдущего состояния этой цепи. В структуре ПЛЦ обязательно имеется элемент памяти, характерным признаком которого является наличие положительной обратной связи с выхода на вход. По функциональному назначению ПЛЦ можно разделить на следующие 4 группы (рис. 9.7): 1) триггеры; 2) регистры; 3) счетчики; 4) делители частоты.

Рис. 9.7

Триггеры – это ПЛЦ, имеющие два устойчивых состояния. В каждом из этих состояний триггер (Тг) может находиться неограниченно долго (пока приложено напряжение питания и отсутствуют информационные сигналы, переводящие Тг из одного состояния в другое).

Основными типами Тг являются: RS-триггеры, D-триггеры, JK-триггеры и Т-триггеры, отличающиеся видом характеристического уравнения, определяющего логику работы. Различают асинхронные (нетактируемые) и синхронные (тактируемые) Тг. Асинхронные Тг переключаются из одного устойчивого состояния в другое сразу после изменения сигналов на его управляющих входах.

Переключение синхронных Тг происходит при наличии разрешающего тактового сигнала на его специальном, тактовом входе. Тактирование может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала).

В первом случае сигналы на управляющих входах оказывают влияние на состояние Тг только при разрешающем потенциале на тактовом входе.

Во втором случае воздействие управляющих сигналов проявляется только в момент перехода единица – ноль или ноль – единица на тактовом входе.

Рис. 9.8

Существуют также универсальные Тг, которые могут работать как в тактируемом, так и нетактируемом режимах. На рис. 9.8а,б показаны временные диаграммы, поясняющие работу RS-триггера соответственно при тактировании уровнем и при тактировании фронтом. Здесь символами S, R, C, Q обозначены соответственно вход установки в 1 (S), вход установки в 0 (R), тактовый вход (С) и прямой выход (Q) Тг. Стрелки на диаграмме С (рис. 9.8б) указывают, что переключение триггера происходит по переднему фронту тактового импульса, т.е. при перепаде из 0 в 1.

Регистры (Рг) – это ПЛЦ, имеющие несколько рабочих состояний и выполняющие функции хранения и преобразования цифровых кодов. В зависимости от назначения Рг можно разделить на регистры памяти (РгП), регистры сдвига (РгС), кольцевые регистры (РгК) и счетчики Джонсона. Основой построения Рг служат синхронные D- и JK-триггеры.

Счетчики (Сч) – это ПЛЦ, число рабочих состояний которых 2k, предназначенные для подсчета количества импульсов, поданных на тактовый вход, и хранения полученного числа в заданном коде. В зависимости от способа тактирования Сч делятся на асинхронные и синхронные.

В синхронных Сч тактовые входы всех триггеров подключаются к одной точке, куда и подаются входные тактовые импульсы.

В асинхронном Сч тактовые входы триггеров подключаются к выходам триггеров более младших разрядов, в результате чего переход Сч из одного устойчивого состояния в другое происходит за более длительное, по сравнению с синхронным Сч, время. Однако асинхронные Сч имеют более простую схему управления.

Основным параметром Сч является коэффициент пересчета М (модуль счетчика), который показывает, сколько импульсов надо подать на тактовый вход, чтобы Сч, находясь в исходном состоянии, прошел все рабочие состояния и вернулся в исходное. По значению этого параметра Сч делятся на двоичные и недвоичные.

Двоичные Сч (ДВСч) имеют максимально возможное число рабочих состояний, равное 2k. Коэффициент пересчета недвоичных Сч (НДВСч) определяется формулой М < 2k. Наиболее часто на практике применяются НДВСч с коэффициентами пересчета 10 – десятичные Сч (ДСч) и 6 – шестиричные Сч. Сч могут работать не только в режиме суммирования количества импульсов, подаваемых на их тактовый вход, но и в режиме вычитания, при котором число, записанное в Сч, уменьшается на единицу при поступлении на тактовый вход одного импульса. Такие Сч называются вычитающими.

Существуют микросхемы Сч, которые могут работать как в режиме суммирования, так и в режиме вычитания. Это так называемые реверсивные Сч (РСч).