832 |

App. A Introduction to SPICE |

where C0 denotes the value for zero voltage across the junction, and m typically falls in the range of 0.3 to 0.4. Thus for Cj and Cjsw, we specify

(cjo, mj)

and

(cjswo, mjsw)

A more complete MOS model may therefore appear as:

.model mymod nmos (level=1, uo=360, tox=0.4n, vth=0.5, lambda=0.4, +cjo=3e-4, mj=0.35, cjswo=40n, mjswo=0.3)

where the “level” denotes a certain complexity for the model. In practice, higher levels with many more parameters are used. Similarly, a PMOS model may be constructed as follows:

.model mymod2 pmos (level=1, uo=150, tox=0.4n, vth=-0.55, +lambda=0.5, cjo=3.5e-4, mj=0.35, cjswo=35n, mjswo=0.3)

A.4 Other Elements and Commands

A.4.1 Dependent Sources

In addition to the independent voltage and current sources studied above, we may need to incorporate dependent sources in simulations. For example, as mentioned in Chapter 8, op amps can be viewed as voltage-dependent voltage sources. Similarly, a MOSFET acts as a voltage-dependent current source.

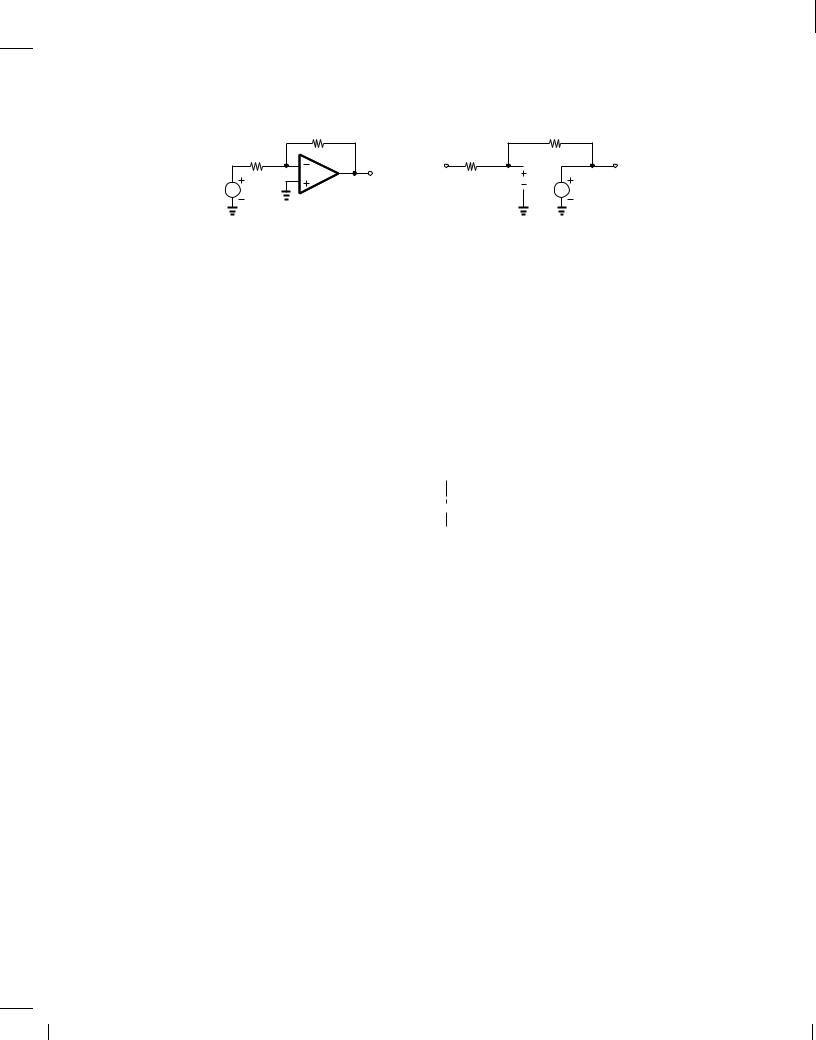

Consider the arrangement shown in Fig. A.18, where the voltage source tied between nodes C and D is equal to three times the voltage difference between nodes A and B. For simplicity,

A

C

C

3VAB

B

D

D

Figure A.18 Voltage-dependent voltage source.

we call (A; B) the “input nodes,” (C; D) the “output nodes,” and the factor of 3, the “gain.” Such a voltage-dependent voltage source is expressed as

Output |

Input |

DC |

Gain |

Nodes |

Nodes |

Value |

|

e1 c d poly(1) |

a b |

0 |

3 |

Note the element name begins with the letter “e” to signify a voltage-dependent voltage source. The next two entries are the output nodes, with the first representing the positive terminal. The entry poly(1) indicates a first-order polynomial relationship between VCD and VAB. Next, the controlling (input) nodes are specified, and the zero is entered to denote a zero additional dc voltage. Finally, the gain is specified. In a more general case, this expression can realize VCD =+ VAB, where is the dc value (zero in the above example) and is the gain (3 in the above example).

Example A.13

C

C

C

C

D

D

C

C

D

D