6. ЛАБОРАТОРНАЯ РАБОТА N 6.

"ПЕРЕДАЧА/ПРИЕМ ЧЕРЕЗ ПАРАЛЛЕЛЬНЫЙ ПОРТ".

Теория.

Теоретический раздел этой работы повторяет в основном сведения, приведенные в теоретическом разделе работы N 1 ("Параллельный порт") . БИС программируемого параллельного интерфейса (ППИ) КР580ВВ55 предназначена для организации ввода/вывода параллельной информации различного формата для сопряжения микропроцессора со стандартным периферийным оборудованием.

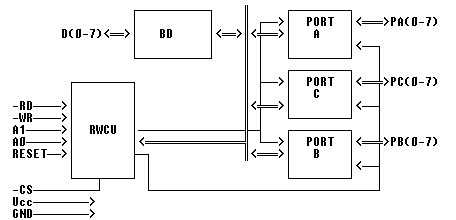

Структурная схема ППИ приведена на рис.1. В состав БИС входят:

д вунаправленный

8-разрядный буфер данных (ВD) , связывающий

ППИ с системной шиной

вунаправленный

8-разрядный буфер данных (ВD) , связывающий

ППИ с системной шиной

данных; блок управления записью/чтением (RWCU) ; три 8-разрядных канала ввода/вывода (PORT A, B и C) .

Рис.1. Структурная схема КР580ВВ55

Назначение входных, выходных и управляющих сигналов ППИ приведены при описании выводов БИС в табл.1. Сигналы управления работой ППИ подаются на блок RWCU (рис.1) и вместе с адресными входами АО, А1 задают вид операции, выполняемой БИС (табл.2) .

Таблица 1. Описание выводов ППИ

|

Обозначение вывода |

Назначение вывода |

|

D (0-7) |

Вход/выход шины данных (разряды 0...7) |

|

-RD |

Чтение; L-уровень сигнала разрешает считывание информации |

|

|

из регистра, адресуемого по входам АО, А1 на шину D (0-7) . |

|

-WR |

Запись; L-уровень сигнала разрешает запись информации с |

|

|

шины D (0-7) в регистр ППИ, адресуемый по входам АО, A1 |

|

A0, A1 |

Входы для адресации внутренних регистров ППИ. |

|

RESET |

Сброс; H-уровень сигнала обнуляет регистр управляющего |

|

|

слова и устанавливает все порты в режим ввода. |

|

-CS

|

Выбор микросхемы: L-уровень сигнала подключает ППИ к системной шине. Обычно этот вход подключается к выходу дешифратора устройств ввода/вывода. |

|

PA (0-7) |

Вход/выход канала A. |

|

PB (0-7) |

Вход/выход канала B. |

|

PC (0-7) |

Вход/выход канала C. |

|

Ucc |

Напряжение питания (+5 в) |

|

GND |

Напряжение питания (0 в) |

Таблица 2. Операции, задаваемые управляющими сигналами ППИ.

|

Операции

|

Сигналы управления |

||||

|

CS |

RD |

WR |

A1 |

A0 |

|

|

Запись управляющего слова |

0 |

1 |

0 |

1 |

1 |

|

Запись в канал А |

0 |

1 |

0 |

0 |

0 |

|

Запись в канал В |

0 |

1 |

0 |

0 |

1 |

|

Запись в канал С |

0 |

1 |

0 |

1 |

0 |

|

Чтение из канала А |

0 |

0 |

1 |

0 |

0 |

|

Чтение из канала В |

0 |

0 |

1 |

0 |

1 |

|

Чтение из канала С |

0 |

0 |

1 |

1 |

0 |

|

Отключение ППИ от D (0-7) |

0 |

1 |

1 |

X |

X |

|

// |

1 |

Х |

Х |

Х |

Х |

Х - безразличное состояние сигнала

Режим работы каждого из каналов ППИ программируется с помощью управляющего слова, задающего один из трех режимов: основной режим ввода/вывода (режим 0) , стробируемый ввод/вывод (режим 1) , режим двунаправленной передачи информации (режим 2) . Одним управляющим словом можно установить различные режимы работы для каждого из каналов. Формат управляющего слова представлен в табл.3.

Канал А может работать в любом из трех режимов, канал В в режимах 0 и 1. Канал С может быть использован для передачи только в режиме 0, а в остальных режимах он служит для передачи управляющих сигналов, сопровождающих процесс обмена по каналам А и В. Разряд D7 управляющего слова (табл.3) определяет либо установку режимов работы каналов (D7 = 1) , либо работу ППИ в режиме сброса/установки отдельных разрядов канала С (D7 = 0) . При D7 = 0 разряды D3-D1 определяют номер модифицируемого разряда канала С, а разряд D0 задает либо сброс (D0 =0) , либо установку (D0 =1) модифицируемого разряда; разряды D6-D4 не используются.

Таблица 3. Формат управляющего слова ППИ

|

Разряды |

Записанная цифра |

Функциональное назначение |

|

DО |

1/0 |

Ввод/вывод PC (3-0) |

|

D1 |

1/0 |

Ввод/вывод PB (7-0) |

|

D2 |

0/1 |

Режимы 0/1 для портов группы В |

|

D3 |

1/0 |

Ввод/вывод РС (7-4) |

|

D4 |

1/0 |

Ввод/вывод РА (7-0) |

|

D6, D5 |

00/01/10 |

Режимы 0/1/2 для портов группы А |

|

D7

|

1/0

|

Установка режимов работы каналов либо работа ППИ в режиме сброса/установки отдельных раз рядов канала С. |

Режим 0 применяется при синхронном обмене или при программной организации асинхронного обмена. Микросхема может рассматриваться в этом режиме как устройство, состоящее из четырех портов (два 8-разрядных и два 4-разрядных) , независимо настраиваемых на ввод или вывод. Вывод информации осуществляется по команде OUT микропроцессора с фиксацией выводимой информации в регистрах каналов, а ввод по команде IN без запоминания информации.

Режим 1 обеспечивает стробируемый однонаправленный обмен информацией с внешним устройством. Передача данных производится по каналам А и В, а линии канала С управляют передачей. Работу канала в режиме 1 сопровождают три управляющих сигнала. Если один из каналов запрограммировать на режим 1, то остальные тринадцать интерфейсных линий можно использовать в режиме 0. Если оба канала запрограммированы на режим 1, то оставшиеся две интерфейсные линии канала С могут быть настроены на ввод или вывод.

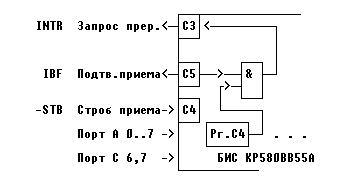

В режиме 1 для ввода информации используются следующие управляющие сигналы: строб приема по каналу А (-STBа = PC4) входной сигнал, формируемый внешним устройством, указывает на готовность ВУ к вводу информации; подтверждение приема в канал А (IBFа = PC5) выходной сигнал ППИ, сообщающий ВУ об окончании приема данных в канал, формируется по спаду -STBа; запрос прерывания от канала А (INTRа = PC3) выходной сигнал ППИ, информирующий микропроцессор (МП) о завершении приема информации в канале: Н уровень сигнала устанавливается при -STB = 1, IBF = 1 и INTE = 1 (внутренний сигнал ППИ INTE разрешение прерываний устанавливается битом D4 для канала А и битом D2 для канала В при записи управляющего слова) ; сбрасывается INTR спадом сигнала -RD. Для канала В соответствие сигналов управления разрядам порта С следующее: -STBb = PC2; IBFb = PC1; INTRb = PC0.

Рассмотрим более подробно работу в режиме 1 при приеме данных через канал А. Для этого может оказаться полезным рис.2, на которой показыны цепи прохождения сигналов.

Рис.2.

Сигнал IBF формируется внутри микросхемы при появлении низкого уровня сигнала -STB. Если при этом на внутреннем регистре С в разряде 4 установлен в 1 бит С4, то на выходе схемы "И" сформируется сигнал высокого уровня, который можно использовать как сигнал запроса на прерывание микропроцессора для приема очередного байта, поступившего на входы порта А. При этом бит С4 выполняет функцию маскирования прерывания (при нулевом состоянии С4 сигнал INTR не формируется) . Для установки отдельных битов внутреннего регистра С удобно использовать специальное управляющее слово для канала С, имеющее следующую структуру:

Бит D7 = 0 (признак специального слова режима для канала С)

Биты D6... D4 не используются

Биты D3... D1 номер устанавливаемого бита в двоичном коде

Бит D0 = 1 при установке разряда D3... D1 в единицу и 0 при установке разряда с номером D3... D1 в ноль.

Для получения информации о появлении сигналов IBF и INTR после загрузки режима 1 для чтения по каналам А и В достаточно прочитать слово состояния порта С (то есть выполнить операцию чтения содержимого порта С) и выделить соответствующие разряды. Структура слова-состояния в режиме 1 ввода через порты А и В следующая:

Бит D7 ввод/вывод через разряд С7 порта С.

Бит D6 ввод/вывод через разряд С6 порта С.

Бит D5 = IBF для канала А.

Бит D4 = INTE для канала А.

Бит D3 = INTR для канала А.

Бит D2 = INTE для канала В.

Бит D1 = IBF для канала В.

Бит D0 = INTR для канала В.

Чтение портов ввода А и В очищает биты запросов на прерывания INTRa и INTRb в разрядах D3 и D0 слова состояния порта С.

Для вывода информации в режиме 1 используются следующие управляющие сигналы: строб записи (-OBFа, b) -выходной сигнал, указывающий ВУ о готовности к выводу, формируется по фронту -WR; подтверждение записи (-АСКa, b) входной сигнал от ВУ, подтверждающий прием информации из ППИ; запрос прерывания (INTRa, b) выходной сигнал ППИ, информирующий МП о завершении операции вывода информации; Н уровень сигнала устанавливается по фронту сигнала -АСК при -OBF = 1 и INTE = 1 (INTE устанавливается при записи управляющего слова битом D6 для канала А и битом D2 для канала В) ; сбрасывается INTR спадом сигнала -WR. Соответствие управляющих сигналов выводам порта С следующее: -OBFa = PC7, -OBFb = PC1; -ACKa = PC6, -ACKb = PC2, INTRa = PC3, INTRb = PC0.

Режим 2 обеспечивает двунаправленную передачу информации по каналу А к ВУ и обратно. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям С7-С3. Оставшиеся одиннадцать интерфейсных линий могут настраиваться на режим 0 или режим 1. Распределение сигналов по интерфейсным линиям порта С следующее: INTRa = PC3; -STBa = PC4; IBFa = PC5; -ACKa = PC6, -OBFa = PC7. Функции управляющих сигналов аналогичны рассмотренным выше сигналам для режима 1. Управление установкой внутреннего сигнала INTE для операции ввода осуществляется по линии С4, а для операции вывода по линии С6.

Основные электрические параметры микросхемы КР580ВВ55 следующие:

выходное напряжение логического нуля Uol, B.....< 0, 4

выходное напряжение логической единицы Uoh, B...> 2, 4

ток потребления от источника питания Icc.mA ....< 60

ток утечки каналов А, B, C, D при невыбранном

режиме Iioz, mkA..........................-100, ..., 100

ток утечки на управляющих входах Iil, mkA.. -10, ..., 10