- •Резонансный усилительный каскад по схеме с общим эмиттером.

- •Транзисторный каскад с общим эмиттером (эмиттерный повторитель)

- •Практические схемы эмиттерных повторителей

- •Выходные каскады.

- •Усилители постоянного тока

- •Интегральные микросхемы операционных усилителей и их применение

- •1. Инвертирующий усилитель.

- •Неинвертирующий усилитель

- •Основные характеристики и параметры интегральных микросхем оу.

- •Коррекция частотных характеристик оу. Приведение лачх к стандартному виду.

- •Схемы с частотно-зависимыми цепями обратной связи.

- •Активные rc-фильтры на основе операционных усилителей.

- •Разработка схем активных фильтров по заданным требованиям к их лачх

- •Схемы для выполнения алгебраических операций.

- •Генераторы на операционных усилителях.

- •Генераторы импульсных сигналов.

- •Генераторы линейно изменяющегося напряжения.

- •Применение операционных усилителей в схемах логической обработки аналоговых сигналов.

- •Схемы аналоговой обработки радиосигналов.

- •Схемы фазовой автоподстройки частоты (фапч) и их применение.

- •1. При (режим биений)

- •Схемотехника функциональных устройств схемы фапч.

- •Применение систем фапч.

- •Источники электропитания от сети переменного тока

Генераторы линейно изменяющегося напряжения.

Генераторы линейно изменяющихся

напряжений (ГЛИН) применяются в различных

устройствах аналоговой техники и

предназначены вырабатывать сигналы,

характерной особенностью которых

является наличие временного интервала,

в пределах которого выходное напряжение

изменяется по закону линейной функции,

т.е. линейно нарастает или линейно

убывает. В большинстве случаев при

создании схем ГЛИН используется принцип

заряда конденсатора, а основу

соответствующих схем на ОУ составляет

интегратор. Принцип построения схемы

ГЛИН на основе интегратора основан на

сочетании интегратора на ОУ с генератором

прямоугольных импульсов, который также

может быть выполнен на основе ОУ. Схема

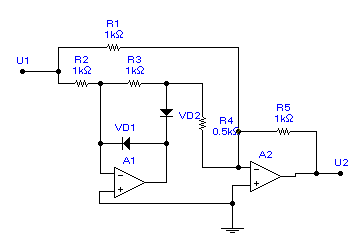

имеет вид, показанный ниже. Как видно,

она состоит из интегратора с цепью

отрицательной обратной связи в виде

зарядно-разрядной цепи R1C1, на вход

которого подключен генератор прямоугольных

импульсов, вырабатывающий напряжение

U1. Напряжение U2 на выходе интегратора

имеет пилообразную форму с крутизной

нарастания и спада, численно равной

![]() ,

где

,

где

![]() -амплитуда

входного сигнала , что иллюстрируется

соответствующим графиком.

-амплитуда

входного сигнала , что иллюстрируется

соответствующим графиком.

Для получения сигнала с различными длительностями участков нарастания и убывания напряжения используются схемы, в которых постоянная времени интегратора автоматически изменяется при смене полярности входного сигнала. Примером такой схемы является следующая.

Данная схема состоит из интегратора на операционном усилителе А1 и компаратора на операционном усилителе А2. Выходное напряжение компаратора поступает через резистор R3 на последовательно включенные стабилитроны D2 и D3, которые обеспечивают ограничение напряжения как положительной, так и отрицательной полярности на заданном уровне, формируя таким образом входной сигнал интегратора. Как видно из схемы, входной сигнал интегратора в зависимости от его полярности проходит или через резистор R1 (отрицательная полярность), или через оба резистора R1 и R2 (положительная полярность). За счет этого положительный фронт сигнала на выходе интегратора имеет большую длительность, чем отрицательный. Переключения компаратора происходят в моменты времени, когда напряжение положительной обратной связи компаратора на резисторе R4 уравновешивается напряжением на выходе интегратора U2. График временной диаграммы для данной схемы приведен ниже.

Применение операционных усилителей в схемах логической обработки аналоговых сигналов.

В качестве характерных примеров такой обработки рассмотрим задачи выделения максимального и минимального из двух одновременно действующих аналоговых сигналов. Для решения таких и подобных задач используются формулы непрерывной логики, аналогичные формулам дискретной (двоичной) логики, но имеющие другие определения. В отличие от двоичной логики, где переменные и их функции могут принимать только одно из двух дискретных значений (0 или 1), в непрерывной логике переменные и функции могут принимать любые значения в диапазоне [-1,0,1] или [0,1], т.е. в пределах от максимального до минимального значений аналогового сигнала.

Для непрерывной логики используются следующие функции:

Дизъюнкция (ИЛИ):

![]() .

.

Реализуется по формуле:

![]() .

.

Конъюнкция (И):

![]() .

.

Реализуется по формуле:

![]() .

.

Инверсия (НЕ):

![]()

Реализуется:

1.

![]()

2.

![]() ,

,

![]() .

.

Как видно, реализация функций дизъюнкции и конъюнкции требует выполнения над аналоговыми сигналами операций сложения, вычитания и выделения абсолютной величины (модуля). Первые две операции выполняются с помощью схем сумматора и усилителя разности. Рассмотрим возможные варианты построения схем для выделения абсолютной величины сигнала. В приведенной ниже схеме R1=R2=R3.

Предположим, что на вход схемы поступает сигнал в виде синусоиды. Тогда во время положительного полупериода диод VD1 закрыт, сигнал через диод VD3 поступает на неинвертирующй вход ОУ и передается на выход с коэффициентом передачи равным единице, поскольку за счет запирания диода VD1 усилитель работает в режим повторителя напряжения.

В отрицательный полупериод диод VD3 закрыт и усилитель работает, как инвертирующий с коэффициентом передачи равным -1. Недостатком схемы является недостаточная точность из-за влияния нелинейности вольт-амперных характеристик диодов и различия коэффициентов усиления ОУ по инвертирующему и неивертирующему входам. Более точной является схема на двух ОУ.

При положительной полуволне на входе на резистор R4 поступает сигнал отрицательной полярности, он усиливается усилителем А2 с коэффициентом усиления равным -R5/R4=-2. Как видно из схемы, усилитель А2 является сумматором сигналов, поступающих на резисторы R1 и R4. С учетом различия полярностей и коэффициентов передачи этих сигналов выходной сигнал оказывается равным входному. При отрицательной полуволне на входе усилитель А1 не участвует в формировании выходного сигнала т.к. диод D2 оказывается закрытым, а D1 открытым, поэтому на выходе А2 отрицательная полуволна превращается в положительную. Временная диаграмма работы схемы имеет вид:

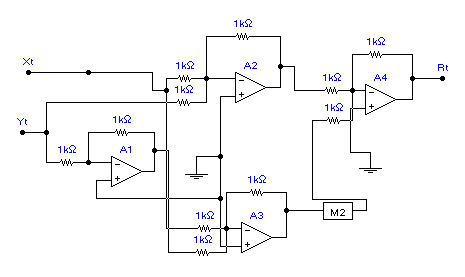

Пример реализации схемы селекции максимального (минимального) сигнала приведен ниже. Как видно из схемы, в ее состав входят инвертор А1, инвертирующие сумматоры А2, А3, А4 и схема выделения абсолютной величины сигнала, обозначенная М2. В зависимости от фазы (0 или 180градусов) одного из сигналов схема выделяет текущие значения сигналов Xt или Yt, как показано на соответствующих временных диаграммах.

Временные диаграммы работы имеют вид:

Выделение большего сигнала

Выделение меньшего сигнала