- •Стандартні розміри системних плат

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Контрольні запитання

- •Практична робота №4 Опис найпростіших логічних схем на мові vhdl. Тріггери. Регістри. Лічильники.

- •Теоретичні відомості.

- •Variable список змінних;

- •Завдання до практичної роботи

- •Практична робота №5 Опис найпростіших логічних схем на мові vhdl. Мультиплексори, суматори, помножувачі.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №6 Побудова схем з пам'яттю. Ramb, srl, rom, fifo.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №7 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №8 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

Variable список змінних;

begin

опис залежності вихідних сигналів від вхідних

end process;

end им’я_архітектури;

Ключове слово «process» означає опис паралельного процесу (обробки наших вхідних сигналів для отримання вихідних), який активується «списком запуску».

ВАЖЛИВО! Всі логічні блоки описані як процес виконуються паралельно один одному!

Список сигналів - це перелік сигналів, зміна яких активує виконання процесу.

У нас лічильник працює по передньому фронту сигналу c_in. Значить нам треба контролювати зміну цього сигналу і при виявленні переднього фронту активувати лічильник.

Запишемо це на VHDL:

architecture count of counter is

begin

process (c_in, res_c)

variable cnt:integer range 0 to 65535;

begin

if (res_c='0') then --якщо низький рівень Reset – скидаємо лічильник

cnt:=0;

elsif (c_in'event and c_in='1') then -- якщо передній фронт - рахуємо

if (enab_c='1') then cnt:=cnt+1;

end if;

end if;

c_out<=cnt;

end process;

end count;

Запис if (c_in'event and c_in = '1 ') then виконує функцію детектора переднього фронту сигналу. Ключове слово event це стандартний атрибут сигналу c_in, який визначає зміна сигналу. Кожен сигнал в проекті має стандартний набір атрибутів. Дослівно наш запис можна прочитати так: якщо c_in змінився і при цьому дорівнює 1. Решта коду процесу працює як і в інших мовах програмування. Хіба що варто звернути увагу на запис c_out <= cnt; який призначає вихідному сигналу c_out значення змінної cnt

Всі попередні кроки - це була підготовча робота. Залишився останній крок.

Крок 5. Опис архітектури всього пристрою:

Опис архітектури всього пристрою істотно відрізняється по структурі від опису архітектури елемента, хоча проводиться так само за допомогою ключового слова «architecture»

У нашому прикладі ця частина виглядає так:

architecture a of one_element is

component counter

port (

c_in,enab_c,res_c:in bit;

c_out:out integer range 0 to 65535

);

end component;

begin

mc: counter

port map (c_in=>main_clk, enab_c=>enab, res_c=>res, c_out=>counter_out);

end a;

Як ви могли помітити у нас з'явилася нова конструкція component. Дана конструкція говорить про те, що елемент counter є компонентом, що входить до складу one_element, і містить опис вхідних та вихідних портів цього компонента.

Далі в операторних дужках begin - end йде найважливіше: призначення вхідних і вихідних сигналів пристрою екземплярам компонентів, що входять в даний пристрій.

Ця частина запису рівносильна з'єднанню логічних елементів провідниками. Так як у нас в проекті тільки один лічильник - то саме йому ми і призначаємо всі наші вхідні і вихідні сигнали.

mc - це ім'я екземпляра лічильника.

port map - це команда призначення вхідних і вихідних сигналів даному лічильнику.

Підсумковий код, який у нас вийшов виглядає так:

library IEEE;

use IEEE.std_logic_1164.all;

entity one_element

port (

main_clk, res, enab : in bit;

counter_out : out integer range 0 to 65535

);

end one_element;

entity counter is

port (

c_in,enab_c,res_c:in bit;

c_out:out integer range 0 to 65535

);

end counter;

architecture count of counter is

begin

process (c_in, res_c)

variable cnt:integer range 0 to 65535;

begin

if (res_c='0') then

cnt:=0;

elsif (c_in'event and c_in='1') then

if (enab_c='1') then cnt:=cnt+1;

end if;

end if;

c_out<=cnt;

end process;

end count;

architecture a of one_element is

component counter

port (

c_in,enab_c,res_c:in bit;

c_out:out integer range 0 to 65535

);

end component;

begin

mc: counter

port map (c_in=>main_clk, enab_c=>enab, res_c=>res, c_out=>counter_out);

end a;

Лічильник готовий.

Для опису тригерних схем в VHDL використовуються оператори wait і if разом з процесом, що використовує атрибути переднього або заднього фронтів синхроімпульсу. Нижче наведені приклади створення описів спрацьовування по фронту:

(Clk'event and clk = '1 ') - атрибут спрацьовування по передньому фронту;

(Clk'event and clk = '0 ') - атрибут спрацьовування по задньому фронту;

rising_edge (clock) - виклик функції по передньому фронту;

falling_edge (clock) - виклик функції по задньому фронту;

У цих прикладах ілюструється застосування атрибута переднього фронту (rising edge 'event attribute). Використання атрибутів слід рекомендувати в тих випадках, коли система проектування не підтримує виклик функції за подією. Однак, використання функцій дозволяє уникнути колізій, пов'язаних з переходом з невизначеного стану, оскільки функція визначає тільки переходи рівнів (з 0 в 1 або з 1 в 0), не не перехід з невизначеного стану в 1 або 0. Це стає досить важливим у випадку використання багатозначних типів даних, наприклад std_logic, який має 9 можливих значень (U, X, 0, 1, Z, W, L, H, -).

Далі розглянемо основні типи тригерів.

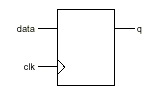

Тригери, тактовані переднім фронтом (Rising Edge Flip-Flop) (рис. 4.2.)

Рис. 4.2 Структура тригера, тактованого переднім фронтом.

Опис на VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity dff is

port (

data, clk : in std_logic;

q :out std_logic);

end dff;

architecture behav of dff is

begin

process (clk) begin

if (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

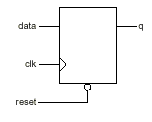

Тригери, тактовані переднім фронтом з асинхронним скиданням (Rising Edge Flip-Flop with Asynchronous Reset) (рис. 4.3)

Рис. 4.3 Структура тригера, тактованого переднім фронтом з асинхронним скиданням.

Приклад опису на VHDL.

library IEEE;

use IEEE.std_logic_1164. all;

entity dff_async_rst is

port

(data, clk, reset: in std_logic;

q: out std_logic);

end dff_async_rst;

architecture behav of dff_async_rst is

begin

process (clk, reset) begin

if (reset = '0 ') then

q <= '0 ';

elsif (clk'event and clk = '1 ') then

q <= data;

end if;

end proces s;

end behav;

Тригери, тактовані переднім фронтом з асинхронною передустановкою (Rising Edge Filp-Flop with Asynchronous Preset) (рис. 4.4).

Рис. 4.4. Структура тригера, тактованого переднім фронтом з асинхронною передустановкою.

Опис на VHDL

library IEEE;

use IEEE.std_logic_1164. all;

entity dff_async_pre is

port

(data, clk, preset: in std_logic;

q: out std_logic);

end dff_async_pre;

architecture behav of dff_async_pre is

begin

process (clk, preset) begin

if (preset = '0 ') then

q <= '1 ';

elsif (clk'event and clk = '1 ') then

q <= data;

end if;

end process;

end behav;

Тригери, тактовані переднім фронтом з синхронним скиданням (Rising Edge Filp-Flop with Synchronous Reset) (рис. 4.5).

Рис. 4.5. Структура тригера, тактованого переднім фронтом з синхронним скиданням.

Опис на VHDL

library IEEE;

use IEEE.std_logic_1164. al l;

entity dff_sync_rst is

port

(data, clk, reset: in std_logic;

q: out std_logic);

end dff_sync_rst;

architecture behav of dff_sync_rst is

begin

process (clk) begin

if (clk'event and clk = '1 ') then

if (reset = '0 ') then

q <= '0 ';

else q <= data;

end if;

end if;

end process;

end behav;

Тригери, тактовані переднім фронтом з синхронною передустановки (Rising Edge Filp-Flop with Synchronous Preset) (рис. 4.6).

Рис. 4.6. Структура тригера, тактованого переднім фронтом з синхронною передустановкою.

Опис на VHDL

library IEEE;

use IEEE.std_logic_1164. al l;

entity dff_sync_pre is

port

(data, clk, preset: in std_logic;

q: out std_logic);

end dff_sync_pre;

architecture behav of dff_sync_pre is

begin

process (clk) begin

if (clk'event and clk = '1 ') then

if (preset = '0 ') then

q <= '1 ';

else q <= data;

end if;

end іf;

end process;

end behav;

Тригери, тактовані переднім фронтом з асинхронним скиданням і дозволом тактового сигналу (Rising Edge Filp-Flop with Asynchronous Reset and Clock Enable) (рис. 4.7).

Рис. 4.7. Структура тригера, тактованого переднім фронтом з асинхронним скиданням та дозволом тактового сигналу.

Опис на VHDL

library IEEE;

use IEEE.std_logic_1164. al l;

entity dff_ck_en is

port

(data, clk, reset, en: in std_logic;

q: out std_logic);

end dff_ck_en;

architecture behav of dff_ck_en is

begin

process (clk, reset) begin

if (reset = '0 ') then

q <= '0 ';

elsif (clk'event and clk = '1 ') then

if (en = '1 ') then

q <= data;

end if;

end if;

end process;

end behav;