- •Тема 11. Основные схемы цифровых устройств

- •11.1. Цифровая электроника и булева алгебра

- •11.2. Основные правила булевой алгебры

- •11.3. Комбинационные схемы

- •11.4. Базовые схемы

- •11.5. Триггеры

- •11.6. Синхронизируемые триггеры

- •11.7. Триггеры с двухступенчатым запоминанием

- •11.8. Триггеры с т-входом, jk-триггеры

- •11.9. Регистры

- •11.10. Схемы преобразования и коммутации

- •11.11. Сумматоры

- •11.12. Тристабильные схемы

- •11.13. Общая шина

- •11.14. Цифро-аналоговые преобразователи

- •11.15. Аналого-цифровые преобразователи

11.10. Схемы преобразования и коммутации

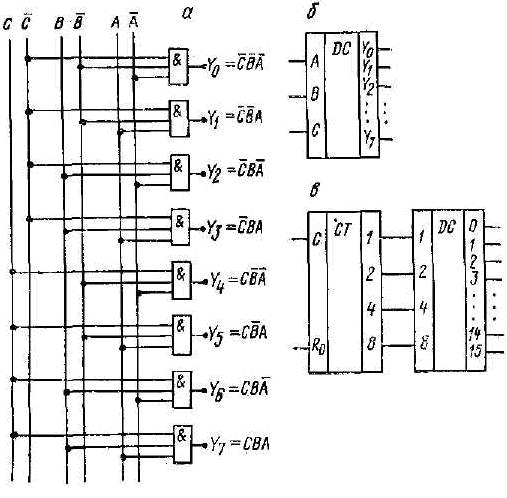

Дешифратор (рис. 11.28) служит для распознавания кодовых комбинаций. Если двоичный дешифратор имеет k входов, то число возможных комбинаций сигналов на входах равно числу k-разрядных двоичных чисел, т. е. 2k поэтому полный двоичный дешифратор имеет 2k выходов. В простейшем случае синтез дешифратора сводится к построению набора из 2k комбинационных схем, имеющих k общих входов. На практике для построения дешифраторов применяются способы, позволяющие более экономно расходовать электронные компоненты.

Рис. 11.28. Дешифратор: структура (а), обозначение (б) и пример применения для индикации состояния счетчика (в)

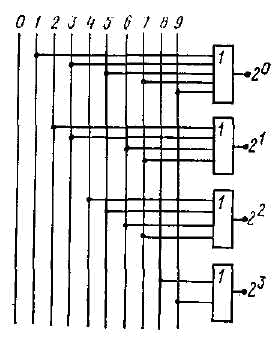

Шифраторы преобразуют цифры, задаваемые сигналом «1» на индивидуальных шинах, в параллельный код. Устройство преобразования десятичных цифр в двоичный код приведено на рис. 11.29. Конструирование подобного рода шифраторов сводится фактически к представлению цифр в виде суммы чисел, каждое из которых равно 2k, где k=0,1,2,...

Рис. 11.29. Структурная схема шифратора

Преобразователи кодов. Принцип синтеза комбинационных схем может быть положен в основу преобразования кодов. Поясним это примером. Пусть требуется преобразовать чисто двоичный код 8-4-2-1 в код 2-4-2-1. Для этого составляют таблицу (рис. 11.30а), в которой каждой комбинации в коде 8-4-2-1 (D1C1B1A1) ставится в соответствие комбинация D2С2В2А2 в коде 2-4-2-1. Такую таблицу можно рассматривать как набор четырех таблиц для определения переключательных функций D2,С2,В2 и А2, аргументами (которых являются D1C1B1 и A1 .Нереализуемые комбинации могут считаться или «0» или «1» из соображений удобства минимизации. Все фазы синтеза преобразователя приведены на рис. 11.30.

Рис. 11.30. Синтез преобразователя кода 8-4-2-1 в код 2-4-2-1: таблица состояний (а); карты минимизации (б); итоговая схема (в)

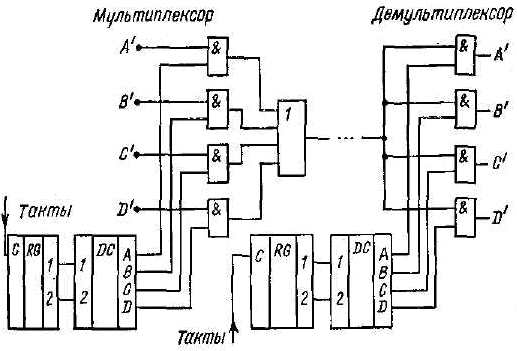

М ультиплексным

называют канал передачи информации, в

котором одни и те же шины служат для

передачи сигналов от различных источников

(рис. 11.31). На передающем конце к линии

через схемы И поочередно подключаются

выходы триггеров А/, В/, С/

и D/. Разрешающий подключение

сигнал поступает на схемы И от дешифратора

состояний счетного регистра, поэтому

в любой момент времени гарантируется

подключение к линии выхода только одного

триггера.

ультиплексным

называют канал передачи информации, в

котором одни и те же шины служат для

передачи сигналов от различных источников

(рис. 11.31). На передающем конце к линии

через схемы И поочередно подключаются

выходы триггеров А/, В/, С/

и D/. Разрешающий подключение

сигнал поступает на схемы И от дешифратора

состояний счетного регистра, поэтому

в любой момент времени гарантируется

подключение к линии выхода только одного

триггера.

Рис. 11.31. Мультиплексный канал передачи информации

Аналогичный счетный регистр и дешифратор на приемном конце линии обеспечивают разделение поступающей информации на четыре канала. На вход обоих счетных регистров подается единый для всей системы сигнал тактовой частоты.

11.11. Сумматоры

Регистры, предназначенные для счета импульсов, выполняют простейшую операцию алгебраического суммирования единицы и содержимого регистра. Более совершенные устройства обработки информации производят все необходимые арифметические и логические действия над кодами.

С умматор

- устройство для суммирования двух

двоичных кодов, занимает особое

положение: с его помощью при должном

выборе способа кодирования можно, в

принципе, производить все четыре

арифметических действия над кодами.

умматор

- устройство для суммирования двух

двоичных кодов, занимает особое

положение: с его помощью при должном

выборе способа кодирования можно, в

принципе, производить все четыре

арифметических действия над кодами.

Рис. 11.32. Структура и таблица состояний логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ (а), полусумматора (б), одноразрядного сумматора (в) и схема многоразрядного комбинационного сумматора (г)

Одноразрядный сумматор, как и любая комбинационная схема, может быть синтезирован по таблице состояний в соответствии с правилами, сформулированными в п. 11.3. Но обычно по этим правилам синтезируют лишь одну схему - СУММАТОР ПО МОДУЛЮ 2, или, что то же самое, ИСКЛЮЧАЮЩЕЕ ИЛИ (рис. 11.32а). Эта схема имеет важное самостоятельное значение, а также входит в качестве составного элемента в схему так называемого полусумматора - устройства, способного суммировать одноразрядные двоичные числа (рис. 11.32б). Сигналы на его выходе имеют название «СУММА» (S) и «ПЕРЕНОС» (Р).

Название «полусумматор» обусловлено тем, что на базе двух таких устройств можно построить одноразрядный сумматор (рис. 11.32в), который наряду с одноразрядными слагаемыми А и В учитывает перенос из младшего разряда Рn-1 и имеет поэтому три входа. Нетрудно заметить, что все входы равнозначны (взаимозаменяемы).

Один из способов построения сумматора многоразрядных чисел, так называемого параллельный комбинационный сумматор, поясняется на рис. 11.32г. Он имеет n-разрядные входы для чисел А и В и (n+1)-разрядный выход для суммы S, так как разрядность суммы не может более, чем на единицу, превышать разрядность большего из слагаемых.

На первом этапе развития электронной вычислительной техники сумматор был тем элементом ЭВМ, при помощи которого выполнялись многие операции над числами. Сейчас он повсеместно вытеснен так называемыми арифметико-логическими устройствами (АЛУ) - интегральными схемами, как правило, четырехразрядными, имеющими входы чисел А, В и кода управления F. В зависимости от кода на входах F над числами А и В могут быть осуществлены различные преобразования, в частном случае - суммирование. Итог появляется на четырехразрядном выходе сигнала результата S и одноразрядном выходе переноса. Несколько АЛУ могут быть объединены для обработки чисел большей разрядности.