- •Министерство образования и науки украины государственное высшее учебное заведение «донецкий нацинальный технический университет»

- •Конспект лекций

- •По дисциплине "Компьютерные системы"

- •1 Мультипроцессорные в с (м п в с)

- •Упрощенная схема мпвс

- •Структурная организация мпвс с общей шиной

- •1.3 Мпвс с перекрестной коммутацией

- •1.4 Мпвс с многовходовыми озу

- •1.5. Характеристики мпвс

- •1.6 Свойства мпвс

- •Выборка команд со сдвигом во времени

- •Выборка широким словом

- •Поточная организация уво

- •2.4 Структура конвейерного процессора

- •Конвейерный процессор для векторной обработки

- •3 Вс с матричной структурой

- •Процессорная матрица (пм) с локальной памятью

- •4. Матричные процессоры

- •5. Ассоциативные вс (авс)

- •6 Систолические массивы

- •7 Однородные системы и среды

- •8 Многопроцессорная система с программируемой архитектурой (мпспа)

- •9 Функционально распределенные вычислительные системы

- •10.1 Структура соо

- •10.2. Сетевые модели соо

- •10.3. Теорема Джексона

- •10.4. Постановка задач синтеза соо

- •10.5. Синтез соо с заданным временем ответа (с заданной производительностью)

- •10.6. Синтез соо с заданной стоимостью

- •11. Планирование работ в вычислительных системах

- •11.1. Планирование по критерию минимума суммарного времени выполнения работ

- •Планирование работ на основе двухфазной модели вс

- •Планирование работ на основе трехфазной модели вс

- •11.1.3. Эвристический алгоритм планирования работ в вс

- •11.2. Планирование работ по критерию максимальной загрузки устройств

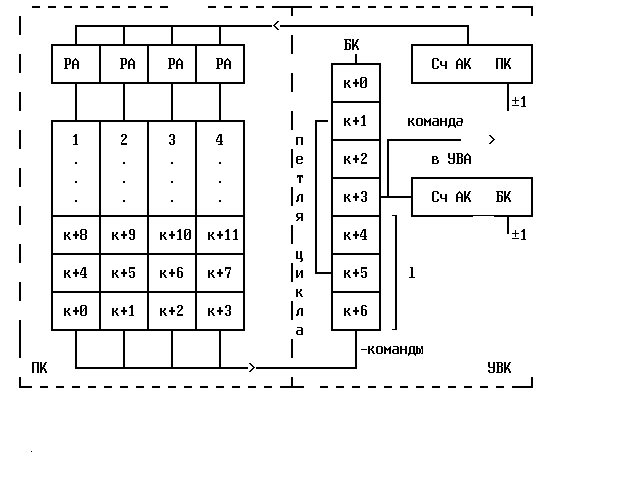

Выборка команд со сдвигом во времени

1-4 это блоки памяти.

l- запас новых команд в БК.

Рис.2.4.

В регистре адреса (РА) блоков памяти 1..4 через каждые t подается новый адрес из счетчика адреса команд СчАК ПК. С таким же сдвигом по времени на выходе ПК будут появляться команды, которые затем поступают в буфер команд (БК), представляющих собой совокупность быстрых регистров. При поступлении каждой новой команды В БК содержимое всех его регистров сдвигается вверх на одну позицию и верхняя команда выбрасывается из БК.

В УВК имеется СчАК БК, который указывает положение в БК считываемой в УВА команды. При считывании из БК каждой команды его содержимое уменьшается на единицу, при добавлении в БК новой команды из ПК - увеличивается на единицу.

Если l становится меньше заданного уровня, то УВК запускает СчАК ПК и производится выборка из ПК новых команд.

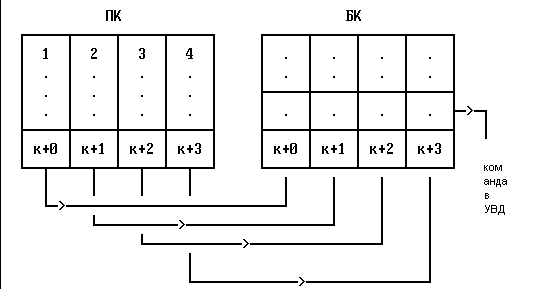

Выборка широким словом

Рис.2.5.

За один цикл памяти в БК заносится несколько команд (широкое слово), операции в БК выполняются также, как и ранее.

Сократить цикл работы УВО можно также использованием многоблочной памяти для уменьшения времени чтения операнда. Однако между выборкой команд и выборкой операндов существует принципиальное различие. Команды в программе и памяти располагаются в порядке линейного нарастания их номеров. Следовательно, во время исполнения текущей команды всегда можно вычислить адреса и выбрать любые следующие команды. Но упорядоченная выборка команд порождает неупорядоченную последовательность адресов для выборки операндов. Это означает, что выборка операндов для некоторой команды не может быть произведена заранее до выборки этой команды. => выборка операндов не может быть конвейеризирована => для построения ПО используется не конвейерный, а поточный принцип организации многоблочной памяти.

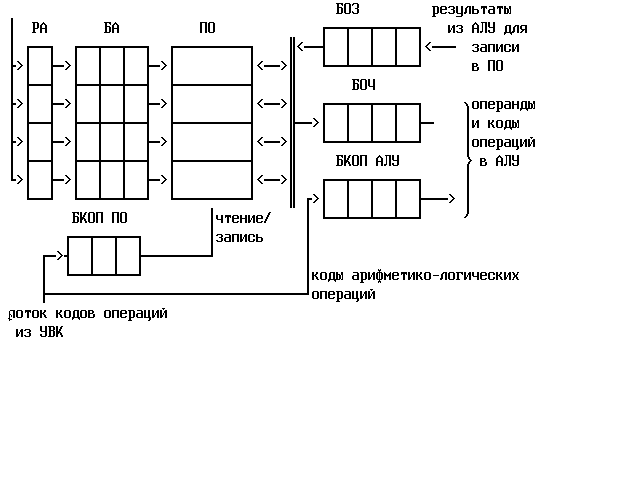

Поточная организация уво

Рис.2.6.

Поступающие из УВА адреса операндов распределяются по блокам ПО. Так как распределение адресов носит случайный характер, в блоках памяти возможны очереди, для размещения которых введены буфера адресов (БА).

Выбираемые из памяти операнды должны сразу поступать в АЛУ, однако в следствии неравномерности их появления из ПО и разной длительности исполнения операций в АЛУ вводятся буферные регистры операндов чтения (БОЧ) и записи (БОЗ).

С каждой парой операндов связан свой код операции, который хранится также в буфере кода операций (БКОП).

Следовательно, в буфере операндов (БО) и БКОП хранятся готовые к исполнению в АЛУ группы информации.

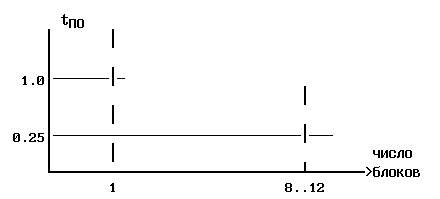

Зависимость цикла выборки одного операнда от количества блоков памяти

Рис.2.7.

Итак, мы изучили структуры отдельных устройств конвейерного процессора.