- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу(проверь дш)

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

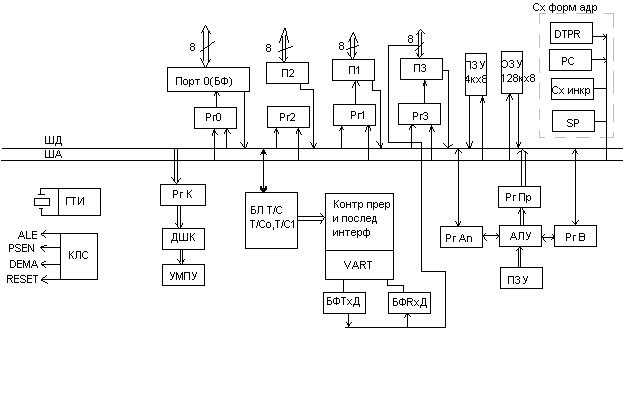

28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

Микроконтроллеры 4 разр. Их прямое назначение:

1)Калькуляторы 2)Пульты ДУ 3)ИК интерфейс.

Intel MCS51

Это контроллер клавиатуры, таймер видеомагнитофонов. 8051 n-МОП технология где 0 вид ПЗУ, 0-ПЗУ масочного изг с фиксированной прошивкой. 3-ПЗУ однопрограммируемое ПЗУ(8351) 7-ПЗУ сУльтрафиол стиранием(30-50раз) 9-Flash память (1000-10000 перепрогр).

8х31- где 31-внутреннего ПЗУ нет, есть возможность подкл внешн ПЗУ.

8хС51 где С – КМОП технология 20мА.

Наиболее популярна МС89С51.

Контроллер имеет 4 || универсальных 8-разр порта, каждый из которых имеет альтернативную функцию. Кристалл гарвардского типа: память команд и данных раздельна. При обращении к данным использ Рг DTPR встроенное ОЗУ-128b ПЗУ-4kb. Имеется возм подкл внешнего ПЗУ 64kb и ОЗУ 64kb. Проц имеет 111 команд включая команды * и /. Есть возможность побитной установки и обработки разрядов портов и флагов. В проце содерж 32 РОНа. Они делятся на 4 банка и карта адреса выглядит след образом: в спец Рг задается какой банк РОНов работает.

RS0-RS1 указывает на номер банка.

80Н-порт 0

equ-порт 0=80Н обращение к ячейке 80Н

89Н ТМОD – установка режима таймера.

Блок таймеров содержит 2 16-ти разр многофукц таймера (0-3 режима). ГТИ: 12MHz за 12 тактов 1 команда в режиме таймера.

Контр прерыв и послед инткрф обр 5 разл прерываний (2 внешних, 2тиаймера и послед интерф). Посл интерф работает в полудуплексном реж-ме и поддерж стандарт протоколы обмена типа RS. Порт 0 исп-ся для ввода вывода байта(как обычный Рг +ШФ), в альтернативном реж-ме порт 0 обеспечивает формирование младшего байта адр и прием данных пр подкл внешн ОЗУ и ПЗУ. Порт 2 то же самое сто и порт 0 но при подкл внешн ОЗУ и ПЗУ формир старш байт адр. Порт 1 вв/выв 8 сигналов, альтернатив нет. Порт 3 каждый бит имеет альтернативную функцию. Dip40- 40 ножек. Альтернативные функции: TxD,RxD –сигнал послед-го интерфейса. T/C0,T/C1-сигналы таймера, сч-ка; RD,WR –чтение/запись при обращении к внеш. памяти данных или внеш. ОЗУ; INT0, INT1- прерыв. по внеш событиям; ALE-строб адреса, по сигналу ALE происходит защелкивание адреса (порта 0) во внешний Рг при обращении в внешн памяти прогр или данных. PSEN- сигнал чтения из внешн памяти прогр. DEMA- 0-блокировка внутр ПЗУ,работа в внешт ПЗУ, 1-наоборот.

Протокол обмена подкл ОЗУ/ПЗУ MCS-51:

Обращение к внешней памяти данных (ОЗУ)

В протоколе обмена нет сигнала RDY (сигнал готовности для особо тупых), тактов ожидания, режима ПДП.

Обращение к внешней памяти прогр. (ПЗУ)

Обращение к внешней ПЗУ идет в 2 раза быстрее. При обращении к внешн памяти команд. на ША (Р0 Р2) выставл РС и считывание инф промсходит в 2 раза быстрее чем обращение к ОЗУ.

Подкл к СМ.

ATmega 32:

8-разр RISC процессор с полным набором систмн команд (131 команда), включает операции * и /. Тактовая частота 16МГц, производительность 16млн опер. Опер умнож на число <1 -2 такта , остальные операции 1 такт.

Фирма совмещает 3 технологии на 1 кристалле:

Выполнен по КМОП технологии и целиком статический (частотаот 0-16МГц, в 0 почти не потребляет энергии). З2 кб флэш-память команд (структура Гарвардская). Флэш допусткает 10000 раз перепрошивку. 2кб-ОЗУ встроенное на кристалле, 32 РОНа.

2кб EEPROM – электрически стираемая и перепрограммируемая память(запись по байтам, допускает 100тыс циклов перепрограм-мирования, и служит как энергонезависимое ОЗУ (при при выкл питания хранит данные)). 10 разр встроенный АЦП (8 канальный). Встроенный аналоговый компаратор( сравнение напряжении япо уровню). 3 таймер-счетчика (2 8-ми разр,1 16-ти разр). 3 последовательных интерфейса UART, SPI, I2C. Встроенный 4 сторожевой таймер со встроенным внутр генератором. Часы реального времени. Встроенный контроллер прерываний. Все это нах-ся в корпусе DIP-40 (32 двунапр линии вв/выв с альтер-нативными функциями

МХ-

мультиплексор

МХ-

мультиплексор

ЧРВ- часы реального времени

WDT- сторожевой таймер

к Пр- контроллер прерываний

T/C –таймер счетчик.(имеют 4 канала ЦАП постр по принципу широко-импульсной модуляции (PSW))

REF- внешнее опорное напряжение для АЦП.