- •Глава III. Организация памяти эвм

- •1. Классификация и параметры запоминающих устройств

- •2. Постоянные и полупостоянные запоминающие устройства

- •3. Оперативные запоминающие устройства

- •4. Характеристики обмена и типы оперативной памяти

- •Озу Nx1 a1... А10 wcasras d0 озу Nx1 a1... А10 wcasras d8 озу Nx1 a1... А10 wcasras d0 ... D7 d8

- •6. Логическая организация памяти

- •7. Сегментация памяти

- •8. Страничная организация памяти

- •9. Озу современных эвм

8. Страничная организация памяти

В P- иV-режимах МП 386 и выше могут поддерживать (с помощью внутреннего менеджера памятиMMUи операционной системы) страничную адресацию. При ней память 4 Гб разбивается на 1 М страниц емкостью по 4 Кб каждая. Тогда физический адрес байта вычисляется как

<ФА (31,0)> = <<АС(19,0)>, < Асм(11,0)>>, где

Ас(19,0) – 20-разрядный адрес страницы, от 0 доFFFFFh(01М-1), который передается в старшие разряды ША(31,12);

Асм(11,0) – 12-разрядный адрес смещения внутри страницы, который передается в младшие разряды шины адреса ША(11,0).

По этой формуле вычисляется виртуальный (virtual– фактический) адрес любого байта данных, размещенных по страницам. Причем номер страницы занимает старшие разряды шины адреса; адреса страниц выровнены по границе, т.е. младшие 12 разрядов номера страницы равны нулю, и поэтому номера новых страниц следуют с шагом 212(4К) в линейном адресном пространстве 4Г. Если программа занимает память под свой код и данные с числом страниц и их номерами, не выходящими за емкость ОЗУ, собранного на ИС, вычисление адреса <АС(19,0)>, <Асм(11,0)> совпадает с обычным способом прямой адресации к физической памяти основного ОЗУ и приводит лишь к снижению быстродействия обмена. В данном случае эффективным будет режим запрета страничного преобразования.

Однако в том случае, если программа работает с виртуальными адресами из верхней области линейного адресного пространства, превышающей емкость ОЗУ, следует:

- размещать информацию по страницам;

- необходимые страницы в процессе работы последовательно переписывать с диска в ОЗУ;

- виртуальные адреса страниц Ас(19,0) преобразовывать в адреса страниц (кадров) реальной физической памяти ОЗУ Ас*(19,0). Преобразование Ас(19,0)Ас*(19,0) может быть осуществлено при помощи косвенной адресации, когда каждому адресу Ас(19,0) ставится в соответствие адрес ячейки памяти, где хранится Ас*(19,0). Если в 20 разрядах таких ячеек размещать реальный адрес страницы, а в других – дополнительную информацию о странице, то каждый элемент этой таблицы (дескриптор) может занимать 4 байта. Тогда при числе страниц 1М емкость памяти, требуемая под таблицу преобразования, может достигать 4 Мб. В мультизадачной среде таких таблиц может потребоваться несколько. Тогда таблицы сами могут занять всю область ОЗУ, что недопустимо.

В процессорах МП 386 и выше используется более гибкое двухэтапное преобразование Ас(19,0)Ас*(19,0) с помощью таблицPDEиPTEI(I= 01023), которое позволяет намного уменьшить емкость памяти косвенной адресации. Вычисление адреса операнда ФА (31,0) в ОЗУ по линейному адресу ЛА(31,0) осуществляется поэтапно по следующему правилу:

ФА (31,0) = <<PTEI L(31,12)>, <ЛА (11,0)>>, где

PTEIL(31,0) =M1(<PDEI (31,12)>, <ЛА (21,12)>),

PDEI(31,0) =M2(<CR3 (31,12)>, <ЛА (31,22)>)

На первом этапе, как показано на рис. 3.15, в МП извлекается содержимое ячейки памяти М2(дескриптор таблицыPDE), где в 20 старших разрядах хранится базовый адрес таблицыPTEIс физическими адресами страниц. Содержимое М2извлекается из ОЗУ по ШД (31,0) по адресу ША (31,0) = <<CR3 (31,12)>, <ЛA(31,22)>>, где старшие 20 разрядов являются базовым ФА каталога базовых адресов таблиц страницPDEи располагаются в регистреCR3, а 10 младших разрядов ЛА (31,22) определяют смещениеIв каталоге. Базовый ФА <CR3 (31,12)> таблицыPDEзаносится в регистрPDBRоперационной системой при включении режима страничного преобразования. Он не изменяется при решении задач.

Рис. 3.15. Схема вычисления ФА при страничной адресации

На втором этапе содержимое 20 старших разрядов М2 используется при определении базового адреса таблицы <PTEI(31,0)>, которое передается в старшие разряды ША, а к 10 младшим разрядам ША подключается содержимое <ЛА 21,12>. По этому ФА извлекается элементPTEIL(L-й дескриптор таблицыPTEI). ЭлементPTEILявляется ячейкой М1, где в 20 старших разрядах хранится ФА страницы А*С(19,0). Для извлечения операнда из ОЗУ в старшие разряды ША подается физический адрес страницы <А*С(19,0)> = <PTEIL(31,12)>, а в младшие – смещение внутри страницы <АСМ (11,0)> = <ЛА (11,0)>.

Смещение внутри страницы не подвержено преобразованию, и 12 его разрядов используются для определения ФА данных или кода внутри страничного кадра подключаясь к 12 разрядам внутренней шины адреса ША(11,0).

Дескрипторы таблиц PDEиPTEимеют одинаковую структуру вида:

|

31 12 |

9 |

|

|

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

ФА страничного кадра |

Дос |

0 |

0 |

D |

A |

PCD |

PWT |

U/S |

R/W |

P |

Разряды этих дескрипторов имеют следующее назначение:

- P– бит присутствия, приP= 1 страница загружена в ОЗУ;

- R/W– бит чтения/записи, приR/W= 1 страница допускает операции чтение/запись, а приR/W= 0 – только чтение;

- U/S– пользователь/супервизор. ПриU/S= 0 страница с привилегиями супервизора, а приU/S= 1 – уровень пользователя;

- PWT– запрет сквозной записи страницы. ПриPWT= 1 осуществляется сквозная запись, а приPWT= 0 – способ с обратной записью;

- PCD– запрет кэширования страницы. ПриPCD= 1 кэширование страницы запрещено, в остальных случаях – кэширование по циклам;

- A– бит обращения.Aустанавливается в 1, когда МП обращается к странице для записи/считывания;

- D–Dirty(грязный) бит. При записи новых данных в страницуDOSустанавливает его в 1;

- Дос при страничной организации не используется, программно доступен;

- ФА – 20-битное поле физического адреса таблицы PTEили страничного кадра задачи.

При преобразовании линейного адреса в ФА МП проверяет в первую очередь бит P, еслиP= 0, то осуществляется свопинг (загрузка с НЖМД нужной страницы в ОЗУ) в следующей последовательности:

- освобождение одного из страничных кадров ОЗУ и, при D= 1, пересылка его на диск;

- DOSкопирует нужную страницу в ОЗУ с диска в страничный кадр, начиная с ФА освободившейся памяти в 4 Кб;

- загрузка 20-битного адреса ФА в соответствующий дескриптор PTEи установка в немP= 1, а также, при необходимости, установка/сброс остальных флагов;

- перезагрузка буфера TLB;

- рестарт команды, инициировавшей свопинг.

К преимуществам страничной адресации относится возможность использования всей области линейного пространства.

К недостаткам можно отнести:

- обмен страницами, которые могут быть не полностью заполнены информацией;

- снижение производительности из-за свопинга и операций преобразования адреса;

- сложность контроля со стороны пользователя за динамическим распределением памяти;

- потеря части ОЗУ на размещение таблиц PDEиPTE.

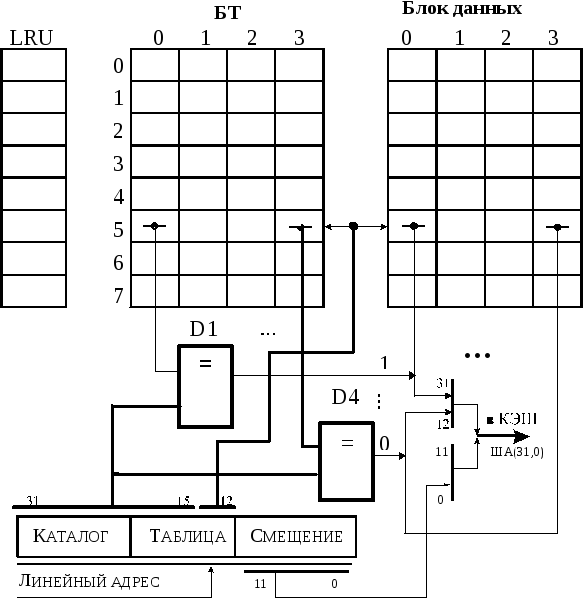

Двухэтапное преобразование уменьшает быстродействие вычисления адреса из-за дополнительного обмена с ОЗУ, и поэтому для повышения производительности используется ассоциативный буфер преобразования(TLB). Для того чтобы уменьшить время вычисления адреса страничного кадра Ас*(19,0) при страничной адресации, необходимые элементы таблицPDEиPTEразмещают в ассоциативном КЭШ-буфере преобразования (TLB), который хранит часть нужных дескрипторов и уменьшает число обращений к ОЗУ. На рис. 3.16 представлена структура буфераTLB, используемого устройством страничного преобразованияi486. Он по содержанию и принципу работы имеет много общего с внутренним кэш. Блок данныхTLB, состоящий из 4 множеств по 8 строк, емкостью по 20 бит каждое множество, используется для хранения физических адресов страничных кадров, которые заносятся непосредственно из ОЗУ при каждой загрузкеPDBR. БлокLRUопределяет, какие физические адреса (строки) можно заменить на новые при отсутствии их вTLB. 21-битные строки блоков тэгов (БТ) используются для хранения 17 старших разрядов виртуального адреса Ас (19,3), 3 бит атрибутов Ат и 1 битаVдостоверности строки. Строки БТ имеют вид:

-

20

16 3 0

V

AT

Ac (19,3)

Разряды строк с (20, 17) используются блоком LRU. Разряды (16,0) множеств 0,1,2,3 БТ коммутируются на соответствующую множеству схему сравненияD1, ...,D4.

Схемы D1D4 сравнивают старшие разряды ЛА (31,15) с разрядами (16,0) каждой из строк направлений 0, 1, 2, 3 БТ, возбужденных в результате дешифрации кода <ЛА(14,12)>. Так, если этот код равен <1, 0, 1>, то пятая строка множеств с направлениями 0, 1, 2, 3 блока тэгов передается на входы своих схемD1D4. На другие входы этих схем подается тэг с разрядов (31,15) линейного адреса. При срабатывании одной из схем сравнения от множеств коммутируется соответствующая строка из блока данных на шину адреса. На рис. 3.16 показано:D1 имеет выход1и коммутирует строку 5 направления 0 из блока данных на ША (31,12).

.

Рис. 3.16. Структура буфера TLB

Если при сравнении D1D4 не срабатывают, то вTLBотсутствует Ас*(19,0) и, используя алгоритм псевдо -LRU, аналогично механизму внутреннего кэш, осуществляется чтение таблицPDEиPTEиз ОЗУ и замена данных в блоке данных и БТ.

Для проверки TLBмогут использоваться два регистраTR6 иTR7 - при наиболее привилегированном уровне. Структура регистров представлена на рис. 3.17. Регистр данныхTR7 «отображается» на блок адресовTLBи имеет следующие поля:

-

31

11

0

Физический адрес

PCD

PWT

LRU

0 0

PL

REP

0 0

TR7

Линейный адрес

V

D*

U*

W*

0

0 0 0

C

TR6

Рис. 3.17. Формат регистров проверки TLB

- TR7(31,12) – физический адрес, который передается (считывается) со строки в соответствии сTR6 (31,12);

- PCD,PWT– значения этих битов соответствуют битам дескриптораPDE;

- LRU– при считывании – битыB0,B1,B2LRU;

- REP– при записи определяет направление. При считывании, еслиPL= 1, определяет срабатываниеD1D4 по коду направления; приPL= 0, содержимоеREPне определено;

- PL– бит промаха (PL= 0) или попадания (PL= 1) при поиске. При записи иPL= 1 подключается направление, указанное вREP, а приPL= 0 направление определяетLRU.

Регистр TR6 является регистром команды со следующим назначением разрядов:

- TR6 (31,12) – линейный адрес Ас (19,0) и тэг, передаваемый в БТ;

- С – бит команды. При С = 0 запись, иначе – поиск или считывание;

- D* – битDи его дополнение;

- U* – битU/Sи его дополнение;

- W* – битR/Wи его дополнение;

- V– достоверность, при отсутствии загрузки строки БТV= 0, при записи в строкуV= 1.

Состояния двух разрядов любого поля D*,U*,W*устанавливаются в соответствии с табл. 3.3 и имеют значение в зависимости от режима поиска или записи.

Таблица 3.3

Назначение наборов полей D*,U*,W*

|

D*,U*,W* |

Поиск |

Запись |

|

0 0 0 1 1 0 1 1 |

Не сравнивать Сравнивать, если бит 0 Сравнивать, если бит 1 Сравнивать всегда |

Не определено Сбросить бит Установить бит Не определено |