- •Глава III. Организация памяти эвм

- •1. Классификация и параметры запоминающих устройств

- •2. Постоянные и полупостоянные запоминающие устройства

- •3. Оперативные запоминающие устройства

- •4. Характеристики обмена и типы оперативной памяти

- •Озу Nx1 a1... А10 wcasras d0 озу Nx1 a1... А10 wcasras d8 озу Nx1 a1... А10 wcasras d0 ... D7 d8

- •6. Логическая организация памяти

- •7. Сегментация памяти

- •8. Страничная организация памяти

- •9. Озу современных эвм

3. Оперативные запоминающие устройства

Для построения ОЗУ большой емкости используются элементы статической или динамической памяти, которые строятся на простейших элементах транзисторно-транзисторной логики (ТТЛ), инжекционной логики (И2Л), эмиттерносвязной логики (ЭСЛ) и других технологий [5].

В основе динамических ОЗУ (DRAM) используется заряд межэлектродных конденсаторов Cijемкостью менее 0.1 пФ и током заряда менее 10-10А. Схемаi-го разряда ячейки памяти динамического ОЗУ (DRAM) представлена на рис. 3.3. Для записи логической “1” в элемент памяти активизируются информационная шинаDjи адресная шинаАi. При этом униполярный (полевой) транзистор открывается и через него конденсаторCijзаряжается. При отсутствии открывающего напряжения на шинеАiтранзистор закрыт, конденсаторCijзаряжен и хранит информацию. При подаче напряжения чтения на шинуАiтранзисторVTijоткрывается и напряжение конденсатораCijподается на шинуDj, и он разряжается. Ток разрядаCijусиливается и фиксируется в информационном регистре ОЗУ.

Dj VTij Cij Ai

Рис. 3.3. Элемент динамического ОЗУ

Для устранения искажений информации в результате утечки заряда с конденсатора элементы памяти периодически, через 2 мс или более, в зависимости от типа ИС, необходимо перезаряжать в цикле регенерации. Преимуществом динамических ОЗУ является высокая степень интеграции элементов памяти и малая потребляемая мощность. Недостатком их является большое время доступа 50-70 нс по сравнению со статической памятью, где оно равно менее 15 нс.

Статическая оперативная память (SRAM)

строится на быстродействующих биполярных

транзисторах, например, двухэмиттерных

транзисторах TTL (рис. 3.4). В режиме хранения

информации между шинами АxиАyподдерживается

минимальное напряжение (около 0.2 В),

сохраняя один из транзисторов открытым

(логический “0”), другой закрытым

(логическая “1”). На обоих проводах

информационной парафазной шины (![]() )

устанавливается положительное напряжение,

которое обеспечивает нулевой ток через

эмиттеры Э2. Элемент памяти (ЭП)

находится в пассивном режиме хранения

информации с наименьшим уровнем

потребления энергии.

)

устанавливается положительное напряжение,

которое обеспечивает нулевой ток через

эмиттеры Э2. Элемент памяти (ЭП)

находится в пассивном режиме хранения

информации с наименьшим уровнем

потребления энергии.

Рис. 3.4. Элемент статического ОЗУ

В режиме чтения информации шины АxиАyвозбуждаются и на них подаются потенциалы, обеспечивающие быстрое чтение разных токов, поступающих с эмиттеров Э2на провода в усилитель чтения. В зависимости от величины токов в проводах, после их усиления триггер Т2(см. рис. 3.5,а) информационного регистра ОЗУ устанавливается в “1” или “0”. При этом состояние ЭП не изменяется и он может быть переведен в режим хранения предыдущего состояния.

Для записи информации в бистабильный

ЭП возбуждаются адресные шины АxиАy и соответствующий

один провод![]() или

или![]() под действием управления с усилителя

записи. Противоположный возбужденному

проводу

под действием управления с усилителя

записи. Противоположный возбужденному

проводу![]() (

(![]() )

транзисторVT1(VT2)

открывается, т.к. через его эмиттер Э2протекает больший ток под действием

большей разности потенциалов

)

транзисторVT1(VT2)

открывается, т.к. через его эмиттер Э2протекает больший ток под действием

большей разности потенциалов![]() .

ЭП переходит в устойчивое состояние:VT1открыт, аVT2закрыт.

.

ЭП переходит в устойчивое состояние:VT1открыт, аVT2закрыт.

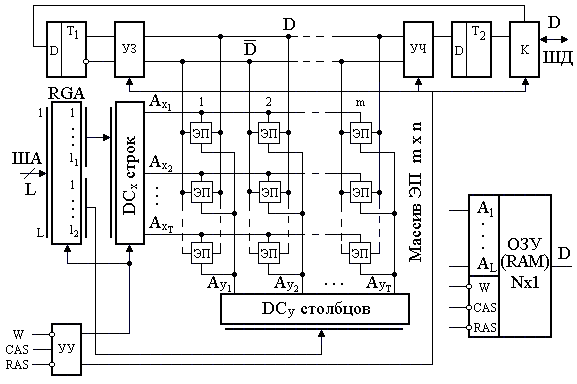

На статических и динамических ЭП изготавливают ИС различной емкости и разрядности. На рис. 3.5, б приведена типичная ИС емкостью

N= 2L=mn(бит).

Массив ЭП состоит из nстрок иmстолбцов. Каждый ЭП хранит один бит информации.

а б

Рис. 3.5. Структура ИС ОЗУ: а – 1- битная схема ОЗУ, б – обобщенная схема ОЗУ

Адрес ЭП, участвующего в операции чтения /записи, определяется L-разрядным двоичным кодом, поступающим с шины адреса ША в регистр адреса RGA. Младшиеl1разряда адреса в режиме чтения или записи информации в ОЗУ с появлением сигнала выборки строки RAS поступают на дешифратор строкDCx. Старшиеl2разряда адреса с появлением сигнала выборки столбца CAS поступают на дешифратор столбцовDCy.

В соответствии с двоичным кодом адреса

каждый из дешифраторов возбуждает

только одну выходную шину. На пересечении

возбужденных шин АxиАyсоответствующий ЭП подключается к

внутренней информационной парафазной

шине

![]() .

.

В режиме записи (W=0, CAS=0, RAS=0) УУ включает

усилитель записи (УЗ) и подсоединяет

его к шине

![]() .

Одновременно к шине

.

Одновременно к шине

![]() дешифраторамиDCx иDCyподключается один ЭП,

который УЗ устанавливается в устойчивое

состояние, задаваемое триггеромТ1.

ТриггерТ1перед началом записи

воспринимает один бит информации через

коммутатор К с внешней шины данных ШД.

дешифраторамиDCx иDCyподключается один ЭП,

который УЗ устанавливается в устойчивое

состояние, задаваемое триггеромТ1.

ТриггерТ1перед началом записи

воспринимает один бит информации через

коммутатор К с внешней шины данных ШД.

В режиме чтения (W=1, RAS=0, CAS=0) УУ отключает

УЗ от шины

![]() и подключает к ней усилитель чтения

(УЧ). Одновременно выход триггераТ2через К подсоединяется к ШД. В соответствии

с кодом адреса усилителем чтения (УЧ)

устанавливается состояние триггераТ2, соответствующее состоянию

возбужденному ЭП дешифраторамиDCx

иDCy. В следующий момент

времени информация с триггераТ2передается на ШД.

и подключает к ней усилитель чтения

(УЧ). Одновременно выход триггераТ2через К подсоединяется к ШД. В соответствии

с кодом адреса усилителем чтения (УЧ)

устанавливается состояние триггераТ2, соответствующее состоянию

возбужденному ЭП дешифраторамиDCx

иDCy. В следующий момент

времени информация с триггераТ2передается на ШД.

При хранении информации (CAS=RAS=1) коммутатор

К отключает от ШД ОЗУ. На всех шинах Аx,Аy,

![]() устанавливаются потенциалы, обеспечивающие

пассивный режим сохранения состояний

ЭП.

устанавливаются потенциалы, обеспечивающие

пассивный режим сохранения состояний

ЭП.