Цилькер Б.Я., Орлов С.А. Организация ЭВМ и систем

.pdf

Контрольные вопросы 5 8 5

Контрольные вопросы

1. Какой уровень параллелизма в обработке информации обеспечивают вычис лительные системы класса SIMD?

2.На какие структуры данных ориентированы средства векторной обработки?

3.Благодаря чему многомерные массивы при обработке можно рассматривать в качестве одномерных векторов?

4.Поясните различие между конвейерными и векторно-конвейерными вычисли тельными системами.

5.Поясните назначение регистров векторного процессора: регистра длины век тора, регистра максимальной длины вектора, регистра вектора индексов и ре гистра маски.

6.Для чего используются операции упаковки/распаковки вектора?

7.Оцените выигрыш в быстродействии векторного процессора за счет сцепления векторов.

8.В чем заключается принципиальное различие между векторными и матричны ми вычислительными системами?

9.Какими средствами обеспечивается подготовка программ для матричных вы числительных систем и их загрузка?

10.По какому принципу в матричной ВС команды программы распределяются между центральным процессором и массивом процессоров?

И.Каким образом в матричной ВС реализуются предложения типа IF-THEN- ELSE?

12.Как идентифицируются отдельные процессорные элементы в массиве процес соров матричной ВС?

13.Какие схемы глобального маскирования применяются в матричных ВС и в ка ких случаях каждая из них является предпочтительной?

14.Могут ли участвовать в вычислениях замаскированные (пассивные) процес сорные элементы матричной ВС и в каким виде это участие проявляется?

15.Поясните различие между ассоциативной памятью и ассоциативным процес сором.

16.В чем выражается аналогия между матричными и ассоциативными ВС?

17.Какую особенность систолической ВС отражает ее название?

18.Объясните достоинства и недостатки систолических массивов типа ULA, BLA, TLA.

19.Сформулируйте правила объединения простых команд в командное слово сверх большой длины.

20.Чем ограничивается количество объединяемых команд в технологии EPIC?

21.Поясните назначение системы предикации и ее реализацию в архитектуре

•IA-64. ,

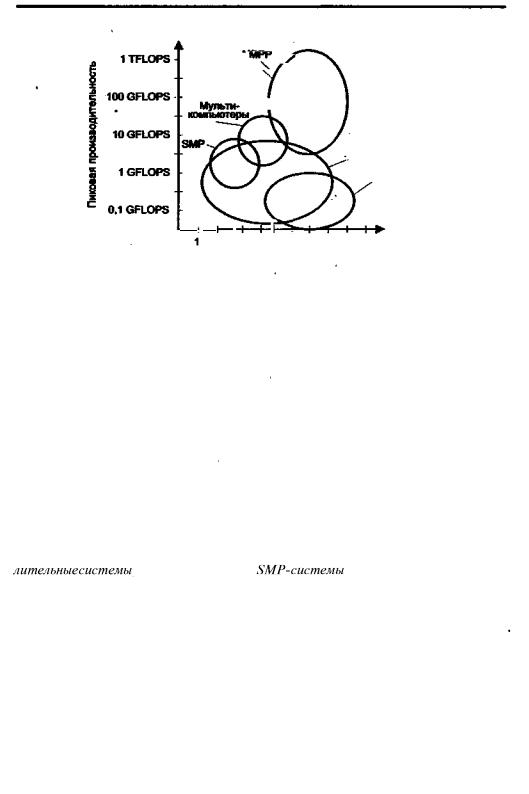

5 9 2 Глава 14. Вычислительные системы класса MIMD

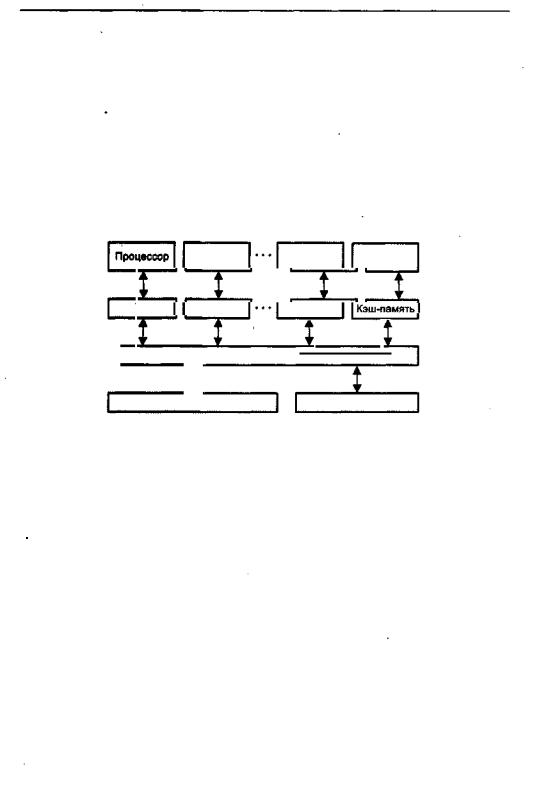

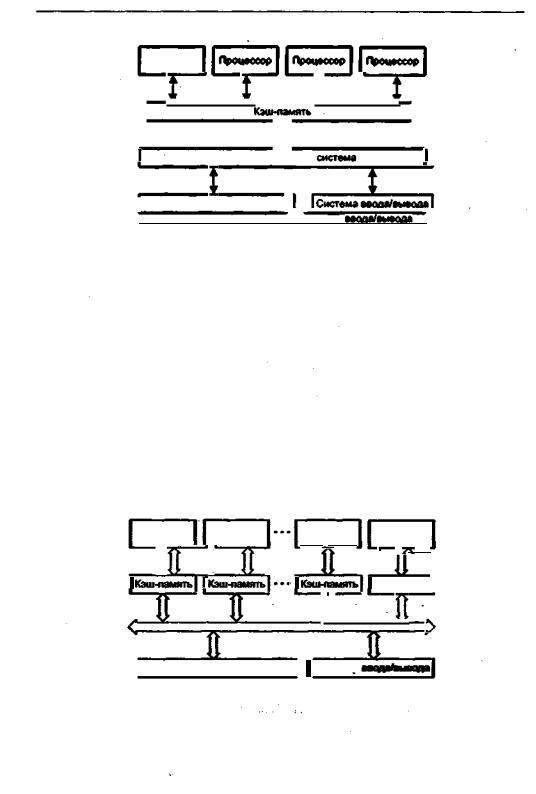

память

память

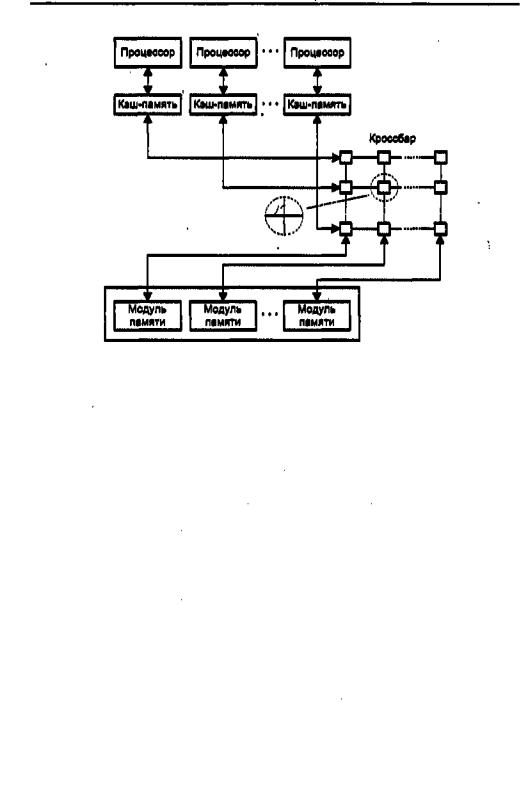

Рис. 14.7. Структура SMP-системы с коммутатором типа «кроссбар»

Коммутатор обеспечивает множественность путей между процессорами и бан ками памяти, причем топология связей может быть как двумерной, так и трехмер ной. Результатом становится более высокая полоса пропускания, что позволяет строить SMP-системы, содержащие больше процессоров, чем в случае общей шины. Типичное число процессоров в SMP-системах на базе матричного коммутатора составляет 32 или 64. Отметим, что выигрыш в производительности достигается, лишь когда разные процессоры обращаются к разным банкам памяти.

По логике кроссбара строится и взаимодействие процессоров с устройствами ввода/вывода.

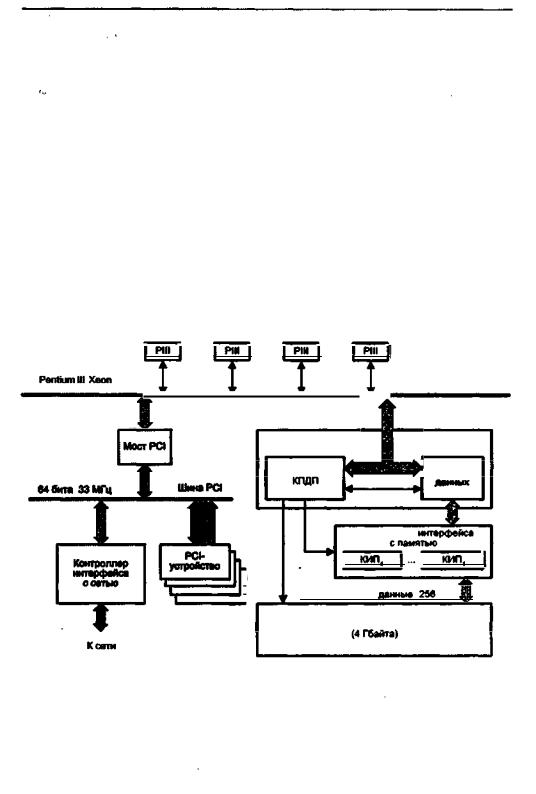

В качестве примера ВС с рассмотренной архитектурой можно привести систе му Enterprise 10000, состоящую из 64 процессоров, связанных с памятью посред ством матричного коммутатора Gigaplane-XB фирмы Sun Microsystems (кроссбар 16 х 16), В IBM RS/6000 Enterprise Server Model S70 коммутатор типа «кроссбар» обеспечивает работу 12 процессоров RS64. В SMP-системах ProLiant 8000 и 8500 фирмы Compaq для объединения с памятью и между собой восьми процессоров Pentium III Хеоп применена комбинация нескольких.шин и кроссбара.

Концепция матричного коммутатора (кроссбара) не ограничивается симмет ричными мультипроцессорами. Аналогичная структура связей применяется для объ единения узлов в ВС типа CC-NUMA и кластерных вычислительных системах.

Архитектура с многопортовой памятью

Многопортовая организация запоминающего устройства обеспечивает любому процессору и модулю ввода/вывода прямой и непосредственный доступ к банкам основной памяти (ОП). Такой подход сложнее, чем при использовании шины,

Кластерные вычислительные системы 5 9 3

поскольку требует придания ЗУ основной памяти дополнительной, достаточно сложной логики. Тем не менее это позволяет поднять производительность, так как каждый процессор имеет выделенный тракт к каждому модулю ОП. Другое преи мущество многопортовой организации — возможность назначить отдельные мо дули памяти в качестве локальной памяти отдельного процессора. Эта особенность позволяет улучшить защиту данных от несанкционированного доступа со сторо ны других процессоров.

Архитектура с централизованным устройством управления

Централизованное устройство управления (ЦУУ) сводит вместе отдельные пото ки данных между независимыми модулями: процессором, памятью, устройствами ввода/вывода. ЦУУ может буферйзировать запросы, выполнять синхронизацию и арбитраж. Оно способно передавать между процессорами информацию о состо янии и управляющие сообщения, а также предупреждать об изменении информа ции в кэшах. Недостаток такой организации заключается в сложности устройства управления, что становится потенциальным узким местом в плане производитель ности. В настоящее время подобная архитектура встречается достаточно редко, но она широко использовалась при создании вычислительных систем на базе машин семейства IBM 370.

Кластерные вычислительные системы

Одно из самых современных направлений в области создания вычислитель ных систем — это кластеризация. По производительности и коэффициенту готовности кластеризация представляет собой альтернативу симметричным мультипроцессорным системам. Понятие кластер определим как группу вза имно соединенных вычислительных систем (узлов), работающих совместно, составляя единый вычислительный ресурс и создавая иллюзию наличия един ственной ВМ. В качестве узла кластера может выступать как однопроцессор ная ВМ, так и ВС типа SMP или МРР. Важно лишь то, что каждый узел в со стоянии функционировать самостоятельно и отдельно от кластера. В плане архитектуры суть кластерных вычислений сводится к объединению несколь ких узлов высокоскоростной сетью. Для описания такого подхода, помимо тер мина «кластерные вычисления», достаточно часто применяют такие названия, как: кластер рабочих станций (workstation cluster), гипервычисления (hypercomputing), параллельные вычисления на базе сети (network-based concurrent computing), ультравычисления (ultracomputing).

Изначально перед кластерами ставились две задачи: достичь большой вычис лительной мощности и обеспечить повышенную надежность ВС. Пионером в об ласти кластерных архитектур считается корпорация DEC, создавшая первый ком мерческий кластер в начале 80-х годов прошлого века.

В качестве узлов кластеров могут использоваться как одинаковые ВС (гомо генные кластеры), так и разные (гетерогенные кластеры). По своей архитектуре кластерная ВС является слабо связанной системой.