- •Микропроцессорные системы мпс (Полетаев Игорь Алексеевич) 4-й курс Iсеместр 2000/2001 гг.

- •Классификация процессоров

- •Классификация контроллеров. Сферы применения 32-разрядных контроллеров

- •Обзор 8-разрядных контроллеров

- •Общая структура контроллеров семейства mCs-51i8x51

- •Структура контроллеров семейства pic16Схх

- •Структура команд и методы адресации

- •Методы адресации в pic-контроллерах

- •Язык Ассемблер

- •Программирование арифметических операций

- •Табличные вычисления

- •Порты ввода-вывода

- •Таймер-счётчик

- •Последовательный интерфейс mCs51

- •Работа последовательного порта в мультиконтроллерных системах

- •Определение тактовой частоты при работе с последовательным портом

- •Интерфейсы контроллеров pic

- •Последовательный связной интерфейс

- •Структурная схема приёмника

- •Модуль прерываниёMCs51

- •Система прерываний pic16

- •16-Ти разрядные контроллеры на примере mCs96

- •Вопросы

Программирование арифметических операций

При сложении и вычитании проблем не возникает, только надо учитывать бит переноса. При наличии команды умножения произведение получается аналогично умножению в столбик (умножается байт на байт).

Пример:

Принципы программирования умножения на примере без знаковых чисел при отсутствии аппаратных команд:

Множимое

![]() ,

множитель

,

множитель![]() .

.

Сумма kпервых или последних частичных произведений – этоk-ая сумма частичных произведений. Приk=nполучаем полное произведение. Длина произведения есть сумма длин множимого и множителя.

Алгоритм:

анализируется очередной бит

множителя;

множителя;в зависимости от его значения происходит прибавление множимого к предыдущей сумме частичных произведений;

производится изменение взаимного положения множимого Х и суммы частичных произведений с учётом веса

.

.

В соответствии с выражением (1) существует 4 возможных варианта умножения, зависящих от того, с каких разрядов множителя начинается умножение и что сдвигается: множимое или сумма частичных произведений.

11.10.2000

В kразрядности выше 8 существуют отдельные команды для знакового и беззнакового умножения:

MUL (unsigned MULtiplication);

IMUL (sIgned MULtiplication).

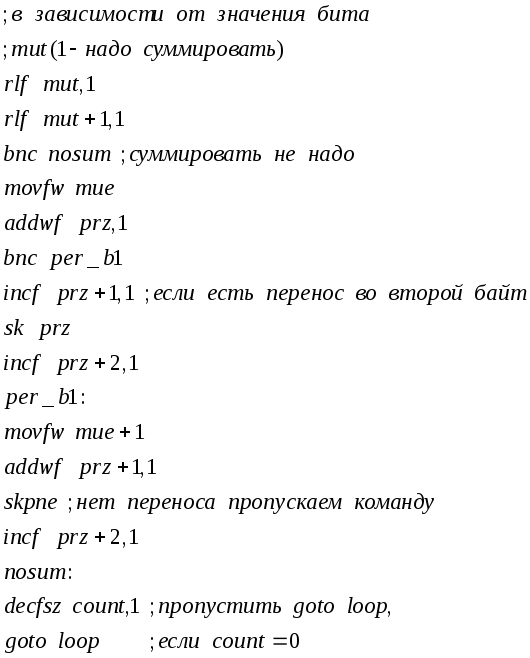

Сдвиг суммы частичных произведений старшими разрядами вперёд (для PIC):

Операция

целочисленного деления является обратной

по отношению к умножению. Принято, как

дополнительный результат, формировать

остаток

![]() .

Рассмотрим две разновидности деления:

делимое, делитель и частное имеют одну

длину; делимое имеет двойную длину по

сравнению с делителем и частным (возможно

переполнение, когда старшая половина

делимого больше делителя). Деление

сводится к последовательности вычитаний

делителя из делимого, а затем из остатка.

Тогда

.

Рассмотрим две разновидности деления:

делимое, делитель и частное имеют одну

длину; делимое имеет двойную длину по

сравнению с делителем и частным (возможно

переполнение, когда старшая половина

делимого больше делителя). Деление

сводится к последовательности вычитаний

делителя из делимого, а затем из остатка.

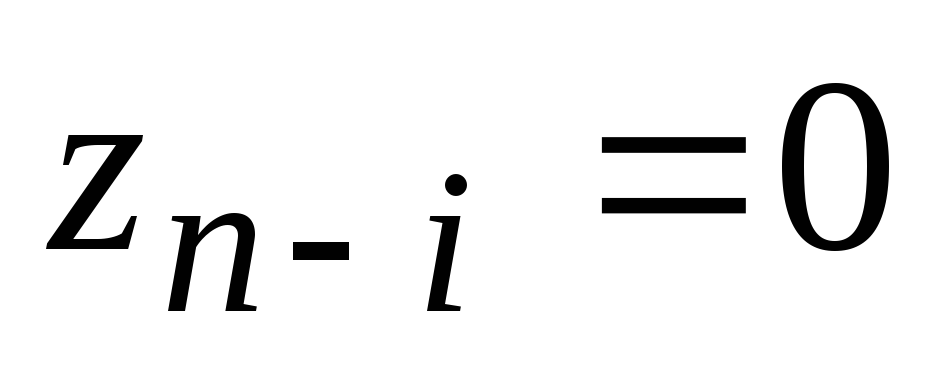

Тогда![]() частного определяется так: если текущий

остаток

частного определяется так: если текущий

остаток![]() делителю – цифра

частного 1 иначе 0.

делителю – цифра

частного 1 иначе 0.

анализ некорректной ситуации;

начальный остаток

равен делимому;

равен делимому;вычитание делителя из остатка

и образование остатка

и образование остатка ;

;если

,

то

,

то и необходимо вернуться к

и необходимо вернуться к ,

если

,

если ,

то

,

то и за очередной остаток принимается

и за очередной остаток принимается ;

;коррекция взаимного положения остатка и делителя (переход к 3 или на конец алгоритма).

Частное определяется со сдвигом делителя вправо или со сдвигом остатка (делимого) влево.

![]()

![]()

![]()

![]()

![]()

Т.к. вычитание (сравнение) происходит побайтно, то необходимо выровнять границы старших байт. При этом младший разряд может быть потерян. Для частного и остатка необходимо иметь по 2 байта. Чтобы частное побитно замещало Х, можно справа добавить один байт, условно считая его младше младшего.

![]()

![]()

0000rrrr

rrrrrrrr rrrrrrrr r0000000

![]()

![]()

![]()

![]()

Затем в каждом цикле будут сравниваться старшие два байта остатка с делителем. В зависимости от результата в самый младший бит сдвигом будет записываться 0 или 1.

000000rr

чччччччч 000000zz zzzzzzzz

![]()

![]()

![]()

![]()

![]()

![]()

000000цц

цццццццц

Программная

реализация зависит от того, как

возвращаются к

![]() :

восстановлением остатка (сложение с

У), запоминанием нового результата во

временных регистрах или использование

дополнительного регистра с переключением.

:

восстановлением остатка (сложение с

У), запоминанием нового результата во

временных регистрах или использование

дополнительного регистра с переключением.

Программа для 51 с использованием дополнительного регистра В:

16.10.2000

Этот вариант проходит, если делитель не кратен 8. Когда делитель кратен 8 битам, то учитывается бит переноса после сдвига остатка влево. Т.е. сначала выполняется сдвиг, анализируется бит переноса и только затем производится сравнение.

Пример: деление 16 разрядов на 8.

Для

экономии времени выполнения операций

иногда отказываются от использования

цикла.

Для

экономии времени выполнения операций

иногда отказываются от использования

цикла.

Пример: 15/78.7