- •Микропроцессорные системы мпс (Полетаев Игорь Алексеевич) 4-й курс Iсеместр 2000/2001 гг.

- •Классификация процессоров

- •Классификация контроллеров. Сферы применения 32-разрядных контроллеров

- •Обзор 8-разрядных контроллеров

- •Общая структура контроллеров семейства mCs-51i8x51

- •Структура контроллеров семейства pic16Схх

- •Структура команд и методы адресации

- •Методы адресации в pic-контроллерах

- •Язык Ассемблер

- •Программирование арифметических операций

- •Табличные вычисления

- •Порты ввода-вывода

- •Таймер-счётчик

- •Последовательный интерфейс mCs51

- •Работа последовательного порта в мультиконтроллерных системах

- •Определение тактовой частоты при работе с последовательным портом

- •Интерфейсы контроллеров pic

- •Последовательный связной интерфейс

- •Структурная схема приёмника

- •Модуль прерываниёMCs51

- •Система прерываний pic16

- •16-Ти разрядные контроллеры на примере mCs96

- •Вопросы

Структура контроллеров семейства pic16Схх

Большинство контроллеров построено по RISK-архитектуре, что отражается на длительности машинного цикла и структуре команд, их длине и времени выполнения. За исключением команд перехода все команды выполняются за один машинный цикл. При работе с памятью используется гарвардская архитектура: отдельные шины данных и команд, имеющих разную разрядность и работающих параллельно, т.е. во время выполнения одной команды считывается другая. Поэтому время выполнения команд перехода – 2 цикла: нарушается работа конвейера. Объём памяти сильно различается в этом семействе.

25.09.2000

Контроллеры имеют закрытую архитектуру, т.е. к ним нельзя подключить внешнюю память программы и данных.

Схема PIC16C74 приведена ниже.

FSR– функциональные специальные регистры;

W– регистр – аккумулятор.

Каждый порт имеет альтернативную функцию (кроме трёх битов порта В). у порта А есть специальный вывод – вывод с открытым коллектором. Порт В используется для прерываний (один тип прерываний INTвторой – специальный).портDможет работать как обычный и как параллельный порт.

Контроллер имеет один вектор прерывания, срабатывание по которому может происходить от двенадцати источников. Это является большим недостатком контроллера. Надо проверять программно, что за устройство подало запрос. Поэтому реакция на прерывание – десятки микросекунд.

Восьмиуровневый аппаратный стек без программного доступа предназначен для хранения адресов возврата. Область стека не принадлежит ни для программной, ни к памяти данных, а указатель стека не доступен.

Память программ имеет объём 4 кило слова, а все команды кодируются одним словом.

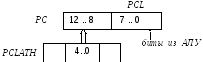

Младший байт программного счётчика (PCL) доступен, старший байт – недоступен, а формируется через регистрPCLATH. Старшие биты загружаются разными способами. В команде перехода явно указываются 11 бит.

Е сли

идёт явная программа сPC,

(т. е. записываются биты из АЛУ), то

сли

идёт явная программа сPC,

(т. е. записываются биты из АЛУ), то

Может показаться, что устройство контроллера достаточно сложное, но если рассмотреть контроллеры других фирм, то они окажутся ещё сложней.

Т.к. в команде перехода 11 бит адреса, то память разбита на 2 банка, а переход между ними выполняется переключение третьего бита (CPLATH).

Область ОЗУ организована как 256 х 8 бит и разбита на 2 банка, т.е. при адресации используется 7 битов. В каждом банке первые 32 адреса занимают регистры специальных функций.

Регистры контроллера:

|

Адрес |

Обозначение |

Назначение |

|

00h |

|

Физически отсутствует, а адрес используется для косвенной адресации (оригинально) |

|

01 h |

TMR 0 |

T/C 0 |

|

02 h |

PCL |

Младший байт PC |

|

03 h |

STATUS |

Регистр словосостояния |

|

04 h |

FSR |

Указатель для косвенной адресации |

|

05 h |

PORT A |

Внешняя линия или порт A |

|

06 h |

PORT B |

Порт B |

|

07 h |

PORT C |

Порт C |

|

08 h |

PORT D |

Порт D |

|

09 h |

PORT E |

Порт E |

|

0A h |

PCLATH |

Буфер старшей части PC |

|

0B h |

INTCON |

Управляющий регистр прерываний |

|

0C h |

PIR 1 |

Регистр флагов прерываний от периферийных устройств |

|

0D h |

PIR 2 |

То, что не поместилось в INTCONиPIR2 |

|

0E h |

TMR1L |

T/C 1 |

|

0F h |

TMR1H | |

|

10 h |

T1CON |

Управляющий регистр T/C1 |

|

11 h |

TMR 2 |

T/C 2 |

|

12 h |

T2CON |

Управляющий регистр T/C2 |

|

13 h |

SSPBUF |

Буфер синхронного последовательного порта |

|

14 h |

SSPCON |

Управляющий регистр синхронного последовательного порта |

|

15 h |

CCPR1L |

|

|

16 h |

CCPR1H | |

|

17 h |

CCP1CON |

Управляющий регистр CCP1 – модуля |

|

18 h |

RCSTA |

Управляющий регистр для приёма последовательного порта |

|

19 h |

TXREG |

Данные для передачи последовательного порта |

|

1A h |

RCREG |

Данные для приёма последовательного порта |

|

1B h |

CCPR1L |

CCP – модуль |

|

1X h |

CCPR2H | |

|

1D h |

CCP2CON | |

|

1E h |

ADRES |

Результат изменения АЦП |

|

1F h |

ADCON 0 |

Управляющий регистр АЦП |

|

81 h |

OPTION |

Регистр конфигурации |

|

85 h |

TRISA |

Указатель направления передачи порта А |

|

86 h |

TRISB |

Указатель направления передачи порта В |

|

87 h |

TRISC |

Указатель направления передачи порта С |

|

88 h |

TRISD |

Указатель направления передачи порта D |

|

89 h |

TRISE |

Указатель направления передачи порта Е |

|

8c h |

PTE1 |

Разрешение прерываний от периферийных устройств |

|

8d h |

PTE2 | |

|

8e h |

PCON |

Регистр контроля включения питания |

|

92 h |

PR2 |

Регистр периода для ШИМ |

|

93 h |

SSPADR |

Абонентский адрес кристалла в режиме I²C |

|

94 h |

SSPSTAT |

Флаги синхронного последовательного порта |

|

98 h |

TXSTA |

Управляющий регистр для передачи последовательного интерфейса |

|

99 h |

SPBRG |

Скорость передачи последовательного интерфейса |

|

9f h |

ADCON1 |

Управляющий регистр АЦП |

С восьми разрядным АЛУ связан W(Working) – регистр, который не принадлежит пространству памяти данных, и адресоваться к нему как к ячейке нельзя. При выполнении двуместных операций один из операндов находится вW– регистре, а результат помещается в зависимости от второго операнда: еслиd=0, то результат остаётся вW, еслиd=1, то результат помещается в регистр-источник.

Регистр конфигурации CONFIGнаходится в памяти программы и является недоступным из программы, хранится в ПЗУ. При программировании необходимо установить следующие режимы:

|

Биты |

Обозначение |

Назначение |

|

5 |

CP1 |

Защита кода |

|

4 |

CP0 | |

|

3 |

PWRTE |

Разрешение выдержки времени после включения питания |

|

2 |

WDTE |

Разрешение работы сторожевого таймера |

|

1 |

FOSC1 |

Выбор типа генератора |

|

0 |

FOSC0 |

Регистр OPTION:

|

Биты |

Обозначение |

Назначение |

|

7 |

RBPV |

Подключение активной нагрузки к порту В |

|

6 |

INTEDG |

Фронт сигнала внешнего прерывания (0 – отрицательный, 1 – положительный) |

|

5 |

T0CS |

Источник импульсов для Т/С0 (один внешний, другой внутренний) |

|

4 |

T0SE |

Счётчик 0 (1 – инкремент по отрицательному фронту, 0 – инкремент по положительному фронту) |

|

3 |

PSA |

Предварительный делитель (0 – подключен к Т/С0, 1 – к сторожевому таймеру) |

|

2 |

PS2 |

Коэффициент деления предварительного делителя |

|

1 |

PS1 | |

|

0 |

PS0 |

Во многих устройствах не предусмотрена кнопка сброса, что вызывает проблему при сбое программы. Поэтому в средствах ВТ предусматривают специальные аппаратные средства – супервизоры, контролирующие изменение определённых сигналов и вырабатывающие аппаратный сброс при их отсутствии.

В PICпрограммируемых интерфейсных контроллерах роль супервизора выполняетWatchDayTimer(WDT), представляющий полностью независимый встроенныйR-Cгенератор. Он вырабатывает сигнал сброса при переполнении с номинальной выдержкой 18 мс и максимальной с пре делителем 2.5 с. еслиWDTвключён, то в цикле управления должна присутствовать командаCLRWDT, постоянно сбрасывающая сторожевой таймер.