- •Условное обозначение, структура и характеристики выпрямительного диода.

- •2. Условное обозначение, структура и характеристики стабилитрона.

- •3. Условное обозначение, структура и характеристики биполярного транзистора.

- •4. Режимы работы биполярного транзистора. Соотношения между токами.

- •5. Условное обозначение, структура и характеристики полевого транзистора.

- •6. Принцип действия полупроводниковых приборов. Электронно-дырочный переход.

- •7. Принцип действия полупроводниковых приборов. Переход металл- диэлектрик – полупроводник.

- •8.Принцип действия полупроводниковых приборов. Переход Шоттки.

- •16()Логические элементы цифровых устройств. Типы и характеристики логических элементов.

- •18. Типовые кцу. Полусумматор. Реализуемая функция, таблица истинности, структурная схема.

- •19.Типовые кцу. Одноразрядный сумматор. Реализуемая функция, таблица истинности, структурная схема.

- •20. Типовые кцу. Одноразрядный полусумматор. Реализуемая функция, таблица истинности, структурная схема.

- •22.Типовые кцу. Сумматор паралелльный. Реализуемая функция, структурная схема

- •Типовые кцу. Демультиплексор. Реализуемая функция, таблица истинности, структурная схема.

- •26.Типовые кцу. Преобразователи кодов. Реализуемая функция, таблица истинности структурная схема.

- •27.Триггеры. Общие понятия.

- •28.Асинхронный rs-триггер. Структура, схемное обозначение, таблица переключений, временная диаграмма работы.

- •29.Синхронный rs-триггер. Структура, схемное обозначение, таблица переключений, временная диаграмма работы.

- •30.Синхронный jk-триггер. Cхемное обозначение, таблица переключений, временная диаграмма работы.

- •31.Двухступенчатый rs-триггер. Структура, схемное обозначение.

- •33.Счетный т- триггер. Схемы построения.

- •34.Последовательностные цифровые устройства. Запоминающий регистр. Назначение, структура.

- •35.Последовательностные цифровые устройства. Регистр сдвига.. Назначение, структура.

- •41. Внешние запоминающие устройства взу. Назначение, структура, типы, характеристики.

- •42. Оперативные запоминающие устройства озу, созу, кэш. Назначение, структура, схемное обозначение.

- •43.Оперативные запоминающие устройства озу. Статические и динамические озу.

- •44. Постоянные запоминающие устройства пзу. Назначение, структура, типы.

- •45. Микропроцессоры. Основные понятия, параметры микропроцессоров.

- •46.Структура микропроцессора и основные параметры.

- •47. Регистровая структура микропроцессора.

- •48.Алу, назначение, выполняемые операции.

- •49.Операционный усилитель. Идеальный операционный усилитель. Преобразователи на операционных усилителях.

- •51.Понятие обратной связи. Усилители на операционном усилителе.

- •55.Энергетические преобразователи. Определение, классификация.

- •56.Типовые энергетические преобразователи – выпрямители.

- •57.Типовые энергетические преобразователи – стабилизаторы.

- •58. Усилительный каскад с общим эмиттером на биполярном транзисторе.

- •60.Опотоэлектр. Сис-мы Источники излучения.

- •61.Оптоэлектронные системы. Приемники излучения.

- •63.Устройства и элементы индикации. Электронно-лучевая трубка.

- •64.Устройства и элементы индикации. Жидкокристаллические индикаторы и дисплеи.

- •65. Плазменные элементы и панели

- •66.Устройства и элементы индикации. Основные тенденции развития.

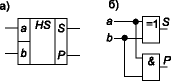

18. Типовые кцу. Полусумматор. Реализуемая функция, таблица истинности, структурная схема.

К типовым кцу относятся: полусумматор, полный сумматор, последовательного и параллельного действия – арифметические устройства, без деления и умножения.

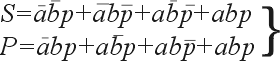

Полусумматор (рис. 3) имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма). Работу его отражает таблица истинности 2 (табл. 2), а соответствующие уравнения имеют вид:

![]()

|

Из уравнений (5) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль И (рис. 3б).

19.Типовые кцу. Одноразрядный сумматор. Реализуемая функция, таблица истинности, структурная схема.

Он

(рис. 4) имеет три входа: a, b — для двух

слагаемых и p — для переноса из предыдущего

(более младшего) разряда и два выхода:

S — сумма, P — перенос в следующий (более

старший) разряд. Обозначением полного

двоичного сумматора служат буквы SM.

Работу его отражает таблица истинности

3 (табл. 3).Таблица 3

№ наб. |

a |

b |

p |

P |

S |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

2 |

0 |

1 |

0 |

0 |

1 |

3 |

0 |

1 |

1 |

1 |

0 |

4 |

1 |

0 |

0 |

0 |

1 |

5 |

1 |

0 |

1 |

1 |

0 |

6 |

1 |

1 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

1 |

Уравнения,

описывающие работу полного двоичного

сумматора, представленные в совершенной

дизъюнктивной нормальной форме (СДНФ),

имеют видУравнение для переноса может

быть минимизировано:P = ab + ap + bp.(7)

Уравнения,

описывающие работу полного двоичного

сумматора, представленные в совершенной

дизъюнктивной нормальной форме (СДНФ),

имеют видУравнение для переноса может

быть минимизировано:P = ab + ap + bp.(7)

20. Типовые кцу. Одноразрядный полусумматор. Реализуемая функция, таблица истинности, структурная схема.

В двоичной системе счисления операция

сложения двух двоичных чисел в одном

разряде осуществляется по правилу:

двоичной системе счисления операция

сложения двух двоичных чисел в одном

разряде осуществляется по правилу:

X |

Y |

P(перенос) |

S(сумма) |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Из таблицы видно, что P(X,Y) = X&Y

Формулу для S можно получить двумя способами: либо по алгоритмам получения СДНФ или СКНФ, либо по сводной таблице логических функций двух переменных .

![]() S(X,Y)

=

S(X,Y)

=

![]() =

=

![]() =

&

=

&

![]() =

&

(X

=

&

(X

![]() Y)

=

Y)

=

= (

![]()

![]() )

& (X

Y)

= X

&

&

Y

)

& (X

Y)

= X

&

&

Y

Предпоследняя формула — это СКНФ, последняя— СДHФ. Для построения функциональной схемы мы воспользуемся структурной формулой ( ) & (X Y) ,так как в ней наименьшее количество операций. Получим структурные формулы и функциональную схему одноразрядного полусумматора:

P(X,Y) = X&Y; S = & (X Y)

Типовые КЦУ. Сумматор последовательный. Реализуемая функция, структурная схема.Последовательный сумматор должен преобразовывать последовательные коды слагаемых в последовательный код суммы этих слагаемых. Такие сумматоры обычно строятся на основе одноразрядного комбинационного сумматора, в котором для запоминания сигнала переноса используется D-триггер (рис. 12.6):При последовательном суммировании разряды ai и bi слагаемых А и В, начиная с младших, поступают на входы одноразрядного комбинационного сумматора SM с выходов сдвигающих регистров. Значения разрядов суммы Si заносятся в освобождающиеся разряды одного из сдвигающих регистров. На вход pi сумматора SM поступает сигнал переноса, который был получен в предыдущем такте при суммировании ai - 1, bi - 1 и Pi - 1. Для запоминания сигнала переноса используется D-триггер. Очевидно, для сложения m разрядных чисел А и В используется m+1 такт (в последнем (m+1)-ом такте перенос из самого старшего разряда поступает на вход сумматора, где суммируется с нулевыми значениями цифр слагаемых). Поэтому такой сумматор обладает очень низким быстродействием. С целью ускорения процесса сложения используются параллельные сумматоры.

1 рисунок – сумматор последовательного действия.