- •Цифровая схемотехника

- •1 .Цепи ускоренного переноса.

- •2.Системы и принцип работы озу.

- •3.Схема мультиплексора и способы их наращивания. Схема демультиплексора и способы их наращивания.

- •5. Классификация и назначение преобразователей кодов; преобразователи кодов прямого в обратный и дополнительный; преобразователи десятичного в двоично-десятичный.

- •6. Триггеры. Схемотехника асинхронного и синхронного rs-триггеров, счетного t-триггеров, d-триггеров, jk-триггеров.

- •7. Принцип построения и работы регистров параллельного действия и регистров последовательного действия.

- •9.Преобразователи цап и ацп

- •10.Организация и принцип работы постоянных запоминающих устройств

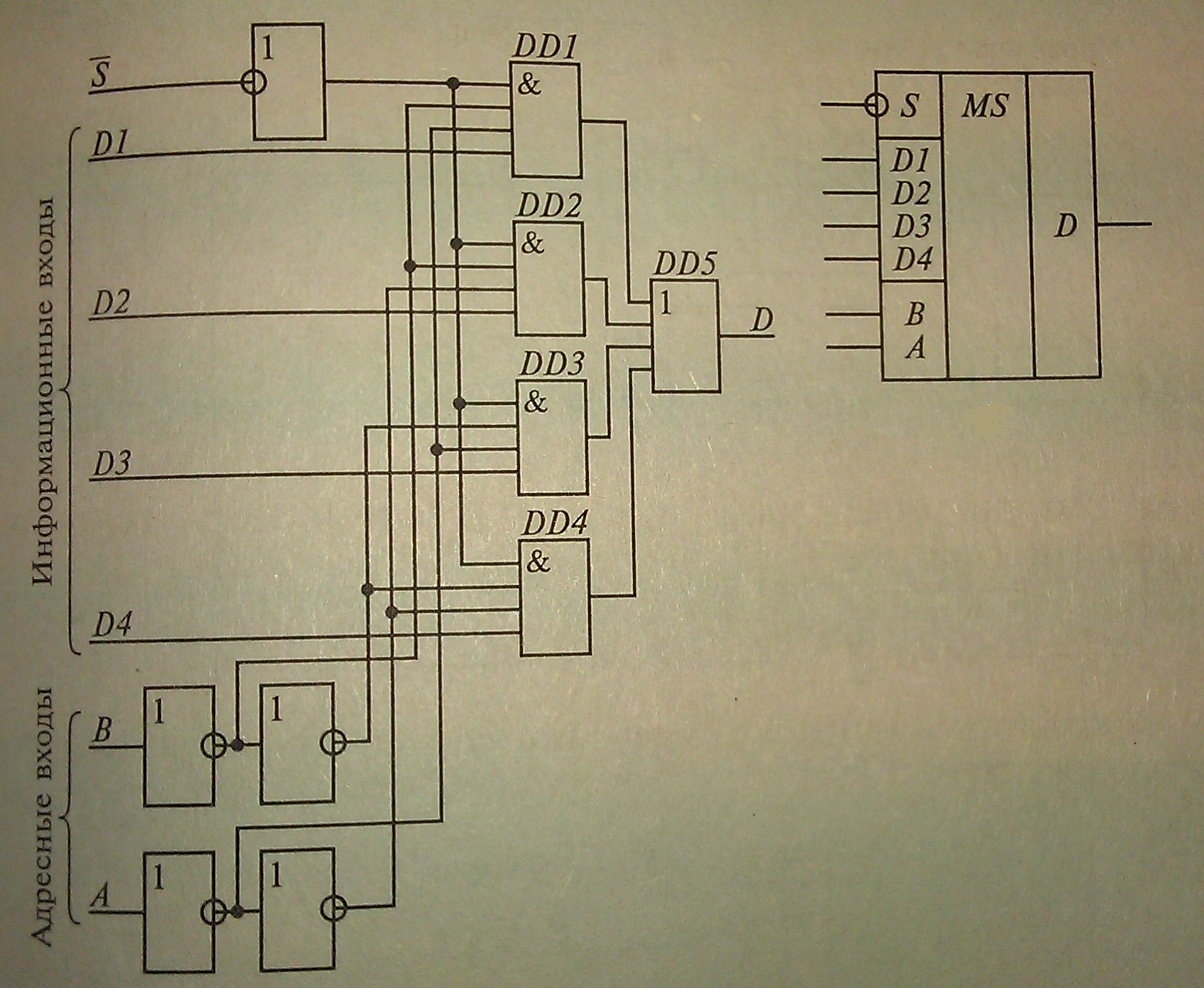

3.Схема мультиплексора и способы их наращивания. Схема демультиплексора и способы их наращивания.

М

ультиплексор

(MS)-

устройство, в котором в зависимости от

управляющего кода осуществляется

передача информации с одного из нескольких

входов на выход. В схемах MS

используются электронные ключи, замыкание

которых производится под действием

управляющих сигналов, приходящих,

например, с дешифратора. Часто функции

дешифратора и ключа объединены в одном

элементе И. Схемы MS

в интегральном исполнении имеют

стробирующие входы S.

При подаче на этот вход лог.0 дается

разрешение на передачу информации на

выход схемы в строго определенное время,

определяемое длительностью строба

(такт информации). Также использование

этого хода позволяет строить схемы MS

на большее число информационных входов.

Сигналы проходят через логические

элементы MS

и реализуют один из минтермов. Если

количество передаваемых входных сигналов

превышает количество входов MS,

применяют несколько схем, объединенных

в мультиплексорное дерево.

ультиплексор

(MS)-

устройство, в котором в зависимости от

управляющего кода осуществляется

передача информации с одного из нескольких

входов на выход. В схемах MS

используются электронные ключи, замыкание

которых производится под действием

управляющих сигналов, приходящих,

например, с дешифратора. Часто функции

дешифратора и ключа объединены в одном

элементе И. Схемы MS

в интегральном исполнении имеют

стробирующие входы S.

При подаче на этот вход лог.0 дается

разрешение на передачу информации на

выход схемы в строго определенное время,

определяемое длительностью строба

(такт информации). Также использование

этого хода позволяет строить схемы MS

на большее число информационных входов.

Сигналы проходят через логические

элементы MS

и реализуют один из минтермов. Если

количество передаваемых входных сигналов

превышает количество входов MS,

применяют несколько схем, объединенных

в мультиплексорное дерево.

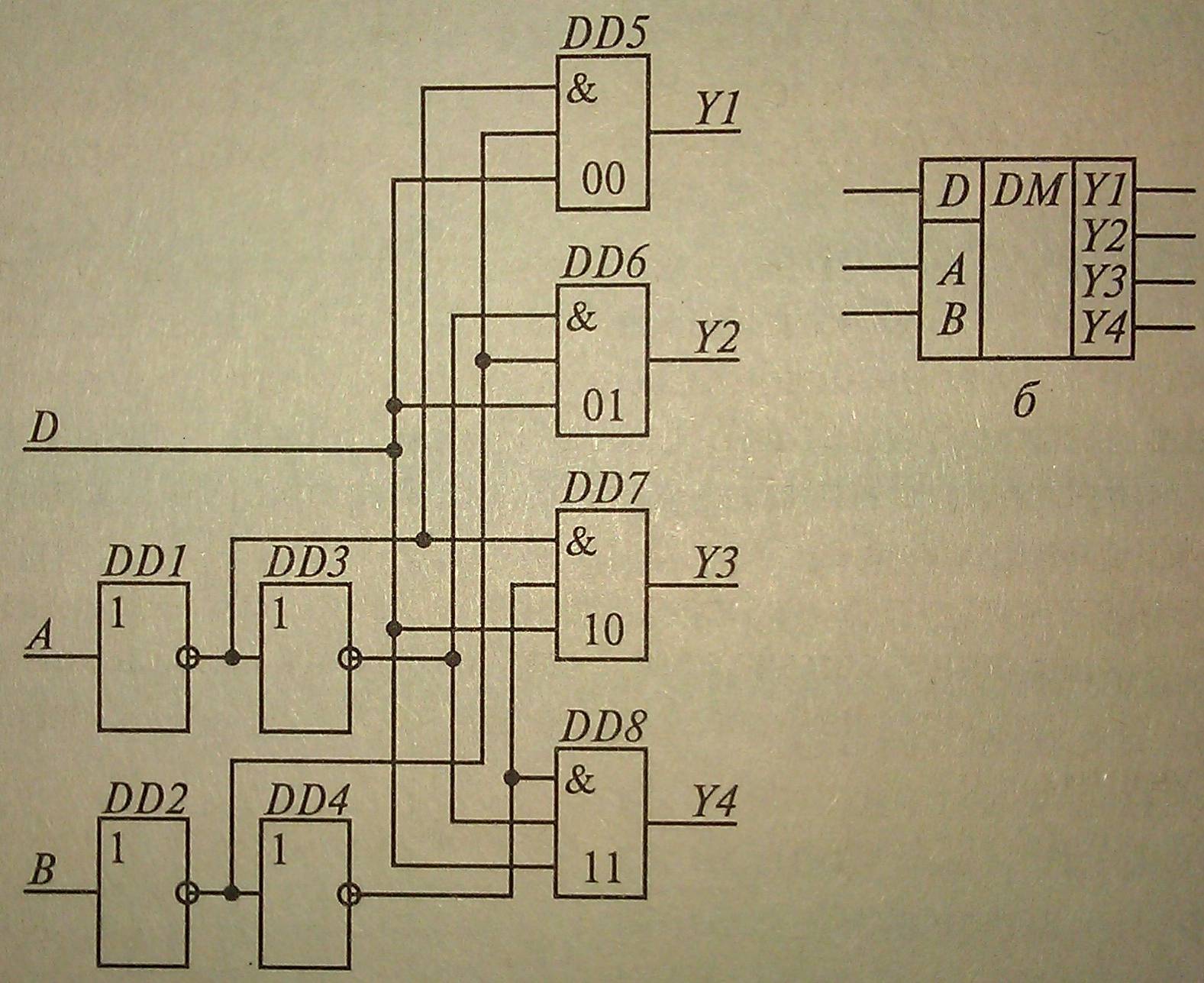

Демультиплескор (DM) имеет один информационный вход D и несколько выходов и осуществляет коммутацию входа к одному из выходов, адрес которого установлен на адресных шинах. Если требуется большое число входов, может быть построено демультиплексорное дерево.

Объединяя MS и DM, можно построить устройство, в котором по заданным адресам один из входов подключается к одному из выходов.

4. Назначение и характеристика сумматоров. Комбинационные схемы сумматоров (одноразрядные на 3 входа), принцип построения многоразрядных сумматоров с последовательным переносом, принцип сложения многоразрядных чисел на основе комбинационных сумматоров, особенности построения многоразрядных сумматоров с ускоренным переносом.

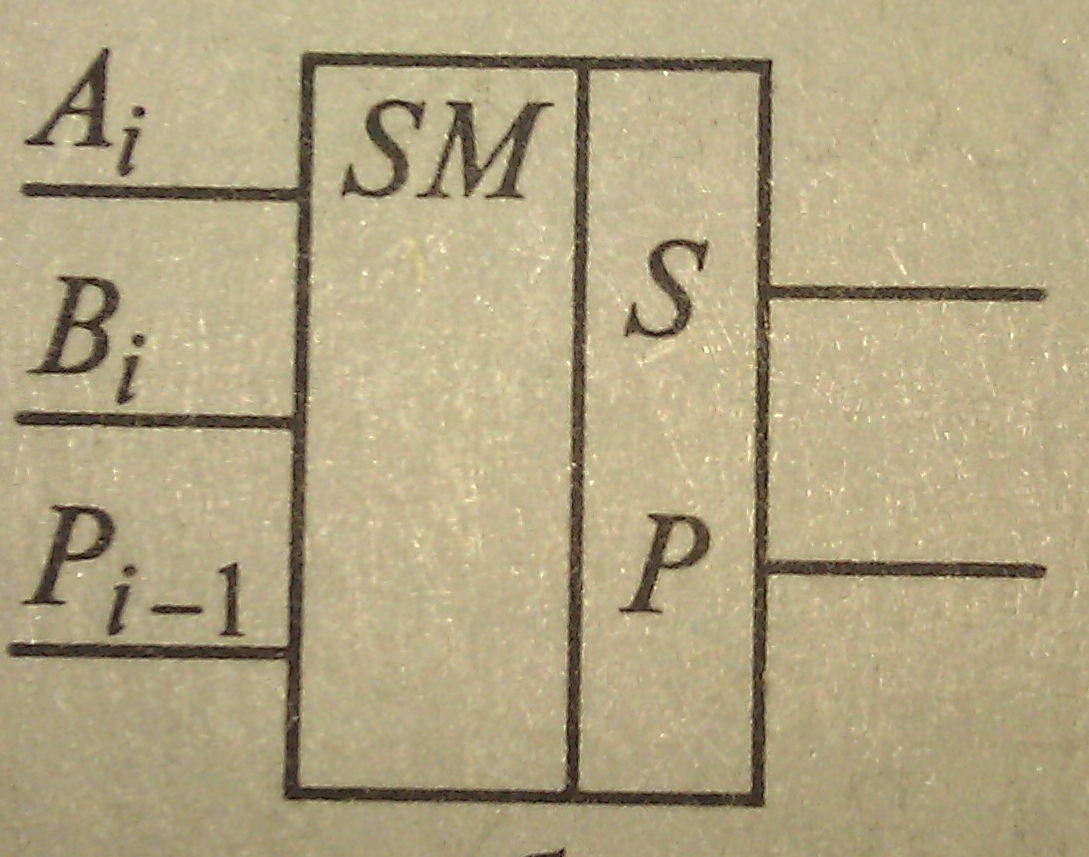

С умматор

(SM)-

узел АЛУ ЭВМ, выполняющий операцию

суммирования кодов двух чисел. В

зависимости от способа организации

суммирования SM

подразделяются на комбинационные

(значение суммы на выходе исчезает со

снятием слагаемых, поданных на вход) и

накапливающие

(результат суммирования сохраняется

после снятия слагаемых со входа). По

способу обработки многоразрядных чисел:

параллельные

(слагаемые всех разрядов вводятся

одновременно), последовательные

(осуществляют поразрядное сложение,

начиная с младшего разряда, с запоминанием

образовавшегося переноса до поступления

более старших разрядов с последующим

их суммированием).

умматор

(SM)-

узел АЛУ ЭВМ, выполняющий операцию

суммирования кодов двух чисел. В

зависимости от способа организации

суммирования SM

подразделяются на комбинационные

(значение суммы на выходе исчезает со

снятием слагаемых, поданных на вход) и

накапливающие

(результат суммирования сохраняется

после снятия слагаемых со входа). По

способу обработки многоразрядных чисел:

параллельные

(слагаемые всех разрядов вводятся

одновременно), последовательные

(осуществляют поразрядное сложение,

начиная с младшего разряда, с запоминанием

образовавшегося переноса до поступления

более старших разрядов с последующим

их суммированием).

Простейшие схемы сумматоров имеют два или три входа. Схемы, в которых производится сложение двух одноразрядных чисел, называются полусумматорами. Схемы, в которых производится сложение двух одноразрядных чисел и третьего слагаемого, в качестве которого, как правило, выступает единица переноса, называются сумматорами. Pi-1- 3-е слагаемое, в качестве которого, как правило, выступает единица переноса из более младшего разряда.

5. Классификация и назначение преобразователей кодов; преобразователи кодов прямого в обратный и дополнительный; преобразователи десятичного в двоично-десятичный.

Под преобразованием кодов понимается преобразование n-разрядных двоичных чисел, представляющих информацию в одном заданном коде, в m-разрядные двоичные числа, представляющие эту информацию в другом коде.

Микросхемы преобразователей кодов (англ. сonverter) служат для преобразования входных двоичных кодов в выходные двоично-десятичные и наоборот. Они используются довольно редко, так как применение двоично-десятичных кодов ограничено узкой областью, например, они применяются в схемах многоразрядной десятичной индикации. К тому же при правильной организации схемы часто можно обойтись без преобразования в двоично-десятичный код, например, выбирая счетчики, работающие в двоично-десятичном коде. Преобразование двоично-десятичного кода в двоичный встречается еще реже.

Знак «плюс» изображается как 0, а «минус» - 1.

Вид кода |

Правило кодирования |

Вид закодированного числа |

Прямой |

Изображение кода совпадает с изображением числа. В знаковой части ставится 1(если число отрицательно). |

Апр. = 1.0001010 |

Обратный |

Значение разрядов после точки меняется на обратное. Код знака остается без изменения. |

Аобр. = 1.1110101 |

Дополнительный |

Образуется как обратный с дополнительным прибавлением 1к младшему разряду. |

Адоп. = 1.1110101 +_______ 1 1.1110110

|

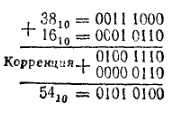

Д воично-

десятичное кодирование- кодирование,

при котором каждая десятичная цифра

представляется группой двоичных цифр.

Число битов в таких группах строго

фиксируется (их должно быть не менее 4)

с сохранением всех левых нулевых

разрядов. При сложении двух чисел в коде

прямого замещения необходимо добавить

корректирующее слагаемое 610=

01102.

воично-

десятичное кодирование- кодирование,

при котором каждая десятичная цифра

представляется группой двоичных цифр.

Число битов в таких группах строго

фиксируется (их должно быть не менее 4)

с сохранением всех левых нулевых

разрядов. При сложении двух чисел в коде

прямого замещения необходимо добавить

корректирующее слагаемое 610=

01102.