- •Цифровая схемотехника

- •1 .Цепи ускоренного переноса.

- •2.Системы и принцип работы озу.

- •3.Схема мультиплексора и способы их наращивания. Схема демультиплексора и способы их наращивания.

- •5. Классификация и назначение преобразователей кодов; преобразователи кодов прямого в обратный и дополнительный; преобразователи десятичного в двоично-десятичный.

- •6. Триггеры. Схемотехника асинхронного и синхронного rs-триггеров, счетного t-триггеров, d-триггеров, jk-триггеров.

- •7. Принцип построения и работы регистров параллельного действия и регистров последовательного действия.

- •9.Преобразователи цап и ацп

- •10.Организация и принцип работы постоянных запоминающих устройств

Цифровая схемотехника

1 .Цепи ускоренного переноса.

П редназначены

для переноса разряда, в случае если в

результате арифметической операции

разряд должен быть перенесен. Т.к.

компьютер умножает и складывает

«столбиком» необходимо как-то организовать

перенос цепи. Ускорение передачи

происходит за счет того, что нам не

приходится использовать никаких

регистров для запоминания переноса

разрядов.

редназначены

для переноса разряда, в случае если в

результате арифметической операции

разряд должен быть перенесен. Т.к.

компьютер умножает и складывает

«столбиком» необходимо как-то организовать

перенос цепи. Ускорение передачи

происходит за счет того, что нам не

приходится использовать никаких

регистров для запоминания переноса

разрядов.

tзадержки = τ запаздывания 1разряда*nразрядов

Перенос в третий разряд после заполнения полностью первых двух разрядов.

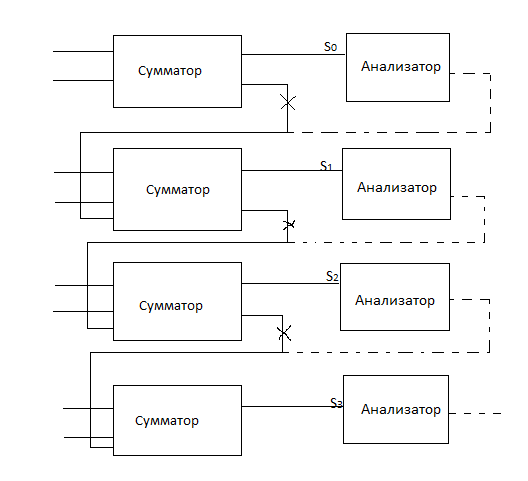

Если последовательный перенос, то цепочка сумматоров с последовательным переносом: перенос этого разряда идет на вход переноса следующего разряда и т.д. Чтобы не было задержки строят не последовательный перенос, а параллельный перенос. Все суммы с сумматоров анализируют и сразу выявляют есть ли перенос, если он есть, то не дожидаясь пока получится сумма перенос сразу идет на следующий сумматор, уже сформированы все входы. Что бы не ждать по цепочкам, когда придет переносимый разряд. Каждый раз анализируются входы и перенос с предыдущего разряда. Если есть перенос, то идет далее- на формирование следующего.

Перенос, когда А и В равно 1.

Если все состояния записать и проанализировать, то получится перенос для общего случая. Пример использования- сумматор.

2.Системы и принцип работы озу.

О перативное

ЗУ используется в условиях, когда

необходимо выбирать и обновлять хранимую

информацию в высоком темпе работы

процессора цифрового устройства.

Вследствие этого в ОЗУ предусматриваются

три режима работы: режим хранения при

отсутствии обращения к ЗУ, режим чтения

хранимых слов и режим записи новых слов.

При этом в режимах чтения и записи ОЗУ

должно функционировать с высоким

быстродействием. В цифровых устройствах

ОЗУ используются для хранения и программ.

перативное

ЗУ используется в условиях, когда

необходимо выбирать и обновлять хранимую

информацию в высоком темпе работы

процессора цифрового устройства.

Вследствие этого в ОЗУ предусматриваются

три режима работы: режим хранения при

отсутствии обращения к ЗУ, режим чтения

хранимых слов и режим записи новых слов.

При этом в режимах чтения и записи ОЗУ

должно функционировать с высоким

быстродействием. В цифровых устройствах

ОЗУ используются для хранения и программ.

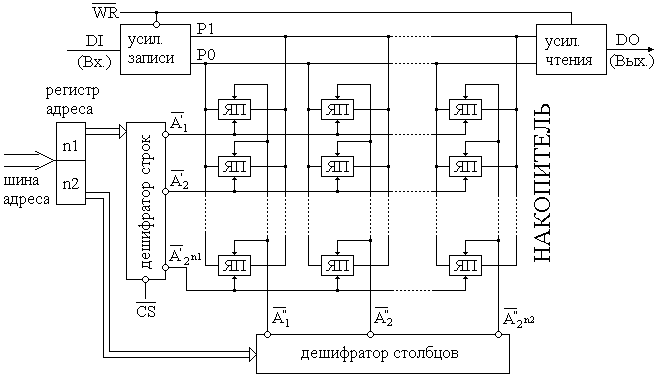

И нформация

хранится в накопителе. Он представляет

собой матрицу, составленную из элементов

памяти (ЭП=ЯП), расположенных вдоль строк

и столбцов. Элемент памяти может хранить

1 бит информации (лог.0 либо лог.1). Кроме

того, он снабжен управляющими цепями

для установки элемента в любом из трех

режимов: режиме

хранения (в

котором он отключается от входа и выхода

микросхемы), режиме

чтения (в

котором содержащаяся в ЭП информация

выдается на выход микросхемы), режиме

записи (в

котором в ЭП записывается новая

поступающая со входа микросхемы

информация).

нформация

хранится в накопителе. Он представляет

собой матрицу, составленную из элементов

памяти (ЭП=ЯП), расположенных вдоль строк

и столбцов. Элемент памяти может хранить

1 бит информации (лог.0 либо лог.1). Кроме

того, он снабжен управляющими цепями

для установки элемента в любом из трех

режимов: режиме

хранения (в

котором он отключается от входа и выхода

микросхемы), режиме

чтения (в

котором содержащаяся в ЭП информация

выдается на выход микросхемы), режиме

записи (в

котором в ЭП записывается новая

поступающая со входа микросхемы

информация).

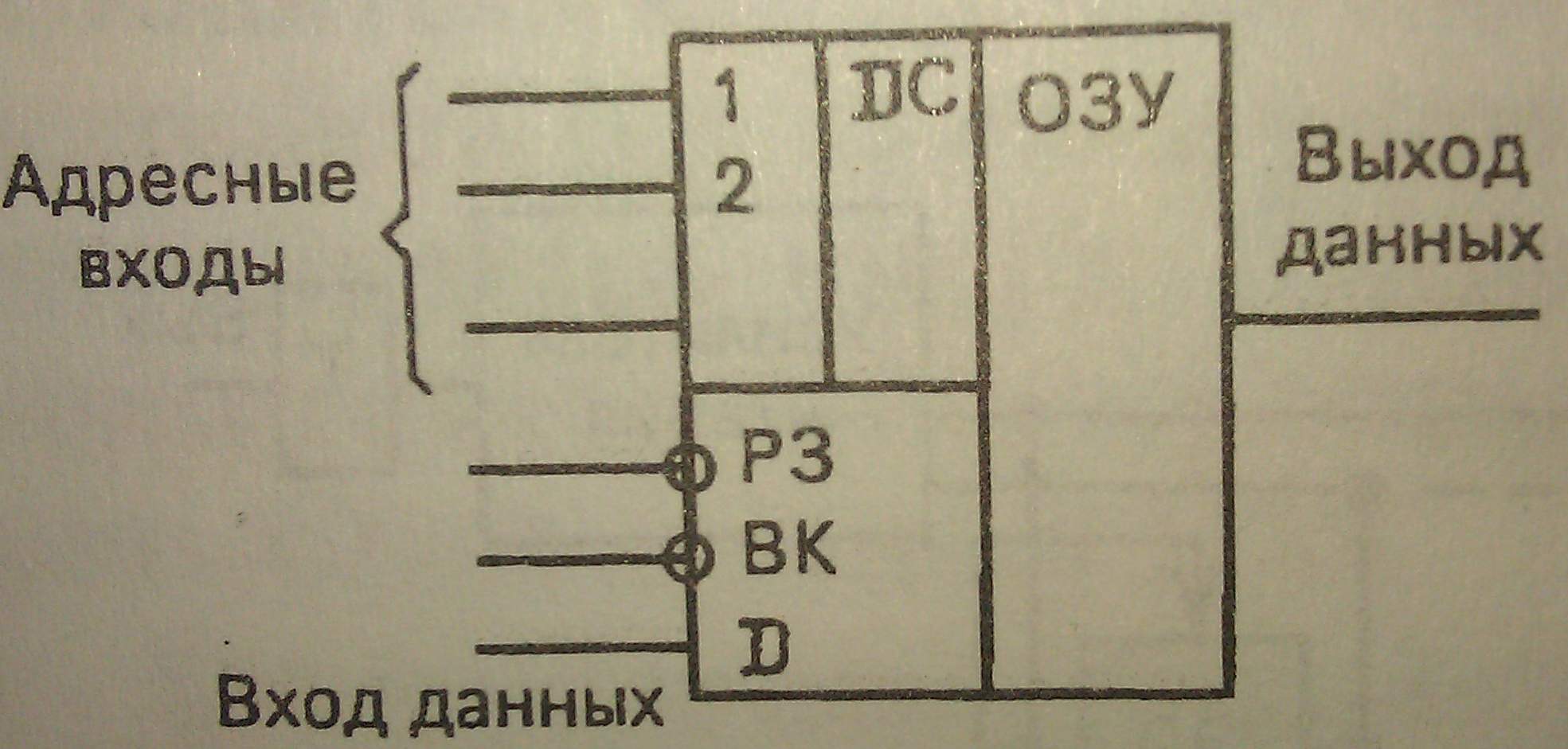

Каждому ЭП приписан номер, называемый адресом элемента. Для поиска требуемого ЭП указывается строка и столбец, соответствующие положению ЭП в накопителе. Адрес ЭП в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Число строк и число столбцов накопителя выбираются равными целой степени двух. И если число строк Nстр = 2n1 и число столбцов Nст = 2n2, то общее число ЭП (емкость накопителя):

N = Nстр * Nст = 2n1 * 2n2 = 2 (n1+n2) = 2n,

где n = n1 + n2 - число разрядов адреса, принимаемого в регистр адреса.

Например, при емкости N = 210 = 1024 число разрядов адреса n = 10; при этом выбирается n1 = n2 = n/2 = 5, в этом случае число строк и число столбцов накопителя 2n1 = 2n2 = 32.

Каждая группа разрядов адреса подается на соответствующий дешифратор: дешифратор строк и дешифратор столбцов. При этом каждый из дешифраторов создает на одной из своих выходных цепей уровень лог.1, выбранный ЭП оказывается под воздействием уровня лог.1. При чтении содержимое ЭП выдается на усилитель чтения и с него на выходной триггер и выход микросхемы. Режим записи устанавливается подачей сигнала на вход разрешения записи (РЗ=WR). При уровне лог.0 на входе РЗ открывается усилитель записи и бит информации со входа данных поступает в выбранный ЭП и запоминается в нем. Эти процессы происходят в том случае, если на входе выбора кристалла (ВК=CS) активный уровень лог.0. При уровне лог.1 на этом входе на всех выходах дешифратора устанавливается уровень лог.0 и ЗУ оказывается в режиме чтения.