- •Назначение, область применения и способы оценки производительности многопроцессорных вычислительных систем

- •Классификация архитектур по параллельной обработке данных

- •Гибридная архитектура (numa). Организация когерентности многоуровневой иерархической памяти

- •Организация когерентности многоуровневой иерархической памяти

- •Кластерная архитектура.

- •Кластерная архитектура. Проблемы выполнения сети связи процессоров в кластерной системе Кластерная архитектура

- •Сети связи процессоров в кластерной системе

- •Принципы построения коммуникационных сред на основе интерфейса sci

- •Принципы построения коммуникационных сред на основ среды Myrinet

- •Способы организации высокопроизводительных процессоров. Ассоциативные процессоры.

- •Ассоциативные процессоры

- •Способы организации высокопроизводительных процессоров. Конвейерные процессоры.

- •Конвейерные процессоры

- •Способы организации высокопроизводительных процессоров. Матричные процессоры

- •Матричные процессоры

- •Простые коммутаторы с временным разделением. Алгоритмы арбитража

- •Простые коммутаторы с временным разделением

- •Алгоритмы арбитража

- •П ростые коммутаторы с пространственным разделением. Особенности реализации шин

- •Особенности реализации шин

- •Составные коммутаторы. Коммутатор Клоза. Баньян-сети

- •Распределенные составные коммутаторы. Граф межмодульных связей Convex Exemplar spp1000.

- •Распределенные составные коммутаторы. Граф межмодульных связей мвс-100.

- •Распределенные составные коммутаторы. Граф межмодульных связей мвс-1000.

- •Требования к компонентам мвс. Отношение "стоимость / производительность".

- •Требования к компонентам мвс. Масштабируемость

- •Требования к компонентам мвс. Совместимость и мобильность программного обеспечения

- •Надежность и отказоустойчивость мвс.

- •Пути достижения параллелизма

- •Примеры параллельных вычислительных систем

- •Принципы разработки параллельных методов

- •Моделирование параллельных программ

- •Этапы разработки параллельных алгоритмов

- •1. Разделение вычислений на независимые части

- •2. Выделение информационных зависимостей

- •3. Масштабирование набора подзадач

- •4. Распределение подзадач между процессорами

- •Mpi: основные понятия и определения

- •Введение в разработку mpi программ. Инициализация и завершение mpi-программ. Операции передачи данных. Типы данных.

- •Коллективные операции передачи данных в mpi

- •Передача данных от одного процесса всем процессам программы

- •Передача данных от всех процессов одному процессу. Операция редукции

- •Обобщенная передача данных от одного процесса всем процессам

- •Обобщенная передача данных от всех процессов одному процессу

- •Общая характеристика среды выполнения mpi-программ

- •Понятие производного типа данных в mpi

- •Способы конструирования производных типов данных. Непрерывный способ конструирования

- •Непрерывный способ конструирования

- •Способы конструирования производных типов данных. Векторный способ конструирования

- •Векторный способ конструирования

- •Способы конструирования производных типов данных. Индексный способ конструирования

- •Индексный способ конструирования

- •Способы конструирования производных типов данных. Структурный способ конструирования

- •Структурный способ конструирования

- •Формирование сообщений при помощи упаковки и распаковки данных

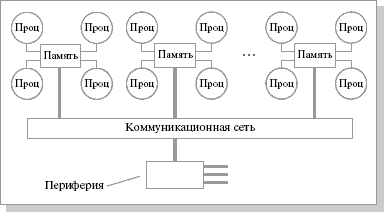

Гибридная архитектура (numa). Организация когерентности многоуровневой иерархической памяти

Главная особенность гибридной архитектуры NUMA (nonuniform memory access) – неоднородный доступ к памяти.

Г ибридная

архитектура

совмещает достоинства систем с общей

памятью

и относительную дешевизну систем с

раздельной памятью. Суть этой архитектуры

– в особой организации памяти: память

физически распределена по различным

частям системы, но логически она является

общей,

так что пользователь видит единое

адресное пространство.

Система построена из однородных базовых

модулей (плат), состоящих из небольшого

числа процессоров и блока памяти. Модули

объединены с помощью высокоскоростного

коммутатора.

Поддерживается единое

адресное пространство,

аппаратно поддерживается доступ к

удаленной памяти. При этом доступ к

локальной

памяти

осуществляется в несколько раз быстрее,

чем к удаленной.

ибридная

архитектура

совмещает достоинства систем с общей

памятью

и относительную дешевизну систем с

раздельной памятью. Суть этой архитектуры

– в особой организации памяти: память

физически распределена по различным

частям системы, но логически она является

общей,

так что пользователь видит единое

адресное пространство.

Система построена из однородных базовых

модулей (плат), состоящих из небольшого

числа процессоров и блока памяти. Модули

объединены с помощью высокоскоростного

коммутатора.

Поддерживается единое

адресное пространство,

аппаратно поддерживается доступ к

удаленной памяти. При этом доступ к

локальной

памяти

осуществляется в несколько раз быстрее,

чем к удаленной.

Организация когерентности многоуровневой иерархической памяти

Понятие когерентности кэшей описывает тот факт, что все центральные процессоры получают одинаковые значения одних и тех же переменных в любой момент времени. Данные, попадающие в кэш одного компьютера, могут быть недоступны другому. Чтобы этого избежать, следует провести синхронизацию информации, хранящейся в кэш-памяти процессоров.

Для обеспечения когерентности кэшей существует несколько возможностей:

использовать механизм отслеживания шинных запросов (snoopy bus protocol)

выделять специальную часть памяти, отвечающую за отслеживание достоверности всех используемых копий переменных.

Наиболее известными системами архитектуры cc-NUMA являются: HP 9000 V-class в SCA-конфигурациях, SGI Origin3000, Sun HPC 15000, IBM/Sequent NUMA-Q 2000. На сегодня максимальное число процессоров в cc-NUMA-системах может превышать 1000 (серия Origin3000).

PVP-архитектура. Кластерная архитектура

PVP (Parallel Vector Process) – параллельная архитектура с векторными процессорами

Основным признаком PVP-систем является наличие специальных векторно-конвейерных процессоров, в которых предусмотрены команды однотипной обработки векторов независимых данных, эффективно выполняющиеся на конвейерных функциональных устройствах. Системы PVP-архитектуры могут являться машинами общего назначения (general purpose systems). Однако, векторные процессоры весьма дорого стоят, то эти машины не могут быть общедоступными. Наиболее популярны три машины PVP-архитектуры:

CRAY X1, SMP-архитектура. Пиковая производительность системы в стандартной конфигурации может составлять десятки терафлопс.

NEC SX-6, NUMA-архитектура. Пиковая производительность системы может достигать 8 Тфлопс, производительность одного процессора составляет 9,6 Гфлопс.

Fujitsu-VPP5000, MPP-архитектура. Производительность одного процессора составляет 9.6 Гфлопс, пиковая производительность системы может достигать 1249 Гфлопс, максимальная емкость памяти – 8 Тбайт.

Кластерная архитектура.

Кластер представляет собой два или более компьютеров (узлов), объединяемые при помощи сетевых технологий на базе шинной архитектуры или коммутатора и предстающие перед пользователями в качестве единого информационно-вычислительного ресурса. В качестве узлов кластера могут быть выбраны серверы, рабочие станции и обычные персональные компьютеры. Узел характеризуется тем, что на нем работает единственная копия операционной системы. Преимущество кластеризации в случае сбоя какого-либо узла: другой узел кластера может взять на себя нагрузку неисправного узла, и пользователи не заметят прерывания в доступе. Возможности масштабируемости кластеров позволяют многократно увеличивать производительность приложений. Кластеризация может осуществляться на разных уровнях компьютерной системы, включая аппаратное обеспечение, операционные системы, программы-утилиты, системы управления и приложения. Чем больше уровней системы объединены кластерной технологией, тем выше надежность, масштабируемость и управляемость кластера.

Типы кластеров

Условное деление на классы предложено Язеком Радаевским и Дугласом Эдлайном:

Класс I. Класс машин строится целиком из стандартных деталей (низкие цены, простое обслуживание, аппаратные компоненты доступны из различных источников).

Класс II. Система имеет эксклюзивные или не слишком широко распространенные детали (очень хорошей производительность, но при более высокой стоимости).

Распространенные типы кластеров:

системы высокой надежности;

системы для высокопроизводительных вычислений;

многопоточные системы (используются для обеспечения единого интерфейса к ряду ресурсов, которые могут со временем произвольно наращиваться (или сокращаться).