- •1. Загальна структура і функції комп’ютера

- •2. Продуктивність комп’ютера

- •3. Швидкодія мікропроцесорів

- •4. Система магістралі

- •5.Зв’язок між компонентами комп’ютера через магістраль

- •6.Магістраль рсі

- •7. Внутрішня пам’ять

- •8.Функції і характеристики підсистеми пам’яті

- •Размещение

- •10. Сучасні тенденції в організації модулів пам’яті

- •11. Стек

- •12.Зовнішня память

- •13.Збереження інформації на магнітних дисках

- •15.Оптична пам'ять

- •16. Збереження інформації на магнітних стрічках

- •17. Введення – виведення

- •18.Програмне введення –виведення

- •19. Введення-виведення по прериванню

- •20.Прямий доступ до пам’яті

- •Зовнішні інтерфейси….. Типы интерфейсов

- •Концепція організації операційних систем

- •Планування завдань

- •Керування розподілом пам’яті

- •Вектори обчислень

- •Арифметико-логічний пристрій

- •Система команд комп’ютера

- •Характеристики та функції команд

- •Структура і функції центрального процесора

- •30.Структура центрального процесора

- •31.Організація набору регістрів

- •32. Конвеєрна обробка команд

- •33. Комп’ютери зі скороченим набором команд

- •34. Організація конвеєру в risc-процесорах

- •35. Порівняльні характеристики risc і сisc комп’ютерів

- •36. Суперскалярні процесори

- •37. Паралелізм на рівні машинних команд

- •38. Функції пристрою керування

- •39. Мікрооперації

- •40. Управління роботою процесора

- •41. Пристрої управління із жорсткою логікою

- •42. Мікропрограмне керування

- •43. Управління послідовністю виконання мікрокоманд

- •44. Використання мікропрограмування

- •45. Параллельна обробка

- •46. Організація мікропроцесорних систем

- •47. Симетричні мультипроцесорні системи

- •48. Інформаційна цілісність кешів та протокол mesi

- •49. Кластери

- •50. Системи зі змінним часом звернення до пам’яті

41. Пристрої управління із жорсткою логікою

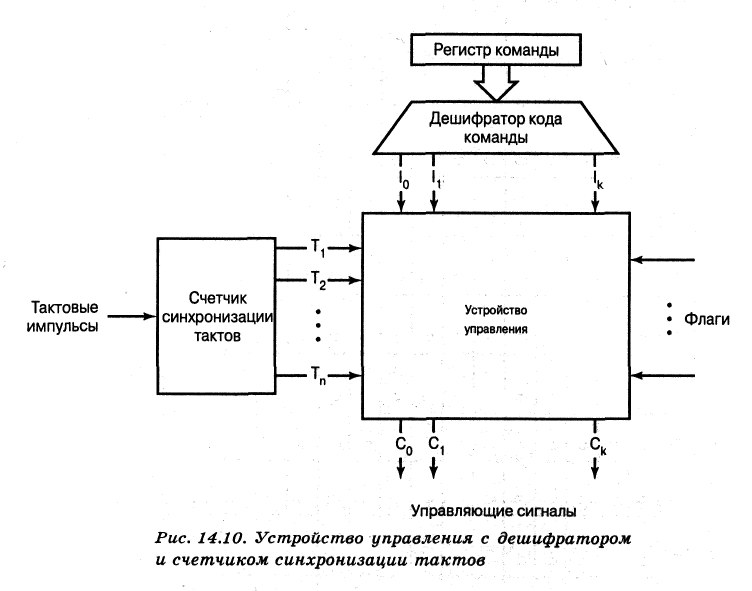

Основными входными сигналами для него являются тактовые импульсы, код в регистре команд, флаги и управляющие сигналы магистрали. Коды флагов и управляющие сигналы магистрали подаются в устройство управления непосредственно, без промежуточного преобразования, а код команды и тактовые импульсы предварительно обрабатываются.

Сначала рассмотрим код команды. Устройство управления должно проанализировать код команды и сформировать соответствующий набор управляющих сигналов, свой для каждой команды. Для упрощения работы устройства управления каждый вариант кода команды желательно преобразовать в отдельный сигнал. Такое преобразование выполняется дешифратором — схемой, которая каждую кодовую комбинацию на входных линиях преобразует в сигнал на одном из множества выходов. В общем случае дешифратор имеет п входных линий и 2" выходных. Каждая из 2" двоичных кодовых комбинаций на п входных линиях возбуждает сигнал на одной из 2" выходных линий. Пример такого преобразования представлен в табл. 14.3. Дешифратор в реальном устройстве управления имеет более сложную формулу преобразования, поскольку в процессорах часто код команды имеет переменную длину. С примерами схемной реализации дешифраторов вы сможете познакомиться в приложении А.

Узел синхронизации устройства управления формирует повторяющуюся последовательность импульсов. Период следования тактовых импульсов должен быть достаточно большим, чтобы в течение этого времени сигналы могли распространиться по линиям магистралей и пройти через логические схемы процессора. Как будет показано далее, в каждом такте машинного цикла обработки команды устройство управления формирует свою последовательность сигналов. Поэтому тактовые импульсы подаются на вход счетчика синхронизации, а его выходы используются устройством управления в качестве номера текущего такта. В конце цикла счетчик сбрасывается в исходное состояние, соответствующее такту t1.

На схеме, представленной на рис. 14.10, показаны дешифратор и счетчик синхронизации тактов.

Логическая схема устройства управления

Теперь нам осталось рассмотреть, как с помощью логических комбинационных схем входные сигналы преобразуются в устройстве управления в выходные. По существу, нам необходимо для каждого формируемого управляющего сигнала построить булеву функцию преобразования комбинации входных сигналов. Лучше всего это пояснить на примере. Вернемся вновь к примеру, представленному на рис. 14.5. В сопутствующей примеру табл. 14.1 выписаны последовательности микроопераций и управляющих сигналов для трех из четырех фаз цикла обработки команды.

Рассмотрим один из управляющих сигналов -— С5. По этому сигналу данные с внешней магистрали считываются в регистр MBR. Этот сигнал в табл. 14.1 используется дважды. Определим два новых управляющих сигнала, Р и Q, комбинация которых определяет текущую фазу цикла обработки командам!

PQ — 00 фаза извлечения

PQ = 01 фаза косвенной адресации

PQ = 10 фаза выполнения

PQ = 11 фаза прерывания