- •1. Загальна структура і функції комп’ютера

- •2. Продуктивність комп’ютера

- •3. Швидкодія мікропроцесорів

- •4. Система магістралі

- •5.Зв’язок між компонентами комп’ютера через магістраль

- •6.Магістраль рсі

- •7. Внутрішня пам’ять

- •8.Функції і характеристики підсистеми пам’яті

- •Размещение

- •10. Сучасні тенденції в організації модулів пам’яті

- •11. Стек

- •12.Зовнішня память

- •13.Збереження інформації на магнітних дисках

- •15.Оптична пам'ять

- •16. Збереження інформації на магнітних стрічках

- •17. Введення – виведення

- •18.Програмне введення –виведення

- •19. Введення-виведення по прериванню

- •20.Прямий доступ до пам’яті

- •Зовнішні інтерфейси….. Типы интерфейсов

- •Концепція організації операційних систем

- •Планування завдань

- •Керування розподілом пам’яті

- •Вектори обчислень

- •Арифметико-логічний пристрій

- •Система команд комп’ютера

- •Характеристики та функції команд

- •Структура і функції центрального процесора

- •30.Структура центрального процесора

- •31.Організація набору регістрів

- •32. Конвеєрна обробка команд

- •33. Комп’ютери зі скороченим набором команд

- •34. Організація конвеєру в risc-процесорах

- •35. Порівняльні характеристики risc і сisc комп’ютерів

- •36. Суперскалярні процесори

- •37. Паралелізм на рівні машинних команд

- •38. Функції пристрою керування

- •39. Мікрооперації

- •40. Управління роботою процесора

- •41. Пристрої управління із жорсткою логікою

- •42. Мікропрограмне керування

- •43. Управління послідовністю виконання мікрокоманд

- •44. Використання мікропрограмування

- •45. Параллельна обробка

- •46. Організація мікропроцесорних систем

- •47. Симетричні мультипроцесорні системи

- •48. Інформаційна цілісність кешів та протокол mesi

- •49. Кластери

- •50. Системи зі змінним часом звернення до пам’яті

40. Управління роботою процесора

Для того чтобы устройство управления могло решать возложенные на него задачи, оно должно располагать определенной входной информацией о текущем состоянии системы и формировать выходные сигналы, которые будут определять дальнейшее поведение системы. Это спецификация устройства управления извне. Если же рассматривать внутреннюю структуру узла, то в ней должны присутствовать логические схемы, необходимые для решения перечисленных выше задач.

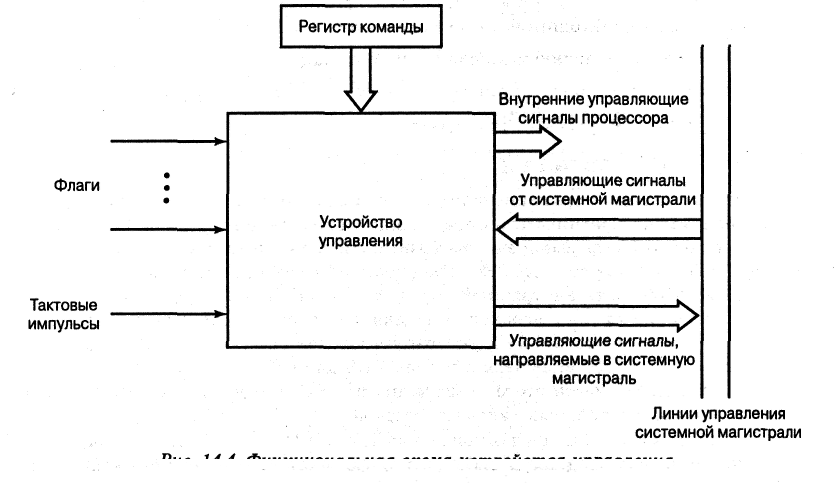

На рис. 14.4 показана функциональная схема устройства управления, на которой представлена входная и выходная информация. В качестве входной информации устройство управления использует следующие сигналы и данные.

Тактовые импульсы. Тактовые импульсы синхронизируют выполнение всех операций во времени. Длительность выполнения каждой микрооперации (или нескольких одновременно выполняемых микроопераций) равна одному такту.

Регистр команд. Поле кода операции в регистре команды определяет, какую последовательность микроопераций должно сформировать устройство управления.

Флаги. Они необходимы для определения текущего состояния процессора и результата выполнения последней операции в АЛУ. Например, при выполнении команды ISZ (приращение и пропуск команды, если результат равен нулю) устройство управления должно увеличить код в регистре PC в том случае, если установлен флаг Z (флаг равенства результата нулю). Сигналы на управляющих линиях магистрали. По этим линям в устройство управления поступают сигналы запроса прерывания и подтверждения от внешних устройств.

Устройство управления формирует следующие сигналы.

Управляющие сигналы, распространяемые внутри процессора. Эти сигналы делятся на две категории: сигналы, задающие передачу данных из одного регистра в другой, и сигналы запуска определенных операций в АЛУ.

Сигналы, передаваемые по управляющим линиям системной магистрали. Эти сигналы также делятся на две категории: сигналы, управляющие работой памяти, и сигналы, управляющие работой модулей ввода-вывода.

Рассмотрим теперь, как с помощью управляющих сигналов устройство управления организует работу процессора при излечении команды. Устройство постоянно следит за тем, какая фаза цикла обработки команды является текущей в данный момент. По состоянию регистра ICC оно определяет, что должна выполняться фаза извлечения. Первым делом устройство организует пересылку содержимого PC в MAR. Для этого формируются управляющие сигналы, открывающие вентили между разрядами PC и разрядами MAR. Следующая операция — чтение слова из памяти в MBR и приращение кода адреса в PC. Для этого устройство управления одновременно формирует такие сигналы:

сигнал, который открывает вентили, связывающие выходы разрядов регистра MAR с линиями адреса системной магистрали;

сигнал READ на линии управления системной магистрали;

сигнал, который открывает вентили, связывающие линии данных системной магистрали со входами разрядов регистра MBR;

внутренний управляющий сигнал процессора, инициирующий работу схемы приращения содержимого регистра PC и сохранение результата в PC.