- •1. Загальна структура і функції комп’ютера

- •2. Продуктивність комп’ютера

- •3. Швидкодія мікропроцесорів

- •4. Система магістралі

- •5.Зв’язок між компонентами комп’ютера через магістраль

- •6.Магістраль рсі

- •7. Внутрішня пам’ять

- •8.Функції і характеристики підсистеми пам’яті

- •Размещение

- •10. Сучасні тенденції в організації модулів пам’яті

- •11. Стек

- •12.Зовнішня память

- •13.Збереження інформації на магнітних дисках

- •15.Оптична пам'ять

- •16. Збереження інформації на магнітних стрічках

- •17. Введення – виведення

- •18.Програмне введення –виведення

- •19. Введення-виведення по прериванню

- •20.Прямий доступ до пам’яті

- •Зовнішні інтерфейси….. Типы интерфейсов

- •Концепція організації операційних систем

- •Планування завдань

- •Керування розподілом пам’яті

- •Вектори обчислень

- •Арифметико-логічний пристрій

- •Система команд комп’ютера

- •Характеристики та функції команд

- •Структура і функції центрального процесора

- •30.Структура центрального процесора

- •31.Організація набору регістрів

- •32. Конвеєрна обробка команд

- •33. Комп’ютери зі скороченим набором команд

- •34. Організація конвеєру в risc-процесорах

- •35. Порівняльні характеристики risc і сisc комп’ютерів

- •36. Суперскалярні процесори

- •37. Паралелізм на рівні машинних команд

- •38. Функції пристрою керування

- •39. Мікрооперації

- •40. Управління роботою процесора

- •41. Пристрої управління із жорсткою логікою

- •42. Мікропрограмне керування

- •43. Управління послідовністю виконання мікрокоманд

- •44. Використання мікропрограмування

- •45. Параллельна обробка

- •46. Організація мікропроцесорних систем

- •47. Симетричні мультипроцесорні системи

- •48. Інформаційна цілісність кешів та протокол mesi

- •49. Кластери

- •50. Системи зі змінним часом звернення до пам’яті

30.Структура центрального процесора

В состав процессора входят как программно доступные регистры, так и специальные регистры управления и состояния. Последние также могут неявно обрабатываться при выполнении определенных машинных команд. Программно доступные регистры могут иметь общее или специальное назначение, например предназначаться для хранения чисел в формате с плавающей точкой, адресов, индексов или указателей сегментов. Регистры управления и состояния используются для управления ходом выполнения операций в процессоре. Примером регистра подобного типа может служить счетчик команд — PC. Другим регистром этой группы является регистр слова состояния программы — PSW, который включает множество битов состояния и условий. В частности, в состав PSW входят биты, отражающие характер результата последней выполненной арифметической или логической команды, биты разрешения прерывания, индикатор режима выполнения программы (супервизорный/пользовательский).

Для повышения скорости обработки в процессоре может быть организован конвейерный режим. По существу, конвейерная организация предполагает разбивку цикла обработки команды на несколько отдельных этапов, которые следуют один за другим — этап извлечения команды, декодирования команды, определения адресов операндов, извлечения операндов, выполнения операции и записи результата. Команда "проходит" через эти этапы, как через технологические позиции на сборочном конвейере, и средства выполнения каждого этапа могут в один и тот же момент времени иметь дело с разными командами. Реализация такой стратегии обработки команд серьезно усложняется наличием команд перехода и определенной зависимостью команд друг от друга.

Структура процессора станет совершенно понятной, если задуматься над тем какие операции ему предстоит выполнять при обработке машинной команды.

Извлечение команды — процессор считывает команду из памяти.

Интерпретация команды — процессор расшифровывает команду и определяет, какие операции ему предстоит выполнить.

Извлечение данных — для выполнения команды может потребоваться прочесть данные из памяти или из модуля ввода-вывода.

Обработка данных — выполнение команды может потребовать преобразования данных, т.е. выполнения над ними определенных арифметических или логических операций.

Запись данных — если в процессе выполнения команды данные были изменены, результат необходимо где-то зафиксировать. В частности, результат может быть записан в память или передан в модуль ввода-вывода.

Чтобы выполнить перечисленные операции, процессору требуются определенные средства временного хранения информации. Ему нужно помнить, где находится выполняемая команда, и тогда можно будет определить, откуда выбрать следующую. Ему нужно хранить коды команд и данных во время их обработки. Другими словами, процессор нуждается в собственной внутренней памяти.

31.Організація набору регістрів

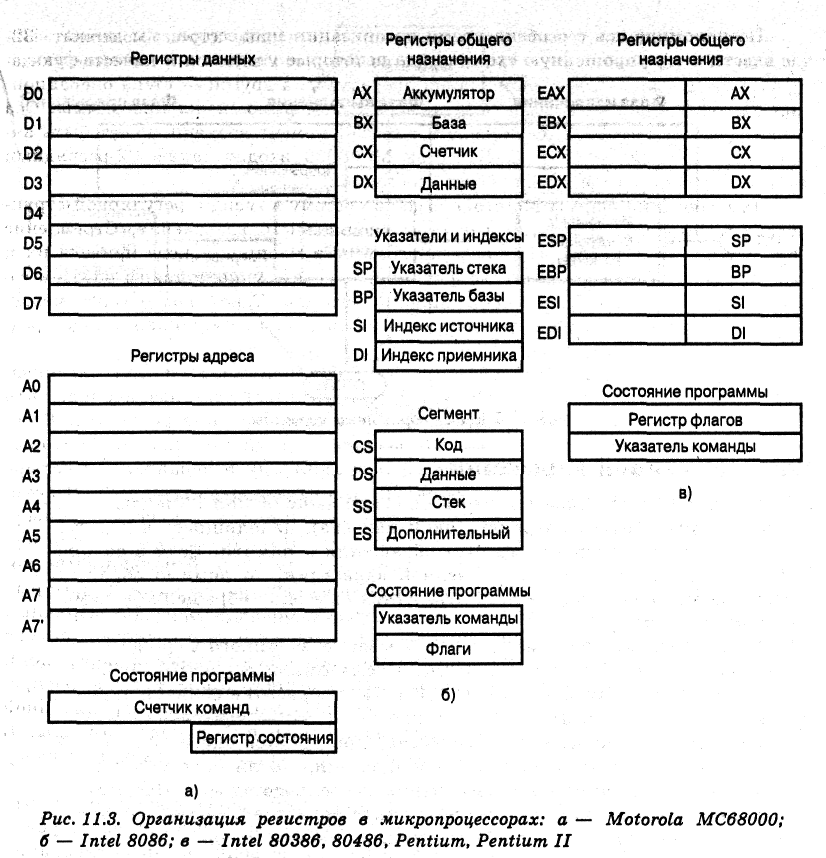

В микропроцессоре MC68000 имеется восемь 32-разрядных регистров данных и девять регистров адреса такой же длины. Хотя основное назначение регистров данных — манипуляция со значениями операндов, они используются и в качестве индексных регистров при формировании исполнительного адреса. Разрядность регистров позволяет работать с 8-, 16- или 32-разрядными элементами

данных в зависимости от кода операции. Регистры адреса содержат 32-разрядные адреса (без сегментации). Два из них используются в качестве указателей стека: один — стека прикладной программы, а другой — стека операционной системы в соответствии с текущим режимом выполнения программы. Оба регистра имеют номер 7, поскольку в каждый момент времени может быть активным только один из них. В состав MC68000 входит также 32-разрядный счетчик команд и 16-битовый регистр состояния.

Разработчики фирмы Motorola создали систему команд с регулярной структурой, в которой отсутствуют регистры специального назначения. Стремление обеспечить высокую эффективность программы в машинном коде привела их к мысли разделить регистры на две функциональные группы и таким образом сэкономить один бит в поле спецификации регистра. Такой компромисс между универсальностью назначения регистров и компактностью машинного кода представляется вполне разумным.

Разработчики микропроцессора Intel 8086 использовали при организации регистров другой подход. Каждый регистр имеет свое назначение, хотя некоторые из них могут использоваться и в качестве универсальных. В составе Intel 8086 имеется четыре 16-разрядных регистра данных, которые можно адресовать как целиком (все 16 разрядов), так и побайтово, и четыре 16-разрядных регистра, предназначенных для формирования адреса.

Из этого краткого описания двух конструкций процессоров следует, что не существует единого общепринятого подхода к организации регистров в процессоре (см. [TOON81J). Как и многие другие вопросы проектирования процессоров, эта проблема до сих пор является темой оживленных дискуссий и экспериментов.

В торой

вывод, касающийся организации регистров

в процессоре, иллю

стрируется

схемой регистров процессора Intel 80386,

представленной на

рис.

11.3,в [ELAY85J.

Этот

микропроцессор разрабатывался как

32-

разрядная

модификация процессора 8086. В состав

процессора 80386 входят

32-разрядные

регистры, но чтобы сохранить обратную

совместимость про

граммного

обеспечения, в нем сохранена прежняя

схема распределения

функций

между регистрами.

торой

вывод, касающийся организации регистров

в процессоре, иллю

стрируется

схемой регистров процессора Intel 80386,

представленной на

рис.

11.3,в [ELAY85J.

Этот

микропроцессор разрабатывался как

32-

разрядная

модификация процессора 8086. В состав

процессора 80386 входят

32-разрядные

регистры, но чтобы сохранить обратную

совместимость про

граммного

обеспечения, в нем сохранена прежняя

схема распределения

функций

между регистрами.