- •Министерство образования Российской Федерации

- •Пояснительная записка

- •2008 Г. Содержание

- •1 Сравнительный анализ возможных вариантов реализации 6

- •Введение

- •1.2 Схема на основе счетчика Джонсона

- •1.3 Схема на основе плм

- •1.4 Схема на основе пмл

- •1.5 Выбор наилучшего варианта реализации

- •2 Описание используемой серии элементов

- •2.1 Общая характеристика системы элементов кмоп

- •2.2 Описание применяемых микросхем

- •3. Получение таблиц и минимизация функций возбуждения и выходов в данном базисе

- •4 Разработка принципиальной электрической схемы

- •4.3 Описание работы узла с использованием временных диаграмм

- •5 Расчет временных параметров устройства

- •6 Расчет параметров генератора тактовых импульсов

- •7 Расчет мощности

- •Заключение

- •Список литературы

- •Приложение а.

2 Описание используемой серии элементов

2.1 Общая характеристика системы элементов кмоп

У нас в стране обширна номенклатура выпускаемых интегральных микросхем, делящихся на серии элементов по способу функциональной организации: КМОП, ТТЛ(Ш), ЭСЛ. Для построения устройств автоматики и вычислительной техники широкое применение находят цифровые микросхемы серии К1554, которые изготавливают по КМОП технологии с окисной изоляцией, двухуровневой металлизацией. Высокое быстродействие в сочетании с низкой потребляемой мощностью и большой нагрузочной способностью, широкий набор интерфейсных микросхем серии КР1554 позволяют создавать вычислительные устройства и устройства цифровой автоматике с качественно новыми характеристиками и высокимим технико экономическими показателями.

2.2 Описание применяемых микросхем

При описании микросхем серии КР1554 использовались сведения из электронного справочника “ИС серии 1533 1554 ”. В таблицах выводов Общим называется земляной вывод, Vcc - питающий вывод.

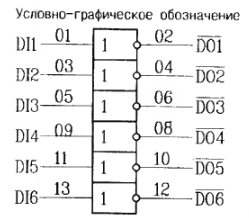

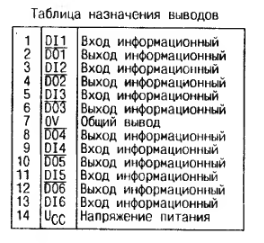

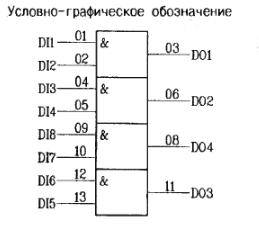

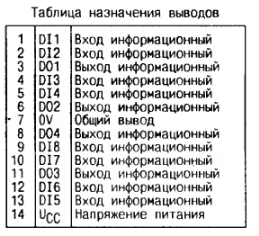

КР1554ЛН1 – 6 элементов НЕ

КР1554ЛИ1 – 4 элемента 2И

КР1533ЛЕ1 – 4 элемента 2ИЛИ-НЕ

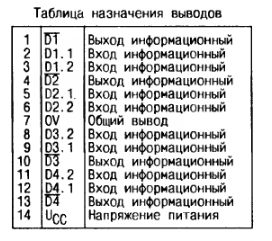

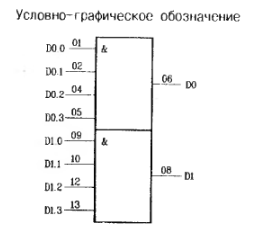

КР1554ЛИ6 – 2 элемента 4И

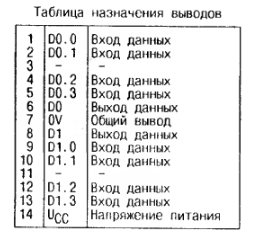

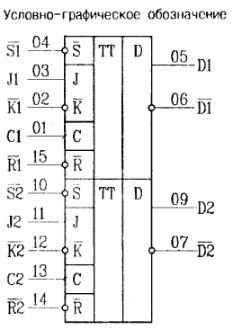

КР1554ТВ15 – 2 JK-триггера с управлением положительным фронтом

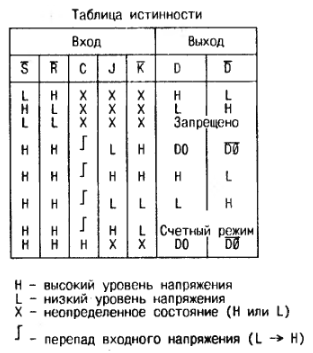

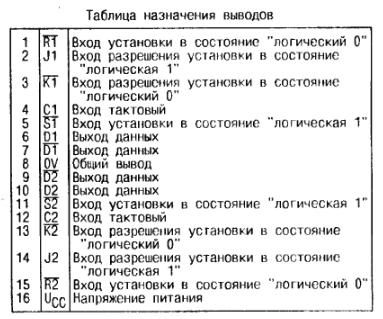

Микросхема КР1554ТВ15 состоит из двух независимых JK-триггеров, имеющих общую цепь питания. Вход синхронизации прямой динамический, поэтому данные от входов J и K передаются на выходы D и ¬D по положительному перепаду (фронту) импульса на входе С. Триггер имеет асинхронные входы установки ¬S и сброса ¬R с активным низким уровне. В таблице истинности представлены состояния для одного триггера.

КР1554ТМ9 – шесть D-триггеров с общим входом установки

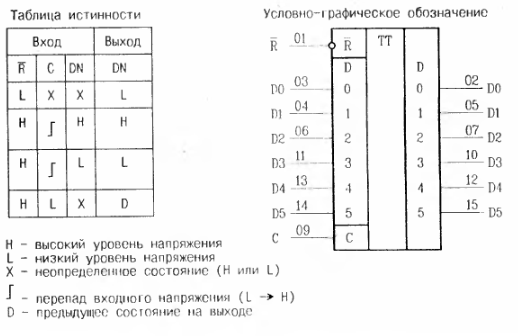

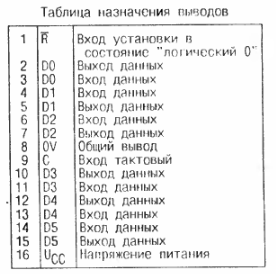

Микросхема КР1554ТМ9 содержит шесть D-триггеров. Все триггеры имеют общие входы асинхронного сброса ¬R (установки в состояние низкого уровня) и входа синхронизации С. Триггеры микросхемы имеют только прямые выходы данных DN.Установка триггера в состояние низкого уровня происходит после подачи на асинхронный вход напряжения низкого уровня. Информацию от входов DN можно загрузить в триггеры, если на вход ¬R подать напряжение высокого уровня, а на вход синхронизации С положительный перепад напряжения (фронт импульса). Состояния одного из триггера представлены в таблице истинности.

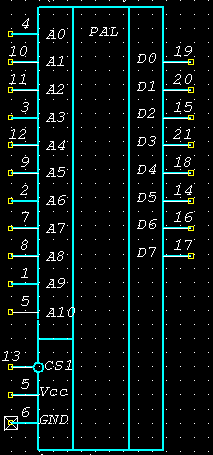

КР1556ХЛ10 – ПМЛ

Входа А0 – А10 информационные ПМЛ;

GND – общий вывод;

Ucc – напряжение питания;

CS1 – разрешающий работу ПМЛ вход;

D0- D7 – выходы данных ПМЛ;

Микросхема КР1556ХЛ10 относится к микросхемам ТТЛ (ТТЛШ). ПМЛ включает в себя последовательно включенные программируемые логические матрицы элементов И и ИЛИ, а также в ПМЛ входят блоки входных и выходных буферных каскадов. Эта микросхема начинает свою работу когда на инверсный разрешающий вход ее будет подано напряжение низкого уровня. После чего входные сигналы через входной буфер попадают на входы коньюнкторов. В результате образуются термы, которые в свою очередь приходят на входы дезъюнкторов. Все термы жестко распределены между входами дезъюнкторов.

Электрические параметры используемых при проектировании микросхем приведены отдельно в приложении А.