- •Питання для іспиту з дисципліни

- •“Комп’ютерна схемотехніка” для спеціальності 5.05010201

- •Особливості процесу виконання команди кр580вм80.

- •Поняття про цикл процесу виконання команди в мп.

- •Алгоритм циклічного обчислювального процесу.

- •Команди звернення до підпрограми.

- •Поняття про логічні адреси при формуванні 20-розрядної адреси у 16-розрядному процесорі.

- •Перерахуємо всі 10 типів:

- •Регістр прапорців мп і 8086, призначення прапорців.

- •Команди умовних викликів підпрограми. Приклади.

- •Практична частина

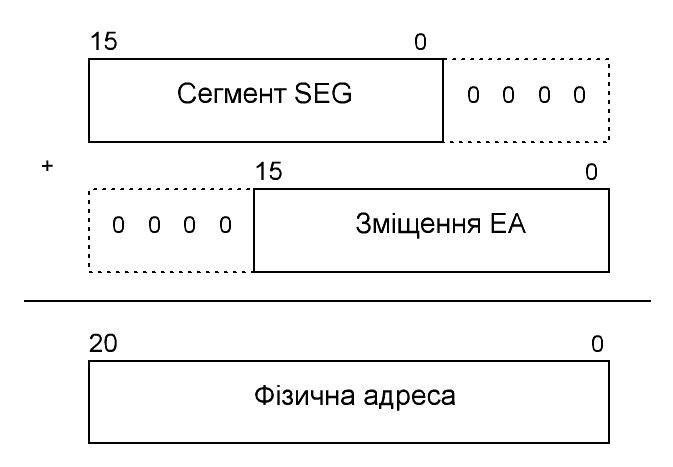

Поняття про логічні адреси при формуванні 20-розрядної адреси у 16-розрядному процесорі.

Для формування 20-розрядної адреси у 16-розрядному процесорі використовують інформацію двох 16-розрядних регістрів. У МП i8086 20-розрядна адреса формується з двох 16-розрядних адрес, які називають логічними. Перша логічна адреса, доповнена праворуч чотирма нулями, являє собою початкову адресу сегмента ємністю 64 кбайт. Друга логічна адреса визначає зміщення у сегменті, тобто відстань від початку сегмента до адресованої комірки.

Якщо вона дорівнює 0000, то адресується перша комірка сегмента, якщо FFFFH - то остання. Отже, логічний адресний простір розподілено на блоки суміжних адрес розміром 64 кбайт, тобто сегменти.

Особливості команд пересилання з регістрів у пам’ять і навпаки в МП і8086.

Особливості застосування шинного формувача КР580ВА86 для буферування шини адреси в МПС на МП і8080.

В

мікропроцесорний комплект КР580 входить

мікросхема шинного формувача КР580ВА86

, яка представляє собою 8- розрядний

прийомо-передавач

(рис.2.8) з тристабільними виходами  і

можливістю керування напрямом передачі

інформації.

і

можливістю керування напрямом передачі

інформації.

В зв'язку з тим, що інформація шиною адреси передається від МП, шинний формувач повинен передавати інформацію від сторони А, до якої під'єднані адресні виходи МП, до сторони В, до якої під'єднана адресна шина системи. Тому на входах Т обох мікросхем можна постійно підтримувати рівень логічної 1 (через гасячий резистор від джерела живлення).

Поняття про такти процесу виконання команди в МП.

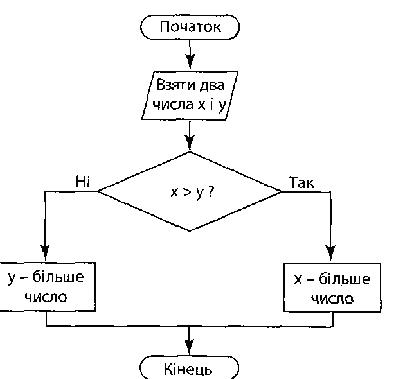

Організація розгалужень.

На блок-схемі алгоритму розгалуження є блок у вигляді ромба (умовний блок) . Умовному блоку відповідають команди умовних переходів. Ці команди використовують для організації розгалужень.

Як умови використовуються ознаки, які заносяться в тригери регістра ознак. Перевірка ознак полягає в перевірці вмісту цих тригерів.

Особливості виконання команди CALL.

При виконанні команди СALL , вміст PC, який представляє собою адресу наступної команди в основній програмі заноситься в дві сусідні комірки стекової памяті і тільки після цього в PC заноситься початкова адреса підпрограми , тобто виконуються наступні дії:

[(SP)-1] [(SP)-2] (PC)

SP (SP)-2

PC

Організація обчислювальних процесів з розгалуженням у МПС на МП , реалізація умовних переходів.

Шинний інтерфейс МП і8086, його структура.

Шинний інтерфейс містить:

Чотири сегментних регістра CS, DS,ES, SS, в які поміщаються початкові адреси сегментів памяті

Вказівник команди IP , який на відміну від МП і8086, містить зміщення в сегменті кодів поточної команди

Допоміжні регістри звязку

Суматор, який формує 20-ти розрядну адресу з двох 16-ти розрядних слів

Регістровий файл черги , команди на шість слів , який працює за принципом FIFO

Буфер шини, який сполучає внутрішні шини даних та адрес з зовнішньою шиною МП

Формування фізичної 20-розрядної адреси у 16-розрядному процесорі.

Фізична 20-розрядна адреса комірки пам’яті формується з двох логічних 16-розрядних адрес – початкової адреси сегменту і лінійної адреси в межах сегменту, яка називається зсувом або виконавчою адресою EA (Executive address).

Процедура формування фізичної адреси ілюструється рис.8.2.

Фізична адреса

формується як сума початкової адреси

сегменту Seg,

зсунутої на чотири розряди ліворуч, що

рівноцінно множенню на 24=16,

зі зсувом EA.

Таким чином фізична адреса буде

визначатися як

.

Фізичну адресу прийнято позначати у

вигляді Seg:EA,

де як Seg

і EA

можуть

використовуватися і позначення регістрів

і 16-розрядні дані.

.

Фізичну адресу прийнято позначати у

вигляді Seg:EA,

де як Seg

і EA

можуть

використовуватися і позначення регістрів

і 16-розрядні дані.

Рис.8.2 Формування фізичної адреси МП і8086

Особливості арифметичних команд в МП і8086.

Особливістю цих операцій є використання прапорців в регістрі стану, які можуть змінювти свій стан за виконанням команд: ADD,SUB, CNP, AND, TEST, OR, XOR

Спосіб запису:

REG, mem

Mem, REG

REG, REG

Mem, immed

REG, іmmed

Результатии записуються в операнд

Структура ППІ КР580ВВ55.

Двонапрравлений 8-ми розрядний буфер даних, який зєднює лінії даних цієї ВІС з системною шиною даних

Блок керування(читання-запис RWCU), що забезпечує керування передаванням даних і керуючих слів.

Три 8-ми розрядні порти вводу-виводу(порт A,B, C). Порт С поділений на два 4-х розрядні порти.

Блок керування групою А (CUA), куди входять порт А,

і блок керування групою В (СUB),

куди

входять порт В,

і блок керування групою В (СUB),

куди

входять порт В, .

.

Блок RWCU містить регістр керуючого слова, який позначається RCW/

Інформація про стан мікропроцесора, поняття про слово “стану”.

Особливістю мікропроцесора є те, що в кожному циклі в такті Т1 в інтервалі часу від моменту додатнього фронту Ф1 в такті Т1 до відємного фронту Ф2 в такті Т2 мікропроцесор видає сигнал синхронізації , а на шину даних видає інформацію про стан МП – це восьмирозрядна кодова комбінація, яка називається “слово стану”

Слово стану – це інформація про наміри мікропроцесора по відношенню до зовнішніх пристроїв.

Способи запису команд.

Для зручності представлення і запису команд використовують мнемокоди – умовні позначення команд, які, як-правило, формуються набором з латинських букв, взятих з назви команди.

Записи команд з використанням мнемокоду мають структуру X..X d, s, де X..X – мнемокод команди, d – адреса призначення (куди поміщається операнд; в двооперандних командах одночасно є адресою другого операнду), s – адреса джерела (операнд або адреса операнду, над яким виконується операція; в двооперандній команді – перший операнд або його адреса).

Приклади запису команд з використанням мнемокодів:

CLI – команда, що не містить операнду;

INC A; MOV AX, DX – команди з одним операндом;

ADD AX, DX – команда з двома операндами.

Особливості виконання команди повернення з підпрограми RET.

Команда RET – це команда повернення з підпрограми в основну програму при виконанні якої програмний лічильник (PC) зі стеку повертається адреса наступної команди основної програми. Таким чином виконуються слідуючі дії:

PC [(SP)(SP)+1]

SP (SP)+2

Використання підпрограм у програмуванні. Реалізація звернення до підпрограми у МПС на МП.

Якщо певна група команд повторюється багато разів у різних точках програми, то її можна оформити у виді підпрограми. Таким чином можна часто значно зменшити об’єм області пам’яті, в якій розміщена програма.

Звернення до підпрограми відбувається за допомогою команд безумовного (CALL) та умовних (CNZ, CZ, CNC, CC, CPO, CPE, CP, CM викликів підпрограми

При виконанні команди безумовного виклику підпрограми вміст програмного лічильника, який представляє собою адресу наступної за порядком команди основної програми заноситься в дві сусідні комірки стекової пам’яті, а замість нього в програмний лічильник заноситься початкова адреса підпрограми, тобто виконуються наступні дії:

[(SP) -1] [ (SP) - 2] ← (PC);

SP ← (SP) – 2;

PC ← <В3 В2>.

П

Структура коду Мнемоніка

команди

11001101

CALL 092D

CALL 092D

00101101

00001001

риклад запису команди безумовного виклику підпрограми з початковою адресою 092D:

Підпрограма закінчується командою повернення з підпрограми, яка повертає мікропроцесор до основної програми. При виконанні команди безумовного повернення з підпрограми (RET) в програмний лічильник повертається зі стеку адреса наступної команди основної програми, яка була туди занесена командою виклику підпрограми (CALL), тобто виконуються дії:

(PC) ← [(SP)] [(SP) + 1];

SP ← (SP) + 2;

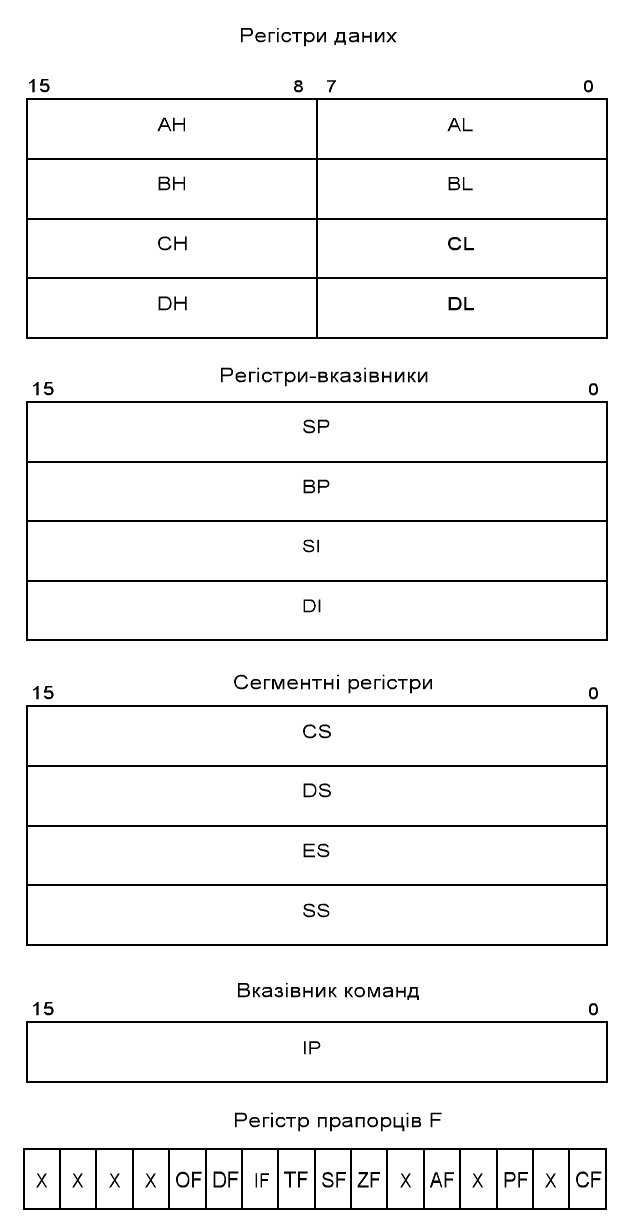

Регістри загального призначення (РЗП) операційного пристрою МП і8086.

Програмна модель МП і8086.

П рограмною

моделлю

МП називається сукупність програмно

доступних регістрів, тобто тих регістрів

вміст яких можна зчитати або змінити

за допомогою команд. Програмну модель

МП і8086 складають регістри загального

призначення (РЗП), сегментні регістри,

вказівник команд і регістр прапорців.

Програмна модель МП і8086 представлена

на рис.9.1.

рограмною

моделлю

МП називається сукупність програмно

доступних регістрів, тобто тих регістрів

вміст яких можна зчитати або змінити

за допомогою команд. Програмну модель

МП і8086 складають регістри загального

призначення (РЗП), сегментні регістри,

вказівник команд і регістр прапорців.

Програмна модель МП і8086 представлена

на рис.9.1.

Рис.9.1 Програмна модель МП і8086

Особливості команд передачі керування в МП і8086.

Команди передачі керування зазвичай змінюють вміст вказівника команд IP, а деякі і вміст регістра сегмента кодів CS. За допомогою цих команд можна змінити послідовність виконання команд у програмі, оскільки регістр CS містить базову адресу поточного сегмента кодів, з якого вибираються команди, а регістр IP - адресу, яка задає зміщення команди відносно початку сегмента кодів. Після виконання команди передачі керування пристрій керування МП, використовуючи новий вміст регістрів CS і IP, вибирає з пам'яті наступну команду. У такий спосіб виконується переоформлення черги команд, які надходять у блок операційного пристрою.

До цієї групи команд належать: команди безумовного й умовного переходів; команди викликів підпрограм і повернень з підпрограм; команди циклів; команди переривань.

Приклад. Виконати безумовний міжсегментний перехід. За командою JMP FAR LABEL

(JuMP FAR - стрибок далеко) здійснюється перехід до виконання команд, першу з яких позначено міткою LABEL. Ця мітка знаходиться в межах усієї пам'яті ємністю 1 Мбайт. При міжсегментному переході змінюється як вміст програмного лічильника IP, так і вміст сегментного регістра кодів CS згідно з міткою LABEL.

Вибір портів або регістра керуючого слова ППІ КР580ВВ55.

Типи машинних циклів.

В залежності від конкретної інформації в “слові стану” розрізняють 10 типів машинних циклів. Цикл m1 є завжди першим типом – вибір першого байту команди.