- •Понятие конвейерной обработки. Организация конвейера.

- •Классификация конвейерных устройств.

- •Показатели эффективности конвейеров.

- •Конвейерное выполнение команд. Командный конвейер.

- •Организация скалярного конвейерного процессора.

- •Конфликты в командном конвейере.

- •Структурные конфликты и способы их минимизации.

- •Совершенствование структуры процессора путем введения буферных зу.

- •Конфликты по данным и способы их минимизации.

- •Конфликты по управлению и способы их минимизации.

- •Предсказание переходов.

- •Суперконвейерные процессоры.

- •Сisc-архитектура.

- •13 Обработка сложных команд

- •15 Risc-архитектура.

- •16 Суперскалярный параллелизм. Суперскалярная обработка.

- •Cуперскалярные процессоры.

- •18Процессоры с vliw архитектурой.

- •19.Процессоры с epic-архитектурой.

19.Процессоры с epic-архитектурой.

Дальнейшим развитием идеи VLIW стала новая архитектура IA-64 — совместная разработка фирм Intel и Hewlett-Packard (IA - это аббревиатура от Intel Architecture). В IA-64 реализован новый подход, известный как вычисления с явным па-раллелизмом команд (EPIC, Explicitly Parallel Instruction Computing) и являющийся усовершенствованным вариантом технологии VLIW. Первым представителем данной стратегии стал микропроцессор Itanium компании Intel. Корпорация Hewlett-Packard также реализует данный подход в своих разработках.

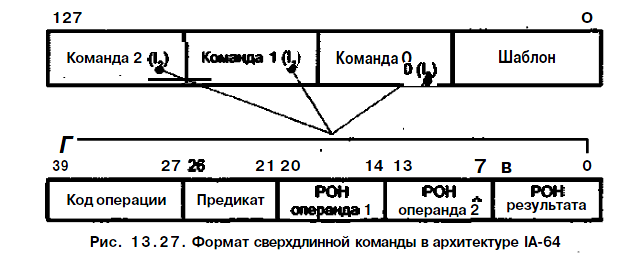

В архитектуре IA-64 предполагается наличие в процессоре 128 64-разрядных регистров общего назначения (РОН) и 128 80-разрядных регистров с плавающей запятой. Кроме того, процессор IA-64 содержит 64 однобитовых регистра предикатов. Формат команд в архитектуре IA-64 показан на рис. 13.27.

Команды упаковываются (группируются) компилятором в сверхдлинную команду — связку (bundle) длиною в 128 разрядов. Связка содержит три команды и шаблон, в котором указываются зависимости между командами (можно ли с командой I0 запустить параллельно I1 или же I1 должна выполниться только после Iо), а также между другими связками (можно ли с командой I2 из связки So запустить параллельно команду I3 из связки S1).

Перечислим все варианты составления связки из трех команд:

- I0 || I1 || 12 — все команды исполняются параллельно;

- Iо & I1 || I г — сначала I0, затем исполняются параллельно I1 и I2;

- I0 || I 1 & I2 - параллельно обрабатываются I0 и I1 после них - I2;

- I0& I1 & I2 — команды исполняются в последовательности I0,I1, I2.

Одна связка, состоящая из трех команд, соответствует набору из трех функциональных блоков процессора. Процессоры IA-64 могут содержать разное количество таких блоков, оставаясь при этом совместимыми по коду. Благодаря тому что в шаблоне указана зависимость и между связками, процессору с N одинаковыми блоками из трех ФБ будет соответствовать сверхдлинная команда из N х 3 команд (Nсвязок). Тем самым обеспечивается масштабируемость IA-64.

Поле каждой из трех команд в связке, в свою очередь, состоит из пяти полей:

- 13-разрядного поля кода операции;

- 6-разрядного поля предикатов, хранящего номер одного из 64 регистров преди

ката;

- 7-разрядного поля первого операнда (первого источника), где указывается но

мер регистра общего назначения или регистра с плавающей запятой, в котором содержится первый операнд;

- 7-разрядного поля второго операнда (второго источника), где указывается но

мер регистра общего назначения или регистра с плавающей запятой, в котором содержится второй операнд;

- 7-разрядного поля результата (приемника), где указывается номер регистра

общего назначения или регистра с плавающей запятой, куда должен быть занесен результат выполнения команды.

Следует пояснить роль подполя предикатов. Предикация - это способ обработки условных ветвлений. Суть в том, что еще компилятор указывает, что обе ветви выполняются на процессоре параллельно, ведь EPIC-процессоры должны иметь много функциональных блоков.

Если в исходной программе встречается условное ветвление (по статистике — через каждые шесть команд), то команды из разных ветвей помечаются разными регистрами предиката (команды имеют для этого соответствующие поля), далее они выполняются совместно, но их результаты не записываются, пока значения регистров предиката (РП) не определены. Когда, наконец, вычисляется условие ветвления, РП, соответствующий «правильной» ветви, устанавливается в 1, а другой - в 0. Перед записью результатов процессор проверяет поле предиката и записывает результаты только тех команд, поле предиката которых указывает на РП с единичным значением.

Предикаты формируются как результат сравнения значений, хранящихся в двух регистрах. Результат сравнения («Истина» или «Ложь») заносится в один из РП,

но одновременно с этим во второй РП записывается инверсное значение полученного результата. Такой механизм позволяет процессору более эффективно выполнять конструкции типа I F - T H E N-E L S E .

Логика выдачи команд на исполнение сложнее, чем в традиционных процессорах типа VLIW, но намного проще, чем у суперскалярных процессоров с неупорядоченной выдачей. По мнению специалистов Intel и HP, концепция EPIC, сохраняя все достоинства архитектурной организации VLIW, свободна от большинства ее недостатков. Особенностями архитектуры EPIC являются:

- большое количество регистров;

- масштабируемость архитектуры до большого количества функциональных бло

ков. Это свойство представители компаний Intel и HP называют наследственно масштабируемой системой команд (Inherently Scaleable Instruction Set);

- явный параллелизм в машинном коде. Поиск зависимостей между командами

осуществляет не процессор, а компилятор;

- предикация — команды из разных ветвей условного предложения снабжаются

полями предикатов (полями условий) и запускаются параллельно;

- предварительная загрузка — данные из медленной основной памяти загружа

ются заранее.

Общий итог обзора технологии VLIW можно сформулировать следующим образом.

Преимущества. Использование компилятора позволяет устранить зависимости между командами до того, как они будут реально выполняться, в отличие от суперскалярных процессоров, где такие зависимости приходится обнаруживать и устранять "на лету". Отсутствие зависимостей между командами в коде, сформированном компилятором, ведет к упрощению аппаратных средств процессора и за счет этого к существенному подъему его быстродействия. Наличие множества функциональных блоков дает возможность выполнять несколько команд параллельно.

Недостатки. Требуется новое поколение компиляторов, способных проанализировать программу, найти в ней независимые команды, связать такие команды в строки длиной от 256 до 1024 бит, обеспечить их параллельное выполнение. Компилятор должен учитывать конкретные детали аппаратных средств. При определенных ситуациях программа оказывается недостаточно гибкой.