- •7.091501 – Комп’ютерні системи та мережі

- •7.091503 – Спеціалізовані комп’ютерні системи

- •7.091501 – Комп’ютерні системи та мережі

- •7.091503 – Спеціалізовані комп’ютерні системи

- •2. Надійність і відмовостійкість

- •3. Масштабованість

- •4. Сумісність і мобільність програмного забезпечення

- •5. Класифікація комп'ютерів по галузям застосування Персональні комп'ютери та робочі станції

- •Сервери

- •Мейнфрейми

- •Кластерні архітектури

- •Контрольні запитання

- •Тести tpc

- •2. Тест tpc-a

- •3. Тест tpc-b

- •4. Тест tpc-c

- •5. Майбутні тести tpc

- •2. Архітектура системи команд. Класифікація процесорів (cisc і risc)

- •3. Методи адресації та типи даних Методи адресації

- •4. Типи команд

- •5. Команди керування потоком команд

- •6. Типи й розміри операндів

- •2. Найпростіша організація конвеєра й оцінка його продуктивності

- •3. Структурні конфлікти й способи їхньої мінімізації

- •4. Конфлікти за даними, зупинка конвеєра й реалізація механізму обходів

- •5. Класифікація конфліктів за даними

- •6. Конфлікти за даними, що призводять до призупинки конвеєра

- •7. Методика планування компілятора для усунення конфліктів за даними

- •Контрольні запитання

- •2. Зниження втрат на виконання команд умовного переходу

- •Метод вичікування

- •Метод повернення

- •Затримані переходи

- •3. Статичне прогнозування умовних переходів: використання технології компіляторів

- •2. Обробка багатотактних операцій і механізми обходів у довгих конвеєрах

- •3. Конфлікти й прискорені пересилання в довгих конвеєрах

- •4. Підтримка точних переривань

- •Контрольні запитання

- •2. Паралелізм рівня команд: залежності й конфлікти за даними

- •Залежності

- •3. Паралелізм рівня циклу: концепції та методи

- •4. Основи планування завантаження конвеєра й розгортання циклів

- •Контрольні запитання

- •2. Динамічна оптимізація із централізованою схемою виявлення конфліктів

- •2. Подальше зменшення зупинок по керуванню: буфера цільових адрес переходів

- •Контрольні запитання

- •Процесор з архітектурою 80x86 і Pentium.

- •Особливості процесорів з архітектурою spark компанії Sun Microsystems.

- •Процесори pa-risc компанії Newlett-Packard

- •2.Особливості процесорів з архітектурою sparc компанії Sun Microsystems

- •Процесори pa-risc компанії Hewlett-Packard

- •Контрольні запитання

- •Процесор mc88110 компанії Motorola.

- •Особливості архітектури mips компанії mips Technology.

- •Особливості архітектури Alpha компанії dec.

- •Особливості архітектури power компанії ibm і power pc компанії Motorola, Apple і ibm.

- •2.Особливості архітектури mips компанії mips Technology

- •3.Особливості архітектури Alpha компанії dec

- •4.Особливості архітектури power компанії ibm і PowerPc компаній Motorola, Apple і ibm

- •Архітектура power

- •Еволюція архітектури power у напрямку архітектури PowerPc

- •Процесор PowerPc 603

- •Контрольні запитання

- •Термінологія в області паралельної обробки .

- •Питання створення програмного забезпечення.

- •Ахітектура паралельної обробки.

- •2.Питання створення програмного забезпечення.

- •1) Язикові розширення.

- •2) Розширення компіляторів.

- •3) Додавання нового язикового рівня.

- •4) Нова мова.

- •3.Архітектура паралельної обробки.

- •4.Елементи теорії конкурентних процесів. Події та процеси

- •Особливості мов конкурентного програмування

- •Моделі конкурентних процесів

- •Взаємодія процесів, синхронізація й передача даних

- •2. Внутрішня архітектура трансп’ютера

- •3. Послідовна обробка

- •Регістри трансп’ютера

- •4. Інструкції

- •Безпосередні функції

- •Непрямі функції

- •Ефективність кодування

- •5. Підтримка паралелізму

- •6. Зв'язок

- •Лінії зв'язку

- •7. Таймер

- •8. Альтернативне виконання

- •9. Інструкції із плаваючою крапкою

- •Контрольні запитання

- •2. Найпростіші процеси-примітиви

- •3. Послідовні процеси-композиції

- •4. Паралельні процеси

- •5. Канали зв'язку

- •6. Конструктор альтернативного процесу

- •7. Описи

- •8. Масиви

- •9. Оголошення процесів

- •10. Цикли і масиви процесів

- •Контрольні запитання

- •2. Структури програмування

- •Прості паралельні процеси

- •Синхронізація за допомогою керуючих сигналів

- •3. Мовні засоби для програмування в реальному масштабі часу

- •4. Використання мови оккам для рішення завдань системного програмування

- •Контрольні запитання

- •Рекомендована література

Затримані переходи

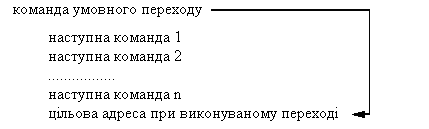

Четверта схема, що використається в деяких машинах називається "затриманим переходом". У затриманому переході такт виконання із затримкою переходу довжиною n є:

Команди 1 - n перебувають у слотах (тимчасових інтервалах) затриманого переходу. Завдання програмного забезпечення полягає в тім, щоб зробити команди, що випливають за командою переходу, дійсними й корисними. Апаратура гарантує реальне виконання цих команд перед виконанням властивого переходу. Тут використаються кілька прийомів оптимізації.

На рис. 3, а показані три випадки, при яких може плануватися затриманий перехід. У верхній частині малюнка для кожного випадку показана вихідна послідовність команд, а в нижній частині - послідовність команд, отримана в результаті планування. У випадку (а) слот затримки заповнюється незалежною командою, що перебуває перед командою умовного переходу. Це найкращий вибір. Стратегії (b) і (c) використовуються, якщо застосування стратегії (a) неможливо.

У послідовностях команд для випадків (b) і (c) використання вмісту регістра R1 як умова переходу перешкоджає переміщенню команди ADD (яка записує результат у регістр R1) за команду переходу. У випадку (b) слот затримки заповнюється командою, що перебуває по цільовій адресі команди переходу. Звичайно таку команду доводиться копіювати, оскільки до неї можливі обіги й з інших частин програми. Стратегії (b) віддається перевага, коли з високою ймовірністю перехід є виконуваним, наприклад, якщо це перехід на початок циклу.

Нарешті, слот затримки може заповнюватися командою, що перебуває між командою невиконуваного переходу й командою, що перебуває по цільовій адресі, як у випадку (c). Щоб подібна оптимізація була законної, необхідно, щоб можна було все-таки виконати команду SUB, якщо перехід піде не по прогнозованому напрямку. При цьому ми припускаємо, що команда SUB виконає непотрібну роботу, але вся програма при цьому буде виконуватися коректно. Це, наприклад, може бути у випадку, якщо регістр R4 використовується тільки для тимчасового зберігання проміжних результатів обчислень, коли перехід виконується не по прогнозованому напрямку.

Рис. 3 а. Вимоги до переставляэмих команд при плануванні затриманого переходу

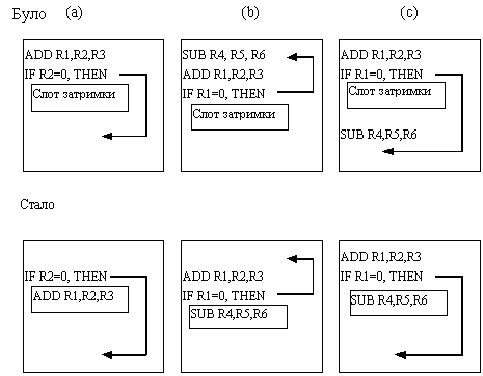

Рис. 3, б показує різні обмеження для всіх цих схем планування умовних переходів, а також ситуації, у яких вони дають виграш. Компілятор повинен дотримувати вимог при підборі належної команди для заповнення слота затримки. Якщо така команда не знайдена, слот затримки повинен заповнюватися порожньою операцією.

Розглянутий випадок |

Вимоги |

Коли збільшується продуктивність |

(a) |

Команда умовного переходу не повинна залежати від переставляє команды |

Завжди |

(b) |

Виконання команды, що переставляється, повинно бути коректним, навіть якщо перехід не виконується Може знадобитися копіювання команди |

Коли перехід виконується. Може збільшувати розмір програми у випадку копіювання команди |

(c) |

Виконання команды, що переставляється, повинно бути коректним, навіть якщо перехід виконується |

Коли перехід не виконується |

Рис. 3, б

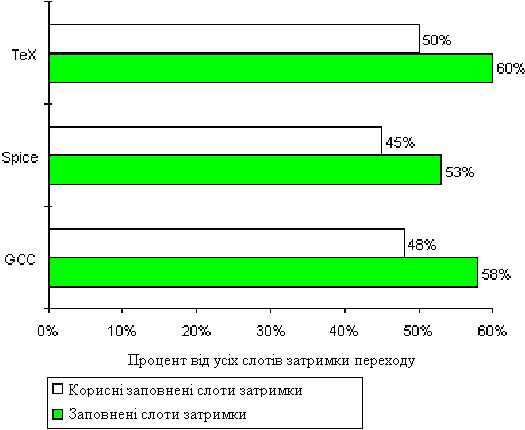

Планування затриманих переходів ускладнюється (1) наявністю обмежень на команди, розміщення яких планується в слотах затримки й (2) необхідністю передбачати під час компіляції, чи буде умовний перехід виконуваним чи ні. Рис. 4 дає загальне подання про ефективність планування переходів для найпростішого конвеєра з одним слотом затримки переходу при використанні простого алгоритму планування. Він показує, що більше половини слотів затримки переходів виявляються заповненими. При цьому майже 80% заповнених слотов виявляються корисними для виконання програми. Це може здатися дивним, оскільки умовні переходи є виконуваними приблизно в 53% випадків. Високий відсоток використання заповнених слотов пояснюється тим, що приблизно половина з них заповнюється командами, що передували команді умовного переходу (стратегія (a)), виконання яких необхідно незалежно від того, чи виконується перехід, чи ні.

Рис. 4. Частота заповнення одного слота затримки умовного переходу

Є невеликі додаткові витрати апаратур на реалізацію затриманих переходів. Через затриманий ефект умовних переходів, для коректного відновлення стану у випадку появи переривання потрібні кілька лічильників команд (один плюс довжина затримки).