- •Курс: «Компьютерные технологии в инженерных расчетах»

- •Введение (Микляев а.П.)

- •Соперничество двух платформ

- •История развития

- •2. Аппаратное обеспечение компьютера (Симонович с.)

- •2.1. Базовая аппаратная конфигурация

- •2.2. Системный блок. Состав системного блока

- •2.3. Микропроцессор. Основные понятия

- •Система команд процессора

- •2.3.1. Процессор Pentium

- •2.3.2. Процессор Pentium III

- •2.4. Современные процессоры

- •Бюджетные процессоры amd Sempron, Intel Celeron-d

- •Процессоры линейки Wolfdale: Core 2 Duo e8500, e8400 и e8200

- •Слева – Wolfdale, справа – Conroe

- •Новые процессоры

- •Характеристика двухядерных процессоров

- •Цены на двухядерные процессоры:

- •Процессоры amd с архитектурой нового поколения появятся в 2011 году

- •Intel Quad-Core Xeon 7300 – новейшие четырёхядерные процессоры

- •Оперативная память

- •2.6. Стандарт pci (Peripheral Component Interconnect)

- •2.7. Быстродействие процессора и памяти

- •2.9. Чипсет (Chipset)

- •2.10. Жесткий диск

- •Что такое кластер?

- •2.12. Гибкие диски

- •2.13. Накопители на компакт-дисках

- •2.14. Видеосистема

- •2.15. Звуковая карта

- •3. Запуск компьютера и настройка запуска (Симонович)

- •3.1. Тест при включении

- •3.2. Определение оперативной конфигурации

- •3.3. Запуск операционной системы

- •3.4. Настройка запуска

2.6. Стандарт pci (Peripheral Component Interconnect)

Шина PCI была разработана Intel. Фирма Intel имеет отношение не только к процессорам, но и к компонентам материнских плат, в частности, к созданию Ethernet (локальной сети на основе протокола CSMA-CD).

Шина PCI имеет 64-разрядный интерфейс, работает под частотой 33 МГц и за каждый такт может переносить 32 бита данных (4 байта).

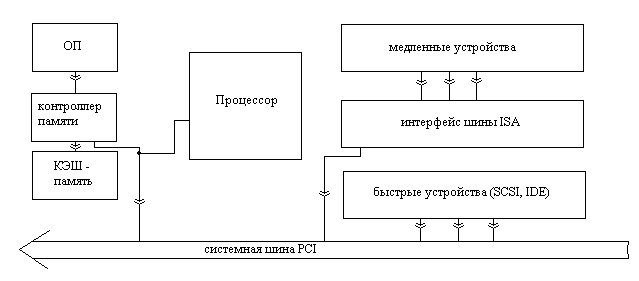

Шина PCI объединяет шину процессор/память и шину ввода-вывода. Чип интерфейса PCI может поддерживать видео-адаптер, два контроллера диска EIDE и две внешних платы адаптера. На рис. 2.1. приведена архитектура шины PCI.

Рис. 2.1. Архитектура шины PCI:

2.7. Быстродействие процессора и памяти

При работе компьютер выполняет инструкции. Основные инструкции – сложение, вычитание и сравнение двух чисел на «< - >». Остальные инструкции – вспомогательные.

Рассмотрим, к примеру, автоматическое исправление ошибки в режиме авто замены в Worde. Если использовать ввел «дял», то компьютер распознает ошибку и изменяет слово на «для». При чем здесь числа? Каждая клавиша символа, которую нажимает пользователь, включая клавишу «пробел», передает на компьютер некоторый код (Scan Code). В системе кодирования ASCII, широко применяемой в компьютерах, символ пробела имеет код 32, «а» - 224, «я» (малая) –255. Так что компьютер видит «дял» как последовательность 32 288 255 235. текстовый процессор в режиме автозамены запрограммирован проверить эту последовательность и, в случае обнаружения ее, поменять местами 255 и 235. чип центрального процессора не знает ничего относительно проверки правописания, но зато он может очень быстро и точно обрабатывать числа.

С каждой инструкцией в РС, помимо «+» или «*», связано выполнение ряда дополнительных операций. В начале компьютер должен найти следующую инструкцию в памяти и передать ее центральному процессору. Эта инструкция закодирована в виде некоторого числа. Компьютер должен декодировать это число и определить операцию (например, ADD для сложения) и размер данных (допустим, 16 бит). Затем принимается и декодируется дополнительная информация, описывающая расположение данных в памяти. Наконец, число добавляется к текущему итогу. Наибольшее время требуется для декодирования инструкций и нахождения данных.

процессор 386 для сложения двоичных чисел требуется минимум 6 тактов;

486 – за 2 такта;

Pentium за 1 такт;

Pentium II/III – за один цикл сложить 3 числа.

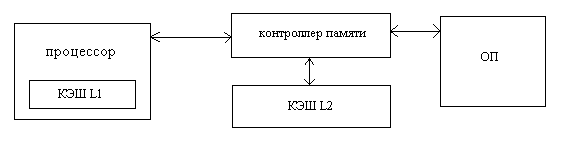

Центральный процессор не знает как быстро работает память, а память ничего не знает относительно задержек в материнской плате. Вопросы синхронизации решаются контроллером памяти на материнской плате. На рис. 2.2. представлена конфигурация построения память-процессор на материнской плате с процессором Pentium.

Рис. 2.2.

Контроллер конфигурируется таким образом, чтобы сгенерировать для процессора достаточно состояний ожидания для замедления каждого из обращений к памяти, с учетом времени на ответ памяти и перемещение запроса и данных. Если материнская плата сконфигурирована под память 60 нс, таким образом, применение памяти DRAM на 50 нс не приведет ни к какому росту производительности системы.

2.8. Кэш-память

Кэш – высокоскоростная область памяти, в которой хранятся копии недавно использованных данных из основной памяти. Кэш-памятью управляет специальное устройство – контроллер, который, анализируя выполняемую программу, пытается предвидеть, какие данные и команды вероятнее всего понадобятся в ближайшее время процессору, и подкачивает их в кэш-память. При этом возможны как «попадания», так и «промахи». В случае попадания, то есть, если в кэш подкачены нужные данные, извлечение их из памяти происходит без задержки. Если же требуемая информация в кэше отсутствует, то процессор считывает ее непосредственно из оперативной памяти. Соотношение числа попаданий и промахов определяет эффективность кэширования.

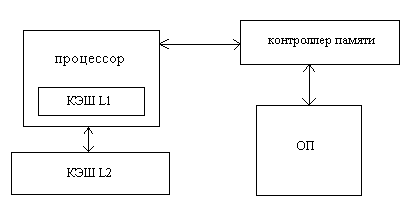

Современный РС имеет 2 уровня кэша. Кэш L1 расположен внутри чипа процессора (в Pentium III – 64 Кбайт). Кэш L2 (128К – 2048К) впаян в плату матери из чипов быстрой статической памяти SRAM.

Pentium II и III поставляются в корпусе, который объединяет чип процессора с интегрированным набором микросхем SRAM кэша L2. Процессор знает об этом Кэше и управляет им сам, точно также, как он управляет КЭШем L1 (рис. 2.3).

Рис. 2.3.