- •Логічні ел-ти ттл/ттлш: базовий логічний елт. Аналіз амплітудно-передаточної (амплітудної або статичної) хар-ки. Статичні та динамічні параметри.

- •1.2 Логічни ел-ти з трьома станами виходу. Принцип дії. Впорядкування роботи декількох ел-тів на одну спільну лінію інтерфейсу (магістральні інтерфейси)

- •1.3 Логічн ел-ти моп/кмоп: базовий лог ел-т. Аналіз амплітудно-передаточної (амплітудної або статичної) хар-ки. Статичні та динамічні параметри.

- •1.4 Тригери: класифікація та коротка характеристика різних типів тригерів. Особливості схемотехнічної реалізації та функціонування.

- •1.5 Регістри: призначення та класифікація. Паралельні та послідовні регістри. Особливості схемотехнічної реалізації та функціонування.

- •1.6 Лічильники: призначення та класифікація. Асинхронні лічильники. Особливості схемотехнічної реалізації та функціонування.

- •1.7. Синхронні лічильники: особливості схемотехнічної реалізації та функціонування.

- •1.8. Дешифратори: визначення, класифікація, способи побудови та функціонування. Линейный или одноступенчатый дешифратор.

- •1.9 Шифратори. Визначення, принципи побудови та особливості функціонування. Клавіатурні, пріоритетні шифратори, кодоперетворювачі.

- •1.10. Мультиплексори: визначення, принципи побудови та функціонування.

- •1.11. Демультиплексори: визначення, принципи побудови та функціонування.

- •1.12. Суматори комбінаційного типу: призначення, класифікація та принципи побудови.

- •1.13. Накопичуючі суматори та особливості їхнього функціонування.

- •1.14 Моделювання аналогових та цифрових схем за допомогою пакетів ewb і micro-cap: послідовність дій при моделюванні. Одержання та оформлення результатів.

- •Мультиметр

- •Генератор слов

- •Логический анализатор

- •Логический преобразователь

- •Осциллограф.

- •Разработка схем цифровых устройств

- •5.1. Вывод элементов схем на рабочую поверхность

- •Монтаж схем

- •1.15 Особливості та принципи побудови пристроїв з використанням «жорсткої» та «програмованої» логіки.

- •1.16 Основні функції алгебри логіки та логічні елементи для їх реалізації. Закони алгебри логіки.

- •1.17 Синтез логічних схем в базисах (і, або, ні), і-ні, або-ні.

- •1. Абстрактный синтез

- •2. Схемный синтез

- •1.18 Типи даних та структури команд в мп intel (на прикладi 486)

- •1.19. Архітектура системного інтерфейсу сучасних пк. Призначення компонент. Режими передачі інформації по системним шинам.

- •1.20. Розподілення системних ресурсів між компонентами пк. Технологія PnP та її реалізація в шинах pci та isa/eisa.

- •1.21. Засоби кешування мп. Призначення та характеристики. Типи кеш-пам'яті. Режими роботи при читанні/записуванні інформації.

- •1.22. Призначення та організація системної пам'яті. Фізична організація мікросхем пзп, статичного та динамічного озп. Типи динамічної пам’яті (fpm, edo, bedo, sdram).

- •1.23. Архітектура та принцип роботи годинника реального часу rtc та cmos пам'яті. Можливості програмування.

- •1.24. Архітектура системного таймера та призначення каналів таймера. Режими роботи каналів таймера. Можливості програмування.

- •1.25. Архітектура та організація підсистеми dma (кпдп) в пк. Керуюча інформація та програмування.

- •1.26. Організація переривань в пк, пріоритети при обробці переривань. Режими роботи та програмування.

- •1.27. Архітектура та принцип роботи підсистеми клавіатури. Призначення компонент. Та можливості програмування.

- •1.28. Архітектура відеосистеми пк. Управління відеосистемою. Режими. Структура відеопам'яті.

- •1.29. Логічна організація дискових накопичувачів зовнішньої пам'яті. Основні області (boot, fat, root, data area).

- •1.30. Архітектура та управління контролером нжмд. Структура команд.

- •1.31. Архітектура та управління com-портом. Призначення регістрів.

- •1.32. Архітектура та управління lpt – портом в режимах ecp epp.

- •1.33. Архітектура scsi шини.

- •1.34. Архітектура usb шини.

- •2.1 Методи відокремлення каналів у багатоканальних системах передачі даних.

- •2.2 Перетворення, кодування, модуляція. Призначення цих процесів при передаванні даних. Теорема котєльнікова (найквіста).

- •2.3 Модуляція. Різновиди модуляції. Швидкість маніпуляції.

- •2.4 Кількість інформації. Ентропія. Надмірність.

- •2.5 Класифікація завад. Властивості флуктуаційних завад.

- •2.6 Амплітудна маніпуляція. Модулятор та детектор. Спектр сигналу та потрібна смуга перепускання каналу.

- •2.7 Частотна маніпуляція. Модулятор, детектор.

- •Фазова маніпуляція. Спектр сигналу та потрібна смуга перепускання каналу. Відносна фазова маніпуляція та детектування.

- •2.9. Різновиди фазової маніпуляції: двфм, твфм, кам.

- •2.11. Класифікація похибкостійких кодів. Вирази для розрахунку віроємності невиявленої помилки для кодів із сталою вагою та для кодів з контролем за паритетом

- •2.12. Первичные коды и способы расширения кодировочной таблицы. Esc-последовательности принтеров.

- •2.13. Причины использования модуляции при передаче данных. Разновидности модуляции и необходимые полосы пропускания линий связи.

- •2.14. Геометрическая интерпретация сигналов и помех. Идеальный приёмник котельникова и другие варианты построения приёмников двоичных сигналов.

- •2.15. Синхронизация в аппаратуре передачи данных и в устройствах считывания магнитных записей, способы кодирования, которые повышают надёжность синхронизации битов.

- •Параллельный метод

- •Последовательный метод

- •2.16. Модемы как периферийные устройства. Система команд хейза. Модемы серии mnp. Особенности модемов классов mnp-5,7,10. Команды модема.

- •2.17. Методы магнитного записывания информации и их применение.

- •2.18. Частотный и модифицированный частотный методы записи информации. Формат сектора на гибком диске. Способы позиционирования головок в дисковых устройствах магнитного записывания информации.

- •2.19. Елементи формату сектору, що забезпечують бітову та байтову синхронізацію під час зчитування інформації з гнучких дисків.

- •2.22. Cтандарт багаторівневого керування мережею (модель взаімодії відкритих систем – open system interconnection, osi). Поняття протоколу, інтерфейсу, стеку протоколів.

- •2.24. Протоколи канального рівня: асинхронні, синхронні (символьно-орієнтовані, біт-орієнтовані). Протоколи з встановленням з’єднання та без встановлення.

- •Синхронные символьно-ориентированные и бит-ориентированные протоколы

- •Передача с установлением соединения и без установления соединения

- •2.25 Локальна мережа ethernet. Топології, стандарти, доступ до мережі, структура кадру, розрахунок продуктивності, колізії, домен колізій та організація роботи мережі.

- •Максимальная производительность сети Ethernet

- •Форматы кадров технологии Ethernet

- •Глобальные связи на основе сетей с коммутацией каналов

- •Isdn - сети с интегральными услугами

- •2.28.Протокол ip та його функції. Структура ip-пакету та його параметри. Маршрутизація в ip-мережах. Фрагментація ip–пакетів. Зборка фрагментів.

- •Источники и типы записей в таблице маршрутизации:

- •Фрагментация ip-пакетов

- •2.29. Тенденції розвитку мікропроцесорної техніки. Структура та режими функціонування сучасних мікропроцесорів.

- •2.30. На базі існуючих технічних рішень провести розробку структурної схеми мікропроцесора.

- •2.31. Сегментація пам’яті в захищеному режимі. Розробка дескрипторів сегментів. Формування лінійної адреси при звертанні до пам’яті.

- •2.32. Обробка переривань в захищеному режимі. Види виключень. Формування дескриптивної таблиці переривань.

- •5.9. Приклад обробки пеpеpивань в захищеному режимi

- •5.9.1. Опис програми p_int

- •2. 34 Захист пам’яті. Рівні привілеїв. Особливості захисту сегментів даних, стеку, коду та пристроїв введення/виведення.

- •2.35. Апаратні засоби підтримки багатозадачної роботи мікропроцесора. Структура аблиці стану задач. Алгоритми та механізми переключення задач.

- •2.36.Алгоритми та механізми переключення задач

- •2.37. Сторінкова організація пам’яті. Розробка покажчиків таблиць та сторінок формування фізичної адреси для 4к-, 2м- і 4м-байтних сторінок.

- •3.1. Засоби захисту носіїв інформації. Записування за межами поля форматування. Зміна довжини сектора. Чергування секторів.

- •3.5. Процеси. Контекст процесу. Стани процесів та переходи між ними. Системні виклики для забезпечення життєвого циклу процесу.

- •3.6. Керування пам’яттю. Основні задачі. Моделі пам’яті. Системні виклики для роботи з пам’яттю.

- •3.7. Операційні системи. Склад ос. Вимоги до сучасних ос. Архітектурні напрямки побудови ос.

- •Монолитные системы

- •Многоуровневые системы

- •Модель клиент-сервер и микроядра

- •3.8. Монопольні ресурси. Проблема тупиків. Дисципліни розподілу ресурсів. Пошук тупиків та їх знищення.

- •3.9. Паралельне виконання процесів. Формулювання задачі «виробники-споживачі» та методи її вирішення.

- •3.10. Засоби взаємодії процесів. Порівняльна характеристика базових механізмів ipc.

- •3. 12 Субд. Основні функції. Види субд.

- •3.13 Реляційні бази даних. Основні поняття, властивості відношень, модель даних, реляційні операції і обчислення. Базовые понятия реляционных баз данных.

- •1. Тип данных

- •2. Домен

- •3. Схема отношения, схема базы данных

- •4. Кортеж, отношение

- •1.Отсутствие кортежей-дубликатов

- •2. Отсутствие упорядоченности кортежей

- •3. Отсутствие упорядоченности атрибутов

- •3.14.Колірні простори rgb та cmyk. Сфера застосування та та причини їх розходження. Одержання кольорів одного простору через значення кольорів іншого.

- •3.16 Провести порівняння технологій взаємодії процесів у локальній мережі. Поштові скриньки. Іменовані канали. Вилучений виклик процедур. Гнізда.

- •3.17 Провести порівняння методів побудови багаторівневих програмних засобів. Динамічні бібліотеки. Com і activex. Провайдери. Служби. Драйвера.

- •3.18 Загальні вимоги і архітектури інтерфейсу користувача . Можливості, переваги і недоліки діалогових, однодокументних і багатодокументних прикладень.

- •3.19 Типи даних та структури команд в мп Intel.

- •3.20 Організація переривань в пк, пріоритети при обробці переривань. Режими роботи та програмування.

- •3.21 Архітектура відеосистеми пк. Управління відеосистемою.

- •3.22 Режими відеосистеми. Структура відеопам'яті.

- •3.23 Логічна організація дискових накопичувачів зовнішньої пам'яті. Основні області (boot, fat, root, data area).

- •3.24 Двійкова логіка. Булеві функції однієї та двох змінних. Кількість булевих функцій n-змінних. Суперпозиція булевих функцій.

- •3.25. Тестова діагностика мереж пк. Утиліта ping: організація роботи, типи повідомлень. Поясніть можливий приклад роботи утиліти.

- •Технические характеристики системной платы

- •3.27. Відеосистема пк. Основні експлуатаційні характеристики. Отримання інформації про відеосистему пк та результатів тестування з допомогою програми класу checkit. Пояснити можливі результати.

- •Возможные тесты видеосистемы:

- •3.28. Реалізація анімації зображення в web-сторінках з використанням додаткових графічних файлів і без них (тільки текстом html-файлу).

- •3.29. Колір – як засіб керування психікою і поведінкою людини. Реалізація колірної гармонії у графічному зображенні.

- •Понятие цветовой гармонии :

- •3.30. Спектральна характеристика людського ока і причина використання rgb системи в моніторах. Технічні і психофізіологічні обмеження відтворення кольору.

- •3.31 Реляційні бази даних. Транзакції та цілісність баз даних. Ізольованість користувачів. Журнал змін. Транзакции и целостность баз данных

- •3.32 Мова запитів sql. Команда select і структура запитів на вибірку.

- •3.33 Мова запитів sql. Робота з записами і таблицями. Додавання, видалення, модифікація.

- •3.34. Архітектури побудови систем клієнт-сервер. Варіанти побудови серверних прикладень. Варіанти побудови клієнтських прикладень.

- •3.35. Драйвери. Призначення, структура. Механізм роботи драйвера. Приклади драйверів.

- •3.36. Керування процесорним часом. Модель планувальника та диспетчера процесорного часу. Пріоритети процесів.

- •3.37. Керування процесорним часом. Витісняючі та невитісняючі дисципліни планування процесорного часу.

1.23. Архітектура та принцип роботи годинника реального часу rtc та cmos пам'яті. Можливості програмування.

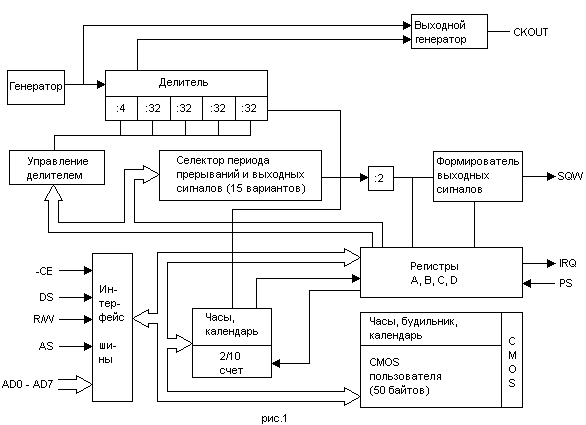

В состав IBM PC AT входят часы реальн времени Real Time Clock (RTC) и 64 байта неразрушающейся операт КМОП памяти (CMOS), питающиеся от автон ист пит. При включ ПЭВМ содержимое CMOS анализир-ся POST, кот. извлек из нее конфигур системы и текущие дату и время. Упрощ структ схема микросх МС146818 фирмы Motorola кот. представл на рис. 1.

Назначение сигналов следующее:

-CE - разрешение кристалла (выход дешифратора адреса);

DS - строб данных;

AS - адресный строб;

R/W - чтение/запись;

SQW - выходные прямоугольные импульсы – меандр (в IBM PC AT не используются);

IRQ - запрос на прерывание от RTC;

PS - сигнал состояния питания (используется для контроля достоверности данных);

CKOUT - синхросигн, кот.может использоваться как входной синхросигнал микропроц.

Основн часть RTC - задающий генер (внутр или внешн) с частотой 4.19 МГц, 1.04 МГц и делитель част, у кот. вых последн каскада (1 Гц) управл часами. Для доступа к данным CMOS исп-ся порты 70h и 71h, адрес рег подается в 70h порт, а данные чит/пиш через 71h порт.

Адреса CMOS с 10h по 20h защищ контрольн суммой, хранящейся по адресам 2Eh-2Fh. Порт 70h примен не только для задания адреса CMOS, но и для разреш или запрещ NMI (немаскируемого прерывания). Если бит 7 равен 0, то NMI разреш, если 1 - запрещается.

Все данные RTC хранятся в двоично - десятичном формате. Байты будильника 1h, 3h, 5h служат для создания времени выработки сигнала прерыв от RTС. Каждый байт может содержать конкретное значение времени (сек и мин в пределах 0-59, а часы в пределах 0-23) и "безразличное" значение - код в пределах C0h-FFh, т.е. два старших разряда содержат 1.

При конкр задании времени прерыв вырабат-ся раз в сутки (2 раза при 12-ти часов врем). Если байт часов содержит "безразличный" код, прерыв каждый час; если байт часов и минут "безразличны", прерыв каждую мин; и при всех "безразличных" байтах - каждую сек.

0Ah - Регистр A состояния RTC:

0Bh - Регистр B состояния RTC:

0Ch- Рег С сост RTC: биты сост прерыв, только для чт. При чт из рег все разр сбрасыв.

0Dh - Рег D сост RTC. Бит 7=1, если CMOS получ питание; 0=нет питания от автономн ист.

0Eh - Байт результатов начального тестирования:

0Fh -Байт состояния перезагрузки.

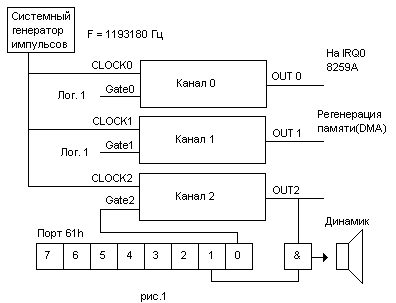

1.24. Архітектура системного таймера та призначення каналів таймера. Режими роботи каналів таймера. Можливості програмування.

В се

компьютеры IBM содержат 3-х канальное

16-ти разрядное устр-во, наз сист таймером.

Структурная схема системного таймера

представлена на рис. 5.1.

се

компьютеры IBM содержат 3-х канальное

16-ти разрядное устр-во, наз сист таймером.

Структурная схема системного таймера

представлена на рис. 5.1.

Таймеры 8253 и 8254 состоят из трех независимых каналов. Каждый канал содержит регистры:

- состояния канала RS (8 разрядов);

- управляющего слова PSW (6 разрядов);

- буферный регистр OL (16 разрядов);

- регистр счетчика CE (16 разрядов);

- регистр констант пересчета CR (16 разрядов).

Каналы таймера подключаются к внешним устройствам при помощи трех линий:

GATE - управляющий вход; CLOCK - вход тактовой частоты; OUT - выход таймера.

Регистр счетчика CE работает в режиме вычитания. Его содержимое уменьшается по заднему фронту сигнала CLOCK при условии, что на входе GATE установлен уровень логической 1. В зависимости от режима работы таймера при достижении счетчиком CE нуля тем или иным способом меняется выходной сигнал OUT. Буферный регистр OL предназначен для запоминания текущего содержимого регистра счетчика CE без остановки процесса счета. После запоминания буферный регистр доступен программе для чтения. Регистр констант пересчета CR предназначен для хранения констант пересчета и может загружаться в регистр счетчика, если это требуется в текущем режиме работы таймера. Содержимое регистра CR изменяется только при перезагрузке счетчика или при перепрограммировании режима (записи управляющего слова). При перепрограммировании содержимое CR устанавливается в нуль. Регистр состояния канала RS хранит текущее состояние канала и может быть прочитан для выбранного канала командой "обратное чтение".Регистр управляющего слова PSW хранит управляющую информацию канала и задает его режим работы до следующего перепрограммирования. Системный генератор импульсов (СГИ) независимо от типа и производительности компьютера IBM вырабатывает импульсы одной и той же частоты - 1 193180 Гц.

В компьютерах IBM PC/XT/AT/PS2 задействованы все три канала таймера.

Канал 0 используется в системных часах времени суток. Этот канал работает в режиме 3 (описание режимов см. в п.5.2.) и используется как генератор импульсов с частотой примерно 18,2 Гц. Канал 1 используется для регенерации содержимого динамической памяти компьютера, поэтому его лучше не трогать. Выходная линия канала OUT связана с микросхемой прямого доступа к памяти (DMA), и ее импульс заставляет DMA регенерировать память. Канал использует режим 2 таймера. Канал 2 связан с громкоговорителем (динамиком) компьютера и может быть использован для генерации различных звуков или музыки либо как генератор случайных чисел. Канал использует режим 3 таймера.

Каждый канал таймера может работать в одном из шести режимов.

Режим 0 - прерывание терминального счета. После загрузки PSW сигнал OUT устанавливается в 0. Запись константы не влияет на OUT. Счет разрешается сигналом GATE=1 и запрещается GATE=0. При GATE=1 и фронту первого CLK константа счета N загружается из CR в CE, а по второму CLK начинается счет. OUT удерживается в нуле до конца счета, т.е. на время (N+1)*T сек. после чего возвращается в 1. Изменение GATE не влияет на OUT, но при GATE=0 счет приостанавливается, а при GATE=1 возобновляется без перезагрузки CE. Загрузка нового управляющего слова при новой константе возобновляет цикл.

Режим 1 - программируемый ждущий мультивибратор. На выходе OUT формируется сигнал низкого уровня длительностью T=Tclk*N (N - константа пересчета; Tclk - период синхроимпульсов). Счет начинается (OUT устанавливается в 0) по положительному фронту GATE, и OUT становится равен 1 по завершению счета. Данный режим является режимом с перезапуском, т.е. по каждому положительному фронту GATE содержимое CR передается в CE и перезапускает его, даже если предыдущий счет не завершен до конца. Загрузка во время счета новой константы не влияет на длительность текущего импульса до новой перезагрузки.

Режим 2 - импульсный генератор частоты. Канал выполняет функцию программируемого делителя входной частоты Fclk . Сразу после загрузки PSW выход OUT становится равным 1 и при удержании GATE=1 сигнал OUT держится в состоянии 1 в течении времени (N-1)*Tclk, после чего переходит в 0 и удерживается в этом состоянии на время Tclk. По окончании указанного цикла выполняется автозагрузка CE из CR и цикл повторяется. При подаче GATE=0 OUT устанавливается в 1, счет прекращается и возобновляется при GATE=1 с начального значения. При загрузке новой константы в CR во время счета текущий цикл не меняется, изменится длительность следующего цикла.

Режим 3 - генератор меандра. Режим аналогичен режиму 2, но на выходе формируются импульсы длительностью полупериода N/2*Tclk при четном N. При нечетном N положительный импульс (OUT=1) имеет длительность (N+1)/2*Tclk, а отрицательный импульс(OUT =0) имеет длительность (N-1)/2*Tclk. Генератор не работает,если N=3.

Режим 4 - программно формируемый строб. Сигнал OUT устанавливается равным 1 после загрузки PSW и удерживается до конца счета, после чего на выходе OUT устанавливается 0 на период Tclk и возвращается в 1, т.о. цикл работы имеет длительность (N+1)*Tclk сек. По действию сигнала GATE и режиму работы (однократное выполнение функции) он аналогичен режиму 0.

Режим 5 - аппаратно формируемый строб. По выходному сигналу режим аналогичен режиму 4 (OUT=1 после загрузки PSW до конца счета и OUT=0 в течении Tclk после окончания счета), а по действию GATE режиму 1, т.е. запуск счета выполняется по переднему фронту сигнала GATE.

Каждый канал таймера программируется отдельно и независимо от других. При программировании канала необходимо послать ему управляющее слово (старшие 2 разряда управляющего слова указывают номер канала, а остальные 6 разрядов защелкиваются в регистре PSW выбранного канала), после чего загружается регистр констант пересчета CR. Так как 16-ти разрядные регистры констант CR отображаются через 8-ми разрядные порты, то загрузка CR выполняется в соответствии с указаниями управляющего слова. Таймеру соответствуют 4 порта ввода/вывода со следующими адресами: 40h - канал 0; 41h - канал 1; 42h - канал 2; 43h - управляющее слово.