- •1.Функциональное описание микроконтроллера i80196kc

- •1.1. Обзор архитектуры

- •1.1.1. Ядро 80xc196kc

- •1.1.1.1. Файловый регистр (Register File)

- •1.1.1.2. Регистровое арифметико-логическое устройство (ралу)

- •1.1.1.4. Контроллер памяти ( Memory Controller)

- •1.1.1.5. Контроллер прерываний и pts (Interrupt Controller)

- •1.2. Параметры синхронизации

- •1.3. Внутренние периферийные устройства

- •1.3.1. Стандартные порты ввода-вывода

- •1.3.2. Последовательный порт ввода-вывода

- •1.3.3. Быстродействующий модуль

- •1.3.4. Аналого-Цифровой Преобразователь (ацп)

- •1.3.5. Широтно-импульсный модулятор (шим)

- •1.3.6. Сторожевой Таймер

- •2.Введение в программирование 8xc196kc

- •2.1. Типы программирования микроконтроллера

- •2.2. Система команд

- •2.3. Типы данных

- •2.4. Способы адресации

- •3. Карта памяти микроконтроллера i80c196kc

- •3.1. Основные разделы памяти

- •3.1.1. Разделы внешней памяти

- •3.1.2. Порты 3 и 4

- •3.1.3. Программная память и Память Специального назначения

- •3.1.3.1. Управление доступом к внутренней или внешней памяти

- •3.1.3.2. Память для программ

- •3.1.3.3. Память специального назначения

- •3.1.4. Регистровый Файл(Register File)

- •3.1.4.1. Указатель Вершины стека (sp)

- •3.1.4.2 Регистры Специальных Функций

- •3.2. Работа через горизонтальное окно

- •3.2.1. Выбор hWindow

- •3.3.1. Выбор vWindow

- •3.3.2. Работа с вертикальными окнами и Способы Адресации

- •4. Прерывания

- •4.1 Обработка Прерывания

- •4.2. Описание работы Контроллера Прерывания

- •4.3. Описание работы Периферийной Станции Транзакций(pts)

- •4.4. Приоритеты Прерывания

- •4.5. Изменение Приоритетов Прерывания

- •4.6. Программы Обработки прерывания

- •4.7. Распознавание Прерываний

- •4.8. Время Ожидания Прерывания

- •4.9. Специальные Прерывания

- •4.9.1. Прерывание по Невыполняемому Коду

- •4.9.2. Прерывание по Ловушке Программного

- •4.9.3. Немаскируемое Прерывание

- •4.10. Программирование Прерываний

- •4.11. Предоставление pts Прерывания

- •4.12. Предоставление Стандартных Прерываний

- •4.13. Выбор Источников Прерывания

- •4.14. Регистры Маскирования Прерываний

- •4.15. Регистры Захвата Прерывания

- •4.16. Pts Прерывания

- •4.16.1. Управляющие Блоки pts

- •4.16.1.1. Регистр ptscount

- •4.16.1.2. Прерывание End-of-pts

- •4.16.1.3. Регистр ptscon

- •4.16.2. Краткий Обзор Режима Одиночной

- •4.16.2.1. Пример Режима Одиночной Передачи

- •4.16.3. Краткий Обзор Режима Поблочной

- •4.16.3.1. Пример Режима Поблочной Пересылки

- •4.16.4. Краткий Обзор Режима Сканирования

- •4.16.4.1. Pts Циклы в Режиме Сканирования ацп

- •11Eh ad_result для ach0

- •102H ad_result для acHx

- •100H ad_command для acHx

- •4.16.5. Hsi. Краткий Обзор Режима

- •4.16.5.1. Пример Режима hsi

- •4.16.6. Hso. Краткий Обзор Режима

- •4.16.6.1. Пример Режима hso

- •6. Парраллельные порты ввода - вывода

- •6.1. Краткий Функциональный Обзор

- •6.2.Контакты Порта Ввода

- •6.3. Контакты Порта Вывода

- •6.4. Контакты квази-двунаправленного порта

- •6.5 Контакты Двунаправленного Порта с открытым стоком

- •6.6.Программирование Портов ввода-вывода

- •6.7.Организация Портов Ввода

- •6.7.1. Порт 0

- •6.8. Организация Портов Вывода

- •6.9. Порт 1

- •6.10. Порт 2

- •6.11. Доступ к Порту 3 и Порту 4

- •6.11.1. Порт 3 и Порт 4

- •6.12. Особенности работы с квази - двунаправленными портами

4.16.6.1. Пример Режима hso

PTSCB на рис.22 определяет десять PTS циклов, каждый из которых будет передавать 8 блоков HSO_COMMAND/ HSO_TIME данных в HSO из таблицы, начинающейся в

ячейке памяти 100H. Исходный адрес увеличивается после каждой передачи и модифицируется новым значением после каждого цикла.

Рис.22 PTSCB для HSO Режима

6. Парраллельные порты ввода - вывода

6.1. Краткий Функциональный Обзор

Порты ввода-вывода обеспечивают механизм передачи информации между устройством и внешними системами.

8XC196KC имеет пять 8-битных порта ввода-вывода.

Каждый порт ввода-вывода имеет контакты, которые являются :

- или только для ввода(INPUT);

- или только для вывода(OUTPUT);

- квази - двунаправленными (QuasyBiDirectional), - двунаправленными с открытым стоком,

- или как комбинация четырех перечисленных.

Почти все контакты портов ввода-вывода выполняют альтернативные функции. Например, один из контактов порта ввода-вывода может стать выходом PWM, в то время как другой может использоваться как аналоговый вход.

Каждый контакт порта ввода-вывода имеет функцию по умолчанию ( например, вывод ). Однако, функция контакта может изменяться при выборе альтернативной функции.

Например, при выборе альтернативной функции, квази - двунаправленный контакт становится контактом только для вывода.

В любом случае, контакт имеет базисный набор харак-теристик работы , связанных с данной конфигурацией .

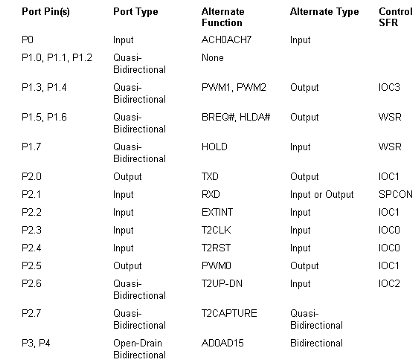

В таблице 8 приведены пять портов ввода-вывода(P0,P1,P2, P3,P4), их альтернативные функции(Alternate Function) и функции по умолчанию (Port Type). Пятый столбец таблицы 8 указывает SFR, который определяет как функционирует контакт:

- или как порт;

- или по альтернативной функции.

Некоторые контакты порта эксплуатируются и как контакты порта, и как контакты альтернативной функции порта одновременно (например, Порт 0 и аналоговые входы ). В этом случае, пятый столбец таблицы 8 оставлен пустым.

Кроме стандартных портов ввода-вывода, дополнительные функции ввода-вывода могут обеспечивать High-Speed Input модуль и High-Speed Output модуль.

Таблица 8. Функции Штырьков Порта

6.2.Контакты Порта Ввода

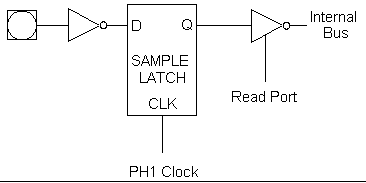

Любой контакт порта, предназначенный для ввода, может только читаться. Любая операция записи в контакт игнорируется ( или не возможна ). Общая схема контакта для ввода состоит из триггера выборки (Sample Latch) и буфера чтения ( см.рис.23).

Рис.23 Контакт Порта Ввода

Контакт порта выбирается за одно время состояния до того, как разрешается чтение из буфера. Выборка и распознавание значения контакта( 0 или 1) происходит в течение Фазы 1 ( пока CLKOUT = 0 ) до того , как оно подается на внутреннюю шину. Если во время выборки происходят изменения значения контакта, новое значение может быть записано ( а может и не записано) во время чтения.

Входные контакты порта не имеют никаких выходных драйверов(формирователей,усилителей).

6.3. Контакты Порта Вывода

Контакт вывода состоит из защелки порта(Port Latch) и логики управления контактом (Q1,Q2,Q3)( см. рис.24 ).

Новое значение контакта вывода защелкивается в течение Фазы 1 ( пока CLKOUT = 0 ). Значение контакта остается устойчивым до того , пока его не изменит другая операция записи ( или пока не произойдет сброс устройства). Контакты порта Вывода не имеют схем выборки и схем чтения буфера. При чтении контакта вывода его значение неопределено и должно маскироваться. Так как нет никакого механизма чтения значения контакта порта вывода, то возможна только установка или очистка контакта вывода. Если необходимо инвертировать значение контакта, образ контакта должен храниться в памяти. Этот образ в памяти используется при установке или очистке контакта.

Рис.24 Контакт Порта Вывода