- •1.Функциональное описание микроконтроллера i80196kc

- •1.1. Обзор архитектуры

- •1.1.1. Ядро 80xc196kc

- •1.1.1.1. Файловый регистр (Register File)

- •1.1.1.2. Регистровое арифметико-логическое устройство (ралу)

- •1.1.1.4. Контроллер памяти ( Memory Controller)

- •1.1.1.5. Контроллер прерываний и pts (Interrupt Controller)

- •1.2. Параметры синхронизации

- •1.3. Внутренние периферийные устройства

- •1.3.1. Стандартные порты ввода-вывода

- •1.3.2. Последовательный порт ввода-вывода

- •1.3.3. Быстродействующий модуль

- •1.3.4. Аналого-Цифровой Преобразователь (ацп)

- •1.3.5. Широтно-импульсный модулятор (шим)

- •1.3.6. Сторожевой Таймер

- •2.Введение в программирование 8xc196kc

- •2.1. Типы программирования микроконтроллера

- •2.2. Система команд

- •2.3. Типы данных

- •2.4. Способы адресации

- •3. Карта памяти микроконтроллера i80c196kc

- •3.1. Основные разделы памяти

- •3.1.1. Разделы внешней памяти

- •3.1.2. Порты 3 и 4

- •3.1.3. Программная память и Память Специального назначения

- •3.1.3.1. Управление доступом к внутренней или внешней памяти

- •3.1.3.2. Память для программ

- •3.1.3.3. Память специального назначения

- •3.1.4. Регистровый Файл(Register File)

- •3.1.4.1. Указатель Вершины стека (sp)

- •3.1.4.2 Регистры Специальных Функций

- •3.2. Работа через горизонтальное окно

- •3.2.1. Выбор hWindow

- •3.3.1. Выбор vWindow

- •3.3.2. Работа с вертикальными окнами и Способы Адресации

- •4. Прерывания

- •4.1 Обработка Прерывания

- •4.2. Описание работы Контроллера Прерывания

- •4.3. Описание работы Периферийной Станции Транзакций(pts)

- •4.4. Приоритеты Прерывания

- •4.5. Изменение Приоритетов Прерывания

- •4.6. Программы Обработки прерывания

- •4.7. Распознавание Прерываний

- •4.8. Время Ожидания Прерывания

- •4.9. Специальные Прерывания

- •4.9.1. Прерывание по Невыполняемому Коду

- •4.9.2. Прерывание по Ловушке Программного

- •4.9.3. Немаскируемое Прерывание

- •4.10. Программирование Прерываний

- •4.11. Предоставление pts Прерывания

- •4.12. Предоставление Стандартных Прерываний

- •4.13. Выбор Источников Прерывания

- •4.14. Регистры Маскирования Прерываний

- •4.15. Регистры Захвата Прерывания

- •4.16. Pts Прерывания

- •4.16.1. Управляющие Блоки pts

- •4.16.1.1. Регистр ptscount

- •4.16.1.2. Прерывание End-of-pts

- •4.16.1.3. Регистр ptscon

- •4.16.2. Краткий Обзор Режима Одиночной

- •4.16.2.1. Пример Режима Одиночной Передачи

- •4.16.3. Краткий Обзор Режима Поблочной

- •4.16.3.1. Пример Режима Поблочной Пересылки

- •4.16.4. Краткий Обзор Режима Сканирования

- •4.16.4.1. Pts Циклы в Режиме Сканирования ацп

- •11Eh ad_result для ach0

- •102H ad_result для acHx

- •100H ad_command для acHx

- •4.16.5. Hsi. Краткий Обзор Режима

- •4.16.5.1. Пример Режима hsi

- •4.16.6. Hso. Краткий Обзор Режима

- •4.16.6.1. Пример Режима hso

- •6. Парраллельные порты ввода - вывода

- •6.1. Краткий Функциональный Обзор

- •6.2.Контакты Порта Ввода

- •6.3. Контакты Порта Вывода

- •6.4. Контакты квази-двунаправленного порта

- •6.5 Контакты Двунаправленного Порта с открытым стоком

- •6.6.Программирование Портов ввода-вывода

- •6.7.Организация Портов Ввода

- •6.7.1. Порт 0

- •6.8. Организация Портов Вывода

- •6.9. Порт 1

- •6.10. Порт 2

- •6.11. Доступ к Порту 3 и Порту 4

- •6.11.1. Порт 3 и Порт 4

- •6.12. Особенности работы с квази - двунаправленными портами

4.11. Предоставление pts Прерывания

После того, как Вы назначаете прерывание к PTS, Вы должны разрешить и PTS и индивидуальное прерывание. Бит разрешения PTS в Слове Состояния Процессора (PSW.2) глобально разрешает или запрещает PTS. Команда EPTS устанавливает бит PSW.2, допуская PTS. Команда DPTS очищает этот бит, отключая PTS. Биты в INT_MASK и INT_MASK1 разрешают или запрещают индивидуальные прерывания PTS ( см.

табл.3 ).

4.12. Предоставление Стандартных Прерываний

Когда Вы назначаете прерывание стандартной сервисной программе обслуживания прерывания, Вы должны разрешить и обслуживание прерывания и индивидуальное прерывание. Бит Глобального разрешения прерывания (I) в Слове Состояния

Процессора (PSW.1) глобально разрешает или запрещает обслуживание всех маскируемых прерываний. Команда EI устанавливает бит PSW.1,разрешая обслуживание прерываний. Команда DI очищает этот бит, отключая обслуживание прерываний.

Биты в INT_MASK и INT_MASK1 индивидуально разрешают или запрещают прерывания (см. табл.3 ). Прерывание,которое происходит во время обслуживания прерывания, глобально

запрещается (PSW.1 сбрасывается )и задерживается в регистрах захвата прерывания.

4.13. Выбор Источников Прерывания

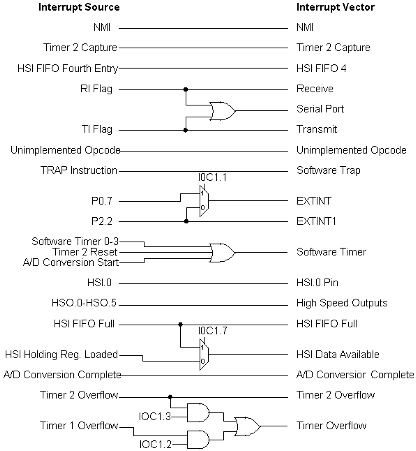

Каждый из пяти следующих источников прерывания (HSI FIFO Full, EXTINT1, Receive, Transmit, Timer 2 Overflow) могут генерировать два различных прерывания:

- 8096BH-совместимое прерывание;

- отдельное прерывание для KC;

В любом случае,надо разрешать только одно прерывание для каждого источника. То есть бит маски должен быть установлен только для одного из двух возможных прерываний. На рис.10 приведены источники прерывания для каждого вектора прерывания. В табл.3 приведены значения битов регистра IOC1, которые выбирают каждый из источников.

4.14. Регистры Маскирования Прерываний

Регистры маскирования прерывания, INT_MASK(08H) и INT_MASK1(13H), разрешают или запрещают(маскируют) индивидуальные прерывания. За исключением бита Немаскируемого Прерывания (NMI) ( INT_MASK1.7 ), установка соответствующего бита разрешает соответствующее прерывание ; очистка соответственно запрещает прерывание. Когда устройство сбрасывается, регистры маски прерывания очищаются (запрещая прерывания ). Регистры читаемы и записываемы во всех окнах. Команда PUSHA сохраняет содержимое этих регистров в стеке, а POPA восстанавливает.

4.15. Регистры Захвата Прерывания

Когда Детектор Перехода обнаруживает прерывание, он устанавливает соответствующий бит в INT_PEND(09H) или INT_PEND1(12H) регистрах,даже если индивидуальное прерывание отключено (замаскировано). Бит Захвата очищается, когда программа переходит к подпрограмме обработки прерывания( стандартного или PTS прерывания ). INT_PEND и INT_PEND1 можно читать, чтобы определить, какие поступили прерывания.

С помощью программного обеспечения, биты в этих регистрах можно устанавливать или сбрасывать, генерируя

прерывания. Однако надо быть осторожным при записи кода в эти регистры. Например, последовательность команд, которая очищает бит захвата, может привести к подтверждению прерывания после того, как последовательность начнется, но прежде, чем бит фактически очистится.

В этом случае происходит частичный цикл прерывания в 5 тактов. То-есть процесс прерывания начинается, но никогда не переходит к программе обработки прерывания.

Такую задержку можно предотвратить, делая код неделимым, то есть прерывания не будут подтверждаться, пока выполняется этот код. Самый простой способ сделать это состoит в том, чтобы использовать логические

команды в двух или трех операндном формате, например:

ANDB INT_PEND, #01111111B ; Очищает прерывание EXTINT

ORB INT_PEND, #10000000B;Устанавливает прерывание EXTINT

8XC196KC/KD не подтверждает прерывания в течение выполнения этих команд "чтение-модификация-запись".

По сбросу INT_PEND, INT_PEND1 = 0000 0000

Рис.10 Источники Прерывания