Министерство образования и науки Российской Федерации

Государственное общеобразовательное учреждение

Высшего профессионального образования

Ижевский государственный технический университет

Кафедра «Радиотехника»

Лабораторная работа

На тему : «МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ».

Выполнил:

студент гр. 4-76-2

Караганских Р.В.

Проверил:

К.п.н Зайцева Е.М.

Ижевск 2012.

ЛАБОРАТОРНАЯ РАБОТА №3.1 Синтез комбинационных узлов с использованием базовых логических элементов.

Цель: научиться синтезировать комбинационные узлы с использованием базовых логических элементов.

Задание 1: Синтезировать структурную

схему, выполняющую функции и постройте

таблицу истинности

![]() .

Покажите правильность работы схемы.

.

Покажите правильность работы схемы.

Исследование инвертирующего усилителя

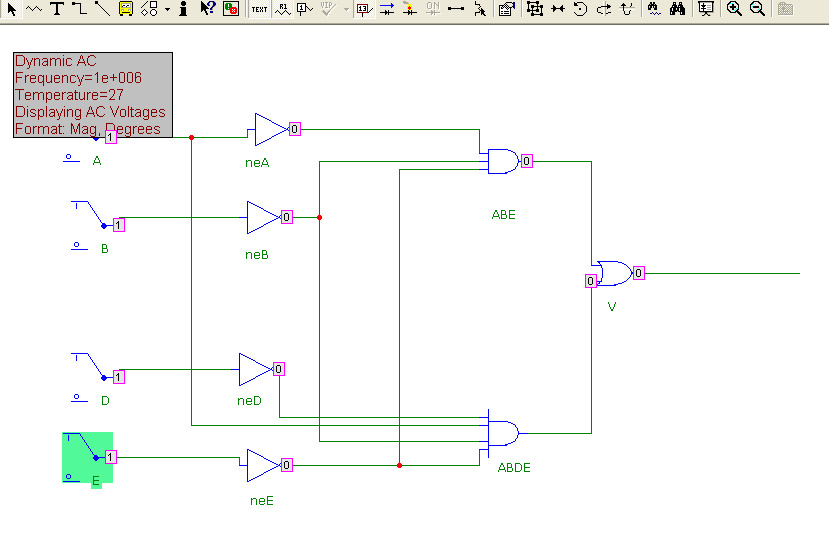

1)Нужно синтезировать структурную схему, выполняющую функции и построить таблицу истинности ; показать правильность работы схемы. В среде системы схемотехнического моделирования МicroСap9 создали схему, выполняющую функцию . На рис.1 приведена схема, а также результаты моделирования.

Рис.1

Построили таблицу истинности . Для этого выполнили моделирование схемы в режиме Analysis/Dinamic DC. В окне “Установки динамического DC анализа” задали установки и параметры анализа, например – «отображение узловых потенциалов». Для запуска расчета нажали «Да».

На рис.2 и в табл.1 в качестве примера приведены установки моделирования для вышеприведенной схемы и таблица истинности, которая была составлена из нескольких результатов.

Рис.2

A |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

B |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

D |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

E |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Табл.1

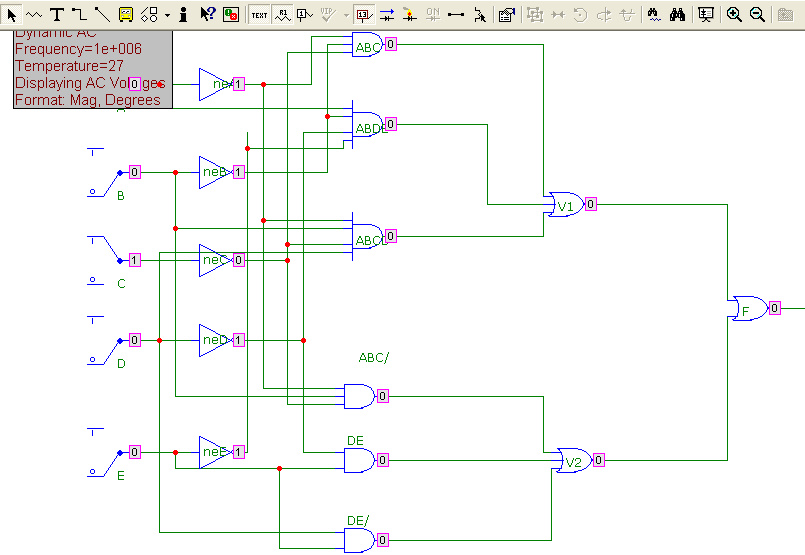

Задание 2. Синтезировать структурную

схему, выполняющую функции и построить

таблицу истинности![]() ;

показать правильность работы схемы. На

рис.3 приведен пример построения схемы,

а также результаты моделирования.

;

показать правильность работы схемы. На

рис.3 приведен пример построения схемы,

а также результаты моделирования.

Рис.3

На рис.4 и в табл.2 в качестве примера приведены установки моделирования для вышеприведенной схемы и таблица истинности.

Рис.4

A |

B |

C |

D |

E |

функция |

A |

B |

C |

D |

E |

функция |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

Табл.2

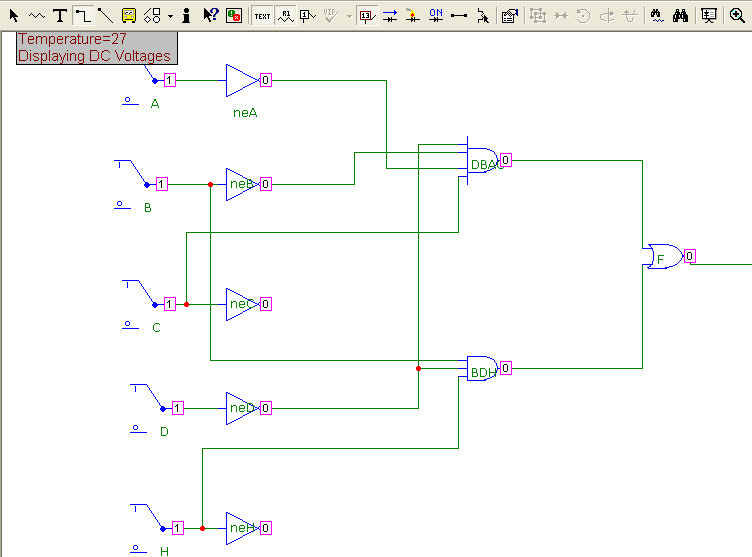

Задании 3. Синтезировать структурную

схему, выполняющую функции и построить

таблицу истинности![]() ;

показать правильность работы схемы. На

рис.5 приведен пример построения схемы,

а также результаты моделирования.

;

показать правильность работы схемы. На

рис.5 приведен пример построения схемы,

а также результаты моделирования.

Рис.5

На рис.6 и в табл.3 в качестве примера приведены установки моделирования для вышеприведенной схемы и таблица истинности.

Рис.6

A |

B |

C |

D |

H |

функция |

A |

B |

C |

D |

H |

функция |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Табл.3

Вывод (1): Исходя из полученной таблицы истинности, можно сделать вывод, что схема построена, верно, и задуманная функция выполняется.

Вывод (2): Схема построена верно, задуманная функция выполняется.

Вывод (3): Схема построена верно, задуманная функция выполняется.

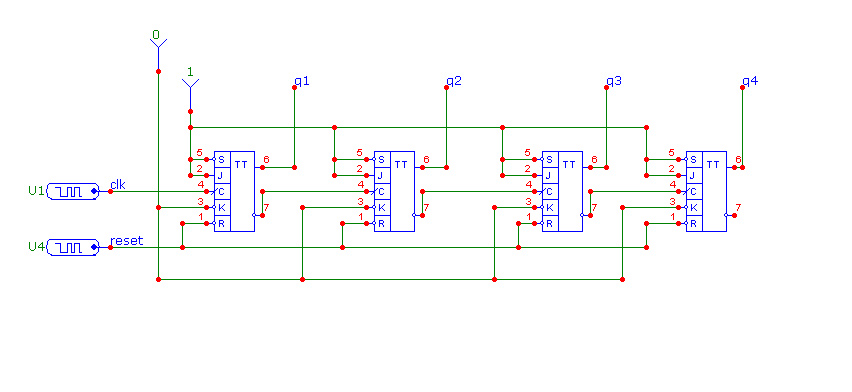

Лабораторная работа № 3.2 “Исследование асинхронных двоичных счетчиков”

Цель работы: Изучение принципов построения и функционирования двоичных счетчиков; исследование быстродействия счетчиков с последовательным и параллельным переносами.

а) Исследование счетчика с последовательным переносом

В среде системы схемотехнического моделирования МС9 создали схему 4-разрядного асинхронного счетчика с последовательным переносом. Типы триггеров K155TV15.

Пример построения схемы приведен на рис.1.

Рис.1

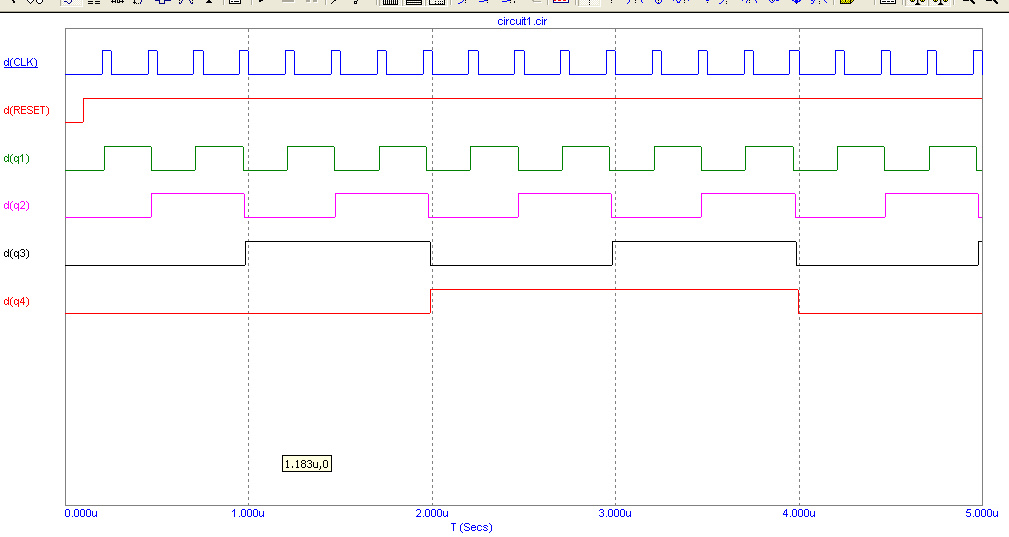

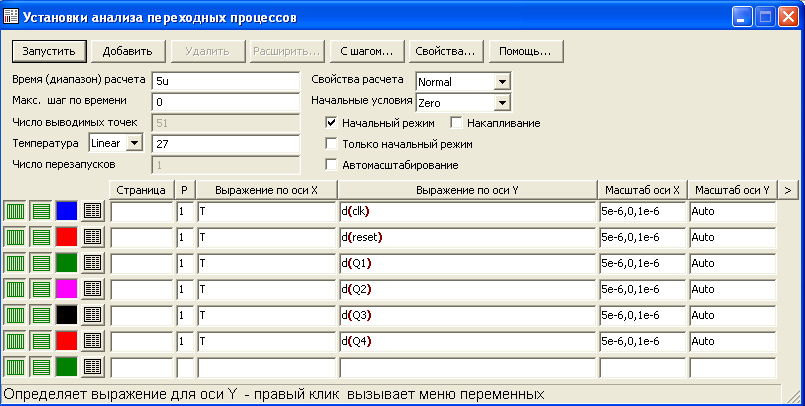

Выполнили моделирование схемы в режиме Analysis/Transient analysis. В окне “Transient analysis limits” задали выводимые временные диаграммы и пределы изменения величин по амплитуде сигналов и времени. Для запуска расчета нажали RUN (Запустить).

Параметры генераторов:

U1

.define _1MHzClk

+0ns 0

+label=start

+200n 1

+250n 0

+450n goto start -1 times

U4

.define B

+0NS 0

+50NS 0

+100NS 1

Примеры расчетов приведены на рис.2 и рис.3.

Рис.2

Рис.3

По временным диаграммам определили время установления счетчика tуст. Для этого выделили фрагмент диаграммы, и увеличили его.

Определенное нами время установления

счетчика

![]() 40ns(наносекунд).

40ns(наносекунд).

Б) Исследование счетчика с параллельным переносом.

На базе серии микросхем K155TV1 создали схему 4-разрядного асинхронного счетчика с параллельным переносом.

Пример построения схемы приведен на рис.5.

Рис.5

Выполнили моделирование схемы в режиме Analysis/Transient analysis. В окне “Transient analysis limits” задали выводимые временные диаграммы и пределы изменения величин по амплитуде сигналов и времени. Для запуска расчета нажали RUN (Запустить).

Параметры генераторов:

для U1 .define _1MHzClk +0ns 0 +label=start +200n 1 +250n 0 +450n goto start -1 times для U2 .define B +0NS 0 +50NS 0 +100NS 1

Примеры расчетов приведены на рис.6 и рис.7.

Рис.6

Рис.7

По временным диаграммам определили время установления счетчика tуст.

Определенное нами время установления счетчика 100ns(наносекунд).

Вывод: Обе микросхемы смоделированы верно, и работают правильно. Время установления счетчика tуст=40ns – у первого счетчика, и tуст=100ns – у второго.