Теоретическое введение

Контроллер прямого доступа к памяти КПДП предназначен для управления передачей информации между внешним устройством и запоминающим устройством (ЗУ) МПС. Он информирует последовательность адресов ЗУ и сигналы управления. В его состав входят буфер данных, схема управления и четыре независимых канала, каждый из которых содержит 10-и разрядный регистр начального адреса РА и 16-и разрядный регистр управления РЦ (РУ). 14 младших разрядов РЦ содержат число на 1 меньше длин массива, а 15 и 16 разряды определяют направление обмена в соответствии с табл. 5.1.

При программировании КПДП при обращении к нему как к ВУ вначале загружают в РА соответствующего канала младший байт начального адреса массива, за ним старший байт по тому же адресу РА канала. Таким же образом вводят младший и старший байты РЦ.

Табл. 5.1. Возможные операции обмена

-

15 разр.

14 разр.

Операция

0

0

1

1

0

1

0

1

контроль

запись в ЗУ

чтение из ЗУ

сочетание запрещено

В процессе выполнения программы МП может считывать содержимое регистров РА и РЦ любого канала. Для этого необходимо две команды IN а одним и тем же адресом (сначала считывается младший байт, потом старший).

Чтобы разрешить работу одного или нескольких каналов, установить режим работы контроллера, необходимо записать в регистр режима управляющее слово.

Формат управляющего слова приведен в табл. 5.2. Если при записи управляющего слова режим циклического приоритета не задан, то нулевой канал имеет высший приоритет, а третий низший. При работе канала передача каждого байта информации происходит за один цикл.

В исходном состоянии контроллер находится в режиме ожидания сигнала от ВУ – запроса прямого доступа к памяти – DRQ. Получив этот сигнал контроллер в следующем такте выдаст сигнал запроса прямого доступа HRQ на вход HOLD МП и переходит к ожиданию сигнала HLDA – разрешения захвата шин от МП, получив который вырабатывает сигнал разрешения передачи адреса AEN, который подается на ВУ и предохраняет другие ВУ от ошибочного воздействия при появлении на шине выработанных контроллером адресов. Затем переходит во второе состояние, при котором выдает стробирующий сигнал адреса STB A и затем выдает на ВУ низкий уровень сигнала разрешения прямого доступа - .

Если цикл записи или чтения байта информации ВУ больше контроллера, то контроллер переходит в состояние ожидания, выход из которого осуществляется по сигналу READY.

Табл. 5.2. Назначение разрядов управляющего слова

Разряд |

Назначение разряда |

D0 D1 D2 D3 D4 D5 D6

D7

|

К0 – разрешение работы канала – 0; 1 – разрешить К1 – разрешение работы канала – 1; 1 – разрешить К2 – разрешение работы канала – 2; 1 – разрешить К3 – разрешение работы канала – 3; 1 – разрешить ДП=1 – циклический приоритет 0 – фиксированный Р3=1 – расширенная запись ОК = 1 – отключение канала по окончании счета ОК=0 – канала не отключается, доступ продолжается после сброса счетчика А3=1 – автоматическая загрузка |

Табл. 5.3. Обращение к регистрам в зависимости от сигнала на линия адреса

Регистр |

А3 |

А2 |

А1 |

А0 |

адрес МИ-3 МПС |

Регистр адреса РАО Регистр управл. РУО РА1 РУ1 РА2 РУ2 РА3 РУ3 Регистр режима РР Регистр состояния РС |

0 0 0 0 0 0 0 0 1 1 |

0 0 0 0 1 1 1 1 0 0 |

0 0 1 1 1 1 1 1 0 0 |

0 1 0 1 0 1 0 1 0 0 |

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 |

Табл. 5.4. Назначение разрядов регистра состояния

Разряд |

Назначение разряда |

D0 D1 D2 D3 D4 D5 D6 D7 |

=1 – конец счета канала 0 =1 – конец счета канала 1 =1 – конец счета канала 2 =1 – конец счета канала 3 =1 – копирование =0 =0 =0 |

Во время передачи последнего байта контроллер выдает сигнал конца счета ТС и сигнал конца блока данных MARK (МП8) если до конца массива осталось кратное 128 число циклов записи или чтения (включая данный цикл).

При установке управляющим словом режима расширенной записи сигнала запись ввода-вывода и запись в память в цикле записи вырабатывается несколько раньше, что ускоряет появление сигнала готовности – READY BY или запоминающего устройства и избежать, где это возможно, перехода контроллера в состояние ожидания.

Единичное значение бита D6 – (отключение канала) управляющего слова обуславливает отключение канала прямого доступа при выработке сигнала конец счета – Тс и сброс бита разрешения работы канала в управляющем слове. Повторная работа этого канала будет возможна только при занесении нового управляющего слова в РР. Если бит ОК управляющего слова равен нулю, появление сигнала конца счета Тс не оказывает влияния на бит разрешения работы сигнала. Выход из режима передачи в этом случае осуществляется внешним устройством снятием сигнала запроса прямого доступа – DRQ.

Режим автоматической загрузки (разряд D7 – A3 управляющего слова) позволяет использовать канал 2 для повторной передачи блока или передачи последовательности блоков без вмешательства МП в промежутке между передачей блоков.

Если ранее в регистр режимов занесено управляющее слово с единичным битом А3 (D7=1), то при занесении данных в регистр адреса РА2 и регистр управления РУ2 эти же данные будут загружены в РА3 и РУ3. После начала работы канала 2 и передачи по нему массива данных в соответствии с содержание РА2, РУ2 во время специального цикла копирования данные из РА3, РУ3 передаются в РА2, РУ2. Содержимое РА3, РУ3 при этом не изменяется. Следующим после цикла копирования будет первый цикл передачи байта нового массива данных. Если после занесения параметров массива в РА2, РУ2, в регистры третьего канала РА3, РУ3 занести другие параметры, то будет осуществлена последовательная передача разных массивов данных.

Во время выполнения цикла копирования в регистре состояния (табл. 5.4) устанавливается бит копирования, т.е. D4=1. Считывая содержимое этого регистра, МП определяет конец передачи массива данных, что позволяет ему ввести в РА3, РУ3 параметры следующего массива, подлежащего передаче.

После окончания цикла копирования бит копирования слова состояния сбрасывается.

При установленном в единицу разряде А3 (D7=1) управляющего слова независимо от значения бита ОК (D6) отключение канала 2 при выработке сигнала конец счета ТС не производится.

Разряды D0-D3 слова состояния (табл. 5.4) устанавливаются после появления сигнала ТС – конец счета. При считывании слова состояния биты конца счета D0-D3 сбрасываются.

Программа 5.1. Ввод 5 слов данных с внешнего устройства от ключей ВУ SA1 – SA8 в ОЗУ МПС с 0900 и вывод данных после окончания ввода через канал 3 на внешнее устройство – светодиоды HL13 – HL20.

Положение ключей ВМ-80:

Адр |

Код |

Ассемблер |

Комментарии |

0800 080A 080C 080E 0810 0812 0814 0816 0818 081A 081C 081E 0820 0822 0824 0826 0828

082A 082C

082E 082F

0832 0834 |

F3 3E 00 D3 D4 3E 09 D3 D4 3E 04 D3 D5 3E 40 D3 D5 3E 00 D3 D6 3E 09 D3 L6 3E 04 D3 07 3E 80 D3 D7

3E4C D3D8

FB 3A 00 09

D3 05 C3 2F 08

|

DI MVIA 00 OUT PA2 MVIA 09 OUT PA2 MVIA 04 OUT PУ2 MVIA 40 OUT PУ2 MVIA 00 OUT PA3 MVIA 09 OUT PA2 MVIA 04 OUT PУ3 MVIA 80 OUT PУ3

MVIA 4C OUT PP

EI LDA 0900

OUT HL JMP 082D

|

Запрет прерывания Загрузка мл. байта адреса Загрузка мл. байта в РА2

Загрузка ст. байта адреса в РА2

Запись мл. байта к-ва циклов в РУ2

Запись ст. 6 разрядов к-ва циклов и кода «Запись в ЗУ» в РУ2 Запись мл. Байта в РА3

Запись ст. байта в РА3

Запись мл. байта к-ва циклов в РУ3

Запись ст. 6 разрядов к-ва циклов и кода «Чтение из ЗУ» в РУ3

Запись управляющего слова в регистр режима Разрешение прерывания Загрузить в Акк. содержимое ячейки памяти 0900 Вывод в ВУ – светодиоды ВМ-80 Зациклить |

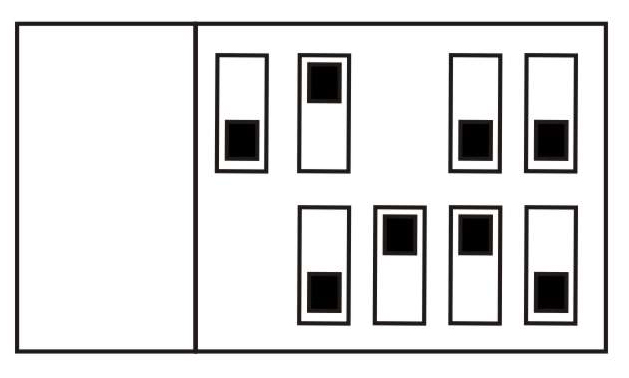

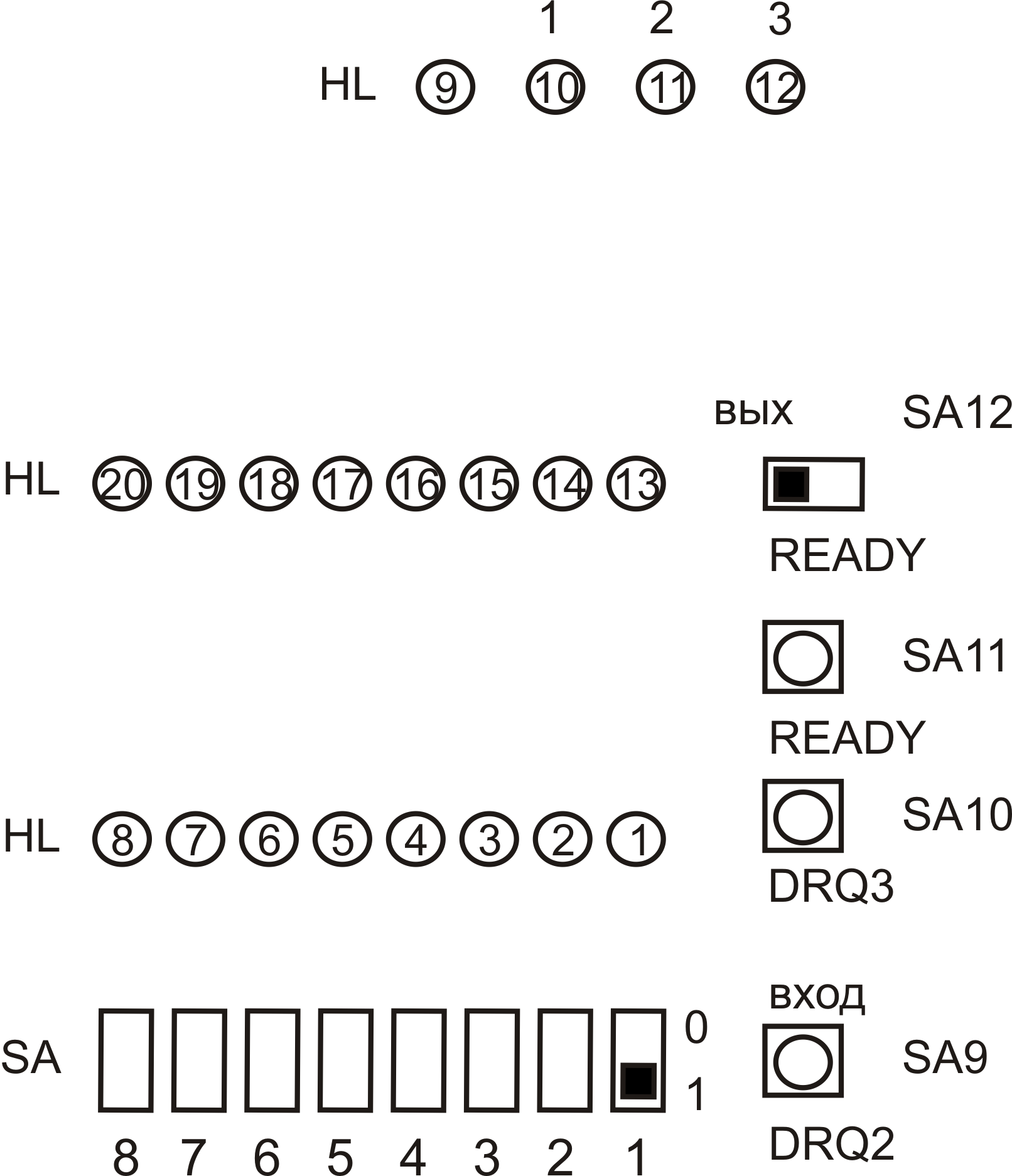

Рис. 5.1. Панель КПДП МИ-3

Задание для домашней подготовки

3.1. Ознакомиться с устройством, работой и программированием контроллера прямого доступа к памяти КР580ВТ57

3.2. Изучить программу 5.1 ввода данных с ВУ в ОЗУ и последующего вывода данных из ЗУ на светодиоды ВУ.

Задание к лабораторной работе

4.1. Набрать программу 5.1. Снять блокировку сигнала HOLD ключом S2.2 – вниз. Запрограммировать КПДП, запустив программу кн. «П».

4.2. Вводить данные с ВУ ключами SA1 – SA8 (нажатием ключей вниз устанавливается 1 и зажигается соответствующий контрольный индикатор на HL1 – HL18).

Нажатием кнопки SA-9 подать запрос – DRQ2 при этом если сигнал на входе контроллера READY – низкого уровня (ключ SA12 влево кнопка SA11 не нажата) контроллер переходит в состояние ожидания сигнала READY. Для записи байта данных в память – нажать кн. SA11 или ключ SA12 – вправо. При положении SA12 право (READY=1) данные записываются сразу после подачи сигнала DRQ (кн. SA9). Проконтролировать запись первого байта светодиодом HL9 – HL16 на панели ВМ.

Набрать следующий байт данных на ВУ кл. SA1 – SA8. Сигналами DRQ2 и READY – ввести его в следующую ячейку памяти. Таким же образом ввести вест блок массива из 5 байтов.

Построить временную диаграмму сигналов по DB0 – DB7, DRQ, RDY, DACK2. Попытаться ввести шестой байт данных.

Проверить правильность записанных значений в ячейках 0900 – 0905. Используя кн. «Ст.» от А «ЗПУ» в ВМ, описать порядок и результат исследований в отчете.

4.3. Вывести данные из ячеек памяти 0900 на ВУ. Светодиоды HL(13-20) через 3-й канал, используя сигналы: DRQ-3 (SA10); READY – (кн. SA-12 – вправо или кн. SA12 влево и нажатием SA-11).