- •Безпека інформаційно- комунікаційних систем

- •Isbn 966-552-167-5

- •1.1. Термінологія

- •1.1.1. Системи, в яких здійснюється захист інформації

- •1.1.2. Завдання захисту інформації

- •1.1.3. Загрози і вразливості

- •1.1.4. Комплексна система захисту інформації

- •1.1.5. Об'єкти захисту та їхні властивості

- •1.1.6. Розроблення й оцінювання захищених систем

- •1.2. Загрози безпеці інформації

- •1.2.1. Класифікація загроз

- •1.2.2. Перелік типових загроз безпеці

- •1.2.3. Класифікація атак

- •1.2.4. Методика класифікації загроз stride

- •1.2.5. Модель загроз

- •1.3. Порушники

- •1.3.1. Визначення терміну «хакер»

- •1.3.2. Наслідки віддій порушників

- •1.3.3. Модель порушника

- •2.1. Рівні інформаційно-комунікаційної системи

- •2.2. Функціональні сервіси безпеки і механізми, що їх реалізують

- •2.2.1. Таксономія функцій систем захисту

- •2.3. Основні підсистеми комплексу засобів захисту

- •2.3.1. Підсистема керування доступом

- •2.3.2. Підсистема ідентифікації й автентифікації

- •2.3.3. Підсистема аудита

- •Підсистема забезпечення цілісності

- •Криптографічна підсистема

- •3.1. Історична довідка

- •3.2. Основні поняття

- •3.3.1. Симетричне шифрування

- •3.3.2. Асиметричне шифрування

- •4.1. Загальні поняття теорії захисту інформації

- •4.2. Позначення, аксіоми та визначення

- •4.3. Основні типи політик безпеки

- •4.4. Математичні моделі безпеки

- •4.4.1. Моделі дискреційної політики безпеки

- •4.4.2. Моделі мандатної політики безпеки

- •5.1. Передумови виникнення вразливостей у комп'ютерних системах

- •5.2. Класифікація вад захисту

- •5.2.1. Класифікація вад захисту за причиною їх появи

- •5.2.2. Класифікація вад захисту за їх розміщенням у системі

- •5.2.3. Класифікація вад захисту за етапами їх появи

- •5.3. Класифікація помилок, що виникають у процесі програмної реалізації системи

- •5.4. Помилки переповнення буфера

- •5.4.1. Переповнення буфера у стеку

- •5.4.2. Переповнення буфера у статичній або динамічній пам'яті

- •5.4.3. Помилка переповнення в один байт

- •5.5. Помилки оброблення текстових рядків

- •5.5.1. Використання конвеєра

- •5.5.2. Переспрямування введення-виведення

- •5.5.3. Спеціальні символи

- •5.6. Люки

- •5.6.1. Режим debug у програмі sendmail

- •6.1. Класифікація шкідливого програмного забезпечення

- •6.2. Програмні закладки

- •6.2.1. Функції програмних закладок

- •6.2.2. Шпигунські програми

- •6.2.3. «Логічні бомби»

- •6.2.4. Люки — утиліти віддаленого адміністрування

- •6.2.5. Несанкціонована робота з мережею

- •6.2.6. Інші програмні закладки

- •6.3. Комп'ютерні віруси

- •6.3.1. Файлові віруси

- •6.3.2. Завантажувальні віруси

- •6.3.3. Макровіруси

- •6.3.4. Скриптові віруси

- •6.3.5. Захист від комп'ютерних вірусів

- •6.4. Мережні хробаки

- •6.4.1. Класифікація мережних хробаків

- •6.4.2. Хробак Морріса

- •6.4.3. Сучасні мережні хробаки

- •6.5. «Троянські коні»

- •6.5.1. Соціальна інженерія

- •6.5.2. Класифікація «троянських коней»

- •6.5.3. Шпигунські троянські програми

- •6.5.4. Троянські інсталятори

- •6.5.5. «Троянські бомби»

- •6.6. Спеціальні хакерські утиліти

- •6.6.1. Засоби здійснення віддалених атак Засоби проникнення на віддалені комп'ютери

- •6.6.2. Засоби створення шкідливого програмного забезпечення

- •6.6.3. Створення засобів атак

- •7.1. Призначення стандартів інформаційної безпеки

- •7.2. Стандарти, орієнтовані на застосування військовими та спецслужбами

- •7.2.1. «Критерії оцінювання захищених комп'ютерних систем» Міністерства оборони сша

- •7.2.2. Інтерпретація і розвиток tcsec

- •7.2.3. Керівні документи Державної технічної комісії при Президенті Російської Федерації

- •7.3. Стандарти, що враховують специфіку вимог захисту в різних системах

- •7.3.1. Європейські критерії безпеки інформаційних технологій

- •7.4. Стандарти, що використовують

- •7.4.1. Концепція профілю захисту

- •7.4.2. Федеральні критерії безпеки

- •8.1. Законодавча і нормативна база захисту

- •8.1.1. Закон України «Про захист інформації

- •8.1.2. Нормативні документи системи

- •8.2. Оцінювання захищеності інформації,

- •8.2.1. Особливості термінології

- •8.2.2. Критерії захищеності інформації в комп'ютерних системах від несанкціонованого доступу

- •8.2.3. Класифікація автоматизованих систем

- •8.3. Керівні документи з вимогами до захисту інформації в інформаційних системах певних типів

- •8.3.1. Вимоги із захисту конфіденційної інформації

- •8.3.2. Вимоги до захисту інформації веб-сторінки від несанкціонованого доступу

- •9.1. Основні відомості

- •9.2. Базові поняття

- •9.3.2. Оцінювання об'єкта за «Загальною методологію»

- •9.3.3. Матеріали, необхідні для проведення кваліфікаційного аналізу

- •9.3.4. Три етапи здійснення кваліфікаційного аналізу

- •9.4. Структура основних документів «Загальних критеріїв»

- •9.4.1. Профіль захисту

- •9.4.2. Завдання з безпеки

- •1. Вступ.

- •5. Вимоги безпеки.

- •8. Обґрунтування.

- •10.1. Завдання апаратного захисту

- •10.2. Підтримка керування пам'яттю

- •10.2.1. Віртуальні адреси

- •10.2.2. Віртуальна пам'ять

- •10.2.3. Трансляція адрес

- •10.4. Особливості архітектури процесорів Intel х86

- •10.4.2. Селектори та дескриптори сегментів і сторінок

- •10.5.2. Сегментно-сторінковий розподіл пам'яті

- •10.6. Керування задачами

- •10.6.1. Виклик процедур

- •10.6.2. Виклик задач

- •10.6.3. Привілейовані команди

- •11.1. Загрози безпеці операційних систем

- •11.1.1. Сканування файлової системи

- •11.1.2. Викрадення ключової інформації

- •11.1.3. Добирання паролів

- •11.1.4. Збирання сміття

- •11.1.5. Перевищення повноважень

- •11.1.6. Програмні закладки

- •11.1.7. «Жадібні» програми

- •11.2. Поняття захищеної операційної системи

- •11.2.1. Підходи до побудови захищених операційних систем

- •11.2.2. Принципи створення захищених систем

- •11.2.3. Адміністративні заходи захисту

- •11.2.4. Політика безпеки

- •11.3.1. Основні функції кзз

- •11.3.2. Розмежування доступу

- •11.3.3. Ідентифікація, автентифікація й авторизація

- •11.3.4. Аудит

- •12.1. Історія створення unix

- •12.2. Архітектура системи

- •12.3.1. Модель безпеки системи unix

- •12.3.2. Підсистема ідентифікації й автентифікації

- •12.3.3. Підсистема розмежування доступу

- •12.3.4. Підсистема реєстрації

- •12.4. Адміністрування засобів безпеки unix 12.4.1. Особливості адміністрування

- •12.4.2. Утиліти безпеки

- •12.4.3. Характерні вразливості системи unix

- •13.1. Основні відомості про систему

- •13.1.1. Стисло про історію створення системи

- •13.1.2. Відповідність вимогам стандартів безпеки

- •13.2.1. Основні концепції

- •13.2.2. Компоненти системи захисту

- •13.3. Розмежування доступу

- •13.3.1. Основні принципи реалізації системи розмежування

- •13.3.2. Суб'єкти доступу Windows

- •13.3.3. Об'єкти доступу Windows

- •13.3.4. Стандартні настроювання прав доступу

- •13.3.5. Ідентифікація й автентифікація

- •13.3.6. Реалізація дискреційного керування доступом

- •13.4. Аудит

- •14.1. Обґрунтування застосування захищених ос для створення систем оброблення конфіденційної інформації

- •14.2. Система Trusted Solaris

- •14.2.1. Основні характеристики середовища Trusted Solaris

- •14.2.2. Керування доступом у середовищі Trusted Solaris

- •14.2.3. Окреме зберігання позначеної мітками

- •14.2.4. Адміністрування безпеки у середовищі Trusted Solaris

- •14.3. Операційна система Фенікс

- •14.3.1. Архітектура системи

- •14.3.2. Засоби захисту

- •14.3.3. Дискреційна модель ієрархічного керування

- •14.3.4. Засоби керування доступом

- •14.3.5. Перегляд протоколу аудита

- •14.3.5. Програмні інтерфейси системи

- •14.3.7. Застосування операційної системи Фенікс

- •15.1. Основні відомості про комп'ютерні мережі

- •15.1.1. Відкриті системи

- •15.1.2. Модель взаємодії відкритих систем

- •15.1.3. Стеки протоколів

- •15.2. Інтернет

- •15.2.1. Організація

- •15.2.2. Адресація

- •15.2.3. Маршрутизація

- •15.3. Загрози безпеці інформації у мережах

- •15.4. Безпека взаємодії відкритих систем

- •15.4.1. Сервіси безпеки

- •15.4.2. Специфічні механізми безпеки

- •15.4.3. Універсальні механізми безпеки

- •15.4.5. Подальший розвиток міжнародних стандартів

- •16.1. Протоколи прикладного рівня

- •16.1.1. Протокол Telnet

- •16.1.2. Протокол ftp

- •16.1.3. Мережні служби unix

- •16.2. Транспортні протоколи

- •16.2.1. Протокол udp

- •16.2.2. Протокол tcp

- •16.3. Протокол ip

- •16.3.1. Призначення й можливості протоколу iPv4

- •16.3.2. Атаки на протокол iPv4, пов'язані з адресацією Підміна адреси відправника

- •16.3.3. Атаки, що ґрунтуються на помилках оброблення фрагментованих пакетів

- •16.3.4. Можливості, закладені у протокол iPv6

- •16.4.1. Особливості протоколу

- •16.4.2. Модель загроз

- •16.4.3. Механізми захисту

- •16.4.4. Рішення з безпеки

- •Interdomain Route Validation

- •16.4.5. Оцінювання захищеності

- •16.5. Протоколи керування мережею 16.5.1. Протокол ісмр

- •16.5.2. Протокол snmp

- •17.1. Система електронної пошти

- •17.1.1. Архітектура системи електронної пошти

- •17.1.2. Формат повідомлення електронної пошти

- •17.1.3. Протокол smtp

- •17.1.4. Протокол рорз

- •17.1.5. Протокол імар4

- •17.1.6. Загрози, пов'язані з використанням електронної пошти

- •17.1.7. Анонімне відсилання електронної пошти

- •17.1.8. Атаки через систему електронної пошти

- •17.2.1. Принципи веб-технології

- •17.2.2. Протокол http

- •17.2.3. Динамічні сторінки

- •17.2.4. Уразливості серверного програмного забезпечення

- •17.2.5. Уразливості у сценаріях

- •17.2.7. Міжсайтовий скриптінг

- •17.2.8. Захист сервера від атак

- •17.2.9. Атака на клієнта

- •17.2.10. Безпека Java

- •18.1. Архітектура захищених мереж

- •18.1.1. Протидія прослуховуванню трафіку

- •18.1.2. Сегментація мережі

- •18.1.3. Резервування мережного обладнання і каналів зв'язку

- •18.2. Міжмережні екрани

- •18.2.1. Можливості міжмережних екранів

- •18.2.2. Рівні реалізації

- •18.2.3. Особливості персональних брандмауерів

- •18.2.4. Недоліки міжмережного екрана

- •18.3. Системи виявлення атак

- •18.3.1. Можливості систем виявлення атак

- •18.3.2. Різні типи систем виявлення атак

- •18.3.3. Інформаційні джерела

- •18.3.4. Аналіз подій у системах виявлення атак

- •18.3.5. Відповідні дії систем виявлення атак

- •18.4. Додаткові інструментальні засоби

- •18.4.1. Системи аналізу й оцінювання вразливостей

- •18.4.2. Перевірка цілісності файлів

- •Передавання інформації через захищені мережі

- •19.1. Захист інформації, що передається відкритими каналами зв'язку

- •19.2. Віртуальні захищені мережі

- •19.2.1. Різні види віртуальних захищених мереж

- •Vpn віддаленого доступу

- •19.2.2. Проблеми побудови віртуальних захищених мереж

- •19.3. Рівні реалізації віртуальних захищених мереж

- •19.3.1. Захист віртуальних каналів на сеансовому рівні

- •19.3.2. Захист віртуальних каналів на мережному рівні

- •19.3.3. Захист віртуальних каналів на канальному рівні

- •19.4. Вимоги нормативної бази до реалізації віртуальних захищених мереж в Україні

- •20.1. Порядок проведення робіт зі створення комплексної системи захисту інформації

- •20.1.1. Структура комплексної системи захисту інформації

- •20.1.2. Створення комплексної системи захисту інформації

- •Обґрунтування потреби у створенні системи захисту

- •20.2.2. Обстеження середовищ функціонування

- •20.2.3. Визначення й аналіз можливих загроз безпеці

- •20.2.4. Розроблення політики безпеки

- •20.2.5. Перелік вимог до захищеної системи

- •20.3. Розроблення технічного завдання на створення комплексної системи захисту інформації

- •20.4. Створення і впровадження комплексної системи захисту інформації

- •20.4.1. Розроблення проекту Порядок розроблення проекту

- •20.4.2. Введення комплексної системи захисту інформації в дію та оцінювання захищеності інформації в інформаційно-телекомунікаційних системах

- •20.4.3. Супроводження комплексної системи захисту інформації

- •21.1. Вимоги до кваліфікаційного аналізу

- •21.2. Організація державної експертизи

- •21.2.1. Положення про державну експертизу

- •21.2.2. Рекомендації з оформлення програм і методик проведення експертизи комплексної системи захисту інформації

- •21.3. Сертифікація засобів технічного захисту інформації

- •22.1. «Типове положення про службу захисту інформації в автоматизованій системі»

- •22.1.1. Загальні положення

- •22.1.2. Завдання та функції служби захисту інформації

- •22.1.3. Права й обов'язки служби захисту інформації

- •22.1.4. Взаємодія служби захисту інформації з іншими підрозділами та із зовнішніми організаціями

- •22.1.5. Штатний розклад і структура служби захисту інформації

- •22.1.6. Організація заходів служби захисту інформації та їх фінансування

- •22.2. Рекомендації щодо структури

- •22.2.1. Завдання захисту інформації в ас

- •22.2.2. Класифікація інформації, що обробляють в ас

- •22.2.3. Компоненти ас і технології оброблення інформації

- •22.2.4. Загрози інформації в ас

- •22.2.5. Політика безпеки інформації в ас

- •22.2.6. Календарний план робіт із захисту інформації в ас

- •22.3. Iso/iec 27002 «Інформаційні технології — Методики безпеки — Практичні правила управління безпекою інформації»

- •22.3.1. Загальні відомості про стандарт

- •22.3.2. Структура й основний зміст стандарту

- •22.3.3. Інші стандарти серн 27000

- •Грайворонський Микола Владленович Новіков Олексій Миколайович безпека інформаційно-комунікаційних систем

- •21100, М. Вінниця, вул. 600-річчя, 19.

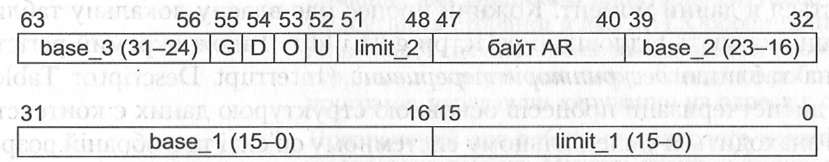

10.4.2. Селектори та дескриптори сегментів і сторінок

Селектор — це 16-розрядна структура, яка завантажується в сегментні регістри (рис. 10.6).

![]()

Рис. 10.6. Формат селектора сегмента

Селектор адресує не сам сегмент, а його дескриптор. Дескриптори розташовані в таблицях, причому в певний момент процесору доступні дві таблиці: глобальна (спільна для всіх процесів) і локальна — таблиця поточного процесу. 13 старших розрядів селектора є індексом у таблиці дескрипторів. Таким чином, кожна таблиця може містити 2,3=8192 дескриптори. Один розряд селектора (біт 2), позначений прапорцем ТІ, вказує на таблицю, де розташовано дескриптор: ТІ=0 вказує на GDT, ТІ=1 — на LDT. Інші 2 розряди селектора (біт 1, біт 0) задають рівень привілеїв (Requested Privilege Level, RPL), що використовує механізм захисту.

Дескриптор

сегмента має 8-байтову структуру. На

рис. 10.7 показано формат дескриптора

сегмента, а в табл. 10.2 наведено значення

його полів. Звернемо увагу на два

найголовніших поля дескриптора:

32-розрядну базову адресу (base)

і

20-розрядну межу сегмента (limit).

Рис.

10.7.

Формат дескриптора сегмента

Базова

адреса вказує на початок сегмента в

пам'яті. На відміну від реального

режиму роботи процесора, в захищеному

режимі передбачено використання

віртуальної пам'яті. Коли було

впроваджено 32-розрядну адресну шину

і в дескрипторі сегмента під базову

адресу виділено 4 байти (2, 3, 4 і 7), тобто

з'явилася можливість прямої адресації

4 Гбайт, обсяг фізичної пам'яті

комп'ютера, побудованого на

процесорах х86, становив 1-2 Мбайт.

Навіть і тепер, майже через 20 років,

комп'ютери архітектури х86 не завжди

мають 4 Гбайт фізичної пам'яті. Тому

32-розрядні адреси, які містять

дескриптори, а також ті, що використовує

процесор для адресації команд та

їхніх операндів (які отримують

додаванням 32-роз- рядного зміщення

до 32-розрядної базової адреси

відповідного сегмента), адресують

віртуальний адресний простір.

Ці

адреси називають лінійними. Перетворення

лінійної адреси на фізичну здійснюють

по-різному, залежно від моделі

використання пам'яті, зокрема від

того, чи застосовується сторінкове

керування.

Таблиця

10.2.

Поля дескриптора сегмента |

Ширина поля |

Символьне |

Призначення і вміст полів |

в дескрипторі |

(розряди) |

позначення |

|

0...1 |

16 |

limit_l |

Молодші 16 розрядів 20-розрядного поля межі сегмента. Межа сегмента визначає його розмір у байтах або 4-кілобайтових сторінках, залежно від значення біта G |

2...3 |

16 |

base_l |

Молодші 16 розрядів 32-розрядного поля бази сегмента. База сегмента визначає лінійну адресу початку сегмента у пам'яті |

4 |

8 |

base_2 |

Розряди 16...23 32-розрядного поля бази сегмента |

5 |

8 |

AR |

Байт захисту |

6 (біти 0...3) |

4 |

limit_2 |

Старші 4 розряди 20-розрядного поля межі сегмента |

6 (біт 4) |

1 |

U (User) |

Біт користувача. Не має спеціального призначення і використовується програмістом на його розсуд |

6 (біт 5) |

1 |

- |

=0 — біт не використовується |

Межа

сегмента визначає його розмір. Якщо

задіяні для цього 20 розрядів

інтерпретувати як розмір у байтах

(коли прапорець гранулярності G

дорівнює 0), то максимальний розмір

сегмента становитиме 1 Мбайт, а якщо

у 4-кілобайтових сторінках (прапорець

гранулярності G

дорівнює 1) — 4 Гбайт.

Окрім

прапорця гранулярності важливий

також для інтерпретації адрес прапорець

розрядності D.

Якщо D

= 0, використовуються 16-розрядні

операнди і ре жими 16-розрядної

адресації, а якщо D

= 1 — 32-розрядні операнди і режими

32-розрядної адресації.

Поля

та прапорці, які стосуються захисту

сегмента, зведені у спеціальний байт

дескриптора, що має назву байт захисту

(позначається AR).

На рис. 10.8 по

казано

формат байта захисту, а в табл. 10.3

наведено призначення полів.

Рис.

10.8.

Формат байта захисту дескриптора

сегмента

Таблиця

10.3.

Поля байта захисту дескриптора

сегмента |

Символьне |

Призначення і вміст полів |

|||

в байті AR |

позначення |

|

|||

0 |

A (Accessed) |

Біт доступу до сегмента. Встановлюється апаратно під час звернення до сегмента |

|||

1 |

R (Readable) |

Для сегментів коду це біт доступу, який визначає право на читання: =0 — читання із сегмента заборонено; =1 — читання із сегмента дозволено |

|||

|

W (Writable) |

Для сегментів даних це біт доступу, який визначає можливість модифікації даних: =0 — записування в сегмент заборонено; = 1 — записування в сегмент дозволено |

|||

Таблиця 10.2 (закінчення) |

|||||

Номер байта в дескрипторі |

Ширина поля (розряди) |

Символьне позначення |

Призначення і вміст полів |

||

6 (біт 6) |

1 |

D (Digit capacity) |

Біт розрядності операндів і адрес. =0 — використовуються 16-розрядні операнди і режими 16-розрядної адресації |

||

6 (біт 7) |

1 |

G (Granularity) |

= 1 — використовуються 32-розрядпі операнди і режими 32-розрядпої адресації Біт гранулярності. =0 — розмір сегмента задається значенням поля limit у байтах (максимальний розмір 1 Мбайт) |

||

7 |

8 |

base_3 |

=1 — розмір сегмента задається значенням поля limit у 4-кілобайтових сторінках (максимальний розмір — 4 Гбайт) Старші 8 розрядів 32-розрядного поля бази сегмента |

||

![]()

Таблиця

10.4.

Значення поля типу сегмента

Таблиця 10.3 (закінчення) |

||

Номер біта |

Символьне |

Призначення і вміст полів |

в байті AR |

позначення |

|

2 |

С (Conforming) |

Для сегментів коду це біт підпорядкованості: =0 — звичайний сегмент коду; =1 — підпорядкований сегмент коду |

|

ED (Expand Down) |

Для сегментів даних це біт розширення вниз, який дає можливість розрізняти сегменти даних і стека, а також визначає трактування поля limit: =0 — сегмент даних (зростає в бік старших адрес); =1 — сегмент стека (зростає в бік молодших адрес) |

3 |

Ε (Execution) |

Біт призначення, який визначає тип сегмента: |

|

або I (Intending) |

=0 — сегмент даних або стека; =1 — сегмент коду |

4 |

S (Segment/System) |

=0 — біт «системний», який вказує на те, що цей дескриптор описує системний об'єкт, який може бути чи не бути сегментом у пам'яті '=1 — біт «сегмент», який вказує, що цей дескриптор описує сегмент, тип якого і порядок використання уточнюються бітами I, C/ED, R/W |

5...6 |

DPL (Descriptor |

Рівень привілеїв сегмента, який визначає рівень |

|

Privilege Level) |

виконання від 0 до 3. (0 — найвищий рівень, який зазвичай використовується для ядра ОС, 3 — найнижчий рівень) |

7 |

Ρ (Present) |

Біт присутності: =0 — сегмента в поточний момент в оперативній пам'яті немає; =1 — сегмент у поточний момент знаходиться в оперативній пам'яті |

Хоча

чотири молодші розряди байта захисту

називають полем типу сегмента

(type_seg),

тип

сегмента задається не розрядами

0...3, а розрядами 1...4. Розряд 0 встановлюється

у разі доступу до сегмента і може бути

використаний операційною системою

під час реалізації алгоритмів керування

віртуальною пам'яттю. Розряд 4 визначає

об'єкт, який описує цей дескриптор:

чи він є сегментом у пам'яті, чи

спеціальним системним об'єктом (деякі

системні об'єкти теж являють собою

спеціальні сегменти у пам'яті —

таблиці дескрипторів або сегменти

стану задачі). Розряди 1...3 визначають,

власне, тип сегмента і права доступу

до нього. У табл. 10.4 проілюстровано

сукупну «роботу» цих розрядів. |

Комбінація бітів у полі type_seg |

Тип сегмента |

0 |

0100 |

Таблиця локальних дескрипторів (LDT) |

0 |

0001 |

Сегмент стану задачі (TSS) |

|

1000 |

|

|

1101 |

|

|

1101 |

|

1 |

000х |

Сегмент даних, тільки для читання |

1 |

001х |

Сегмент даних, дозволено читання і записування |

1 |

010х |

Не визначено |

Таблиця

10.4 (закінчення)

Рис.

10.9.

Формат дескриптора сторінки

Таблиця

10.5.

Поля дескриптора сторінки

Окремі

розділи таблиці сторінок може бути

витіснено з фізичної пам'яті на диск.

При цьому кожний розділ таблиці має

розмір 4 Кбайт (210

= 1024 дескриптори) і відтак займає рівно

одну сторінку. Таблиця розділів завжди

присутня у пам'яті, її фізична адреса

міститься в регістрі сгЗ.

Біт S |

Комбінація бітів |

Тип сегмента |

|

у полі type_seg |

|

1 |

011х |

Сегмент стека, дозволено читання і записування |

1 |

100х |

Сегмент коду, дозволено лише виконання |

1 |

101х |

Сегмент коду, дозволено читання і записування |

1 |

110х |

Підпорядкований сегмент коду, дозволено лише виконання |

1 |

111х |

Підпорядкований сегмент коду, дозволено читання і виконання |

Ще

два розряди байта захисту дескриптора

— 5 і 6 — визначають рівень привілеїв

дескриптора (Descriptor

Privilege

Level,

DPL).

Разом із рівнем привілеїв селектора

RPL

і поточним рівнем привілеїв процесу,

що виконується (Current

Privilege

Level,

CPL),

ці рівні дають змогу організувати

розмежування доступу до сегментів

за мандатним принципом (так звані

кільця захисту) [91].

Якщо

включено сторінковий механізм

керування пам'яттю (біт pg

регістра

сг0 дорівнює 1), то з дескриптора

визначається лінійна базова адреса

сегмента, а після додавання до неї

зміщення — лінійна адреса даних. Для

обчислення фізичної адреси здійснюється

сторінкове перетворення. Більш

докладно цей процес буде розглянуто

далі, а тепер звернемо увагу лише на

пов'язані з ним структури даних.

Лінійна

адреса — 32-розрядна, старші 20 розрядів

інтерпретуються як номер сторінки,

а молодші 12 — як зміщення у сторінці.

Номер сторінки інтерпретується як

індекс дескриптора сторінки, а з

дескриптора визначається номер у

фізичній пам'яті, який водночас

становить старші 20 розрядів 32-розрядної

фізичної базової адреси сторінки. На

рис. 10.9 показано формат дескриптора

сторінки, а в табл. 10.5 наведено значення

його полів. |

Символьне |

Призначення і вміст полів |

біта |

позначення |

|

0 |

Ρ (Present) |

Прапорець наявності сторінки у фізичній пам'яті |

1 |

W (Writable) |

Прапорець дозволу записування у сторінку |

2 |

U (User mode) |

Прапорець користувач/супервізор |

3 |

PWT |

Керують механізмом кешування сторінок (введені |

4 |

PCD |

починаючи з процесора 80486) |

5 |

A (Accessed) |

Ознака того, чи було здійснено доступ до сторінки |

6 |

D |

Ознака модифікації вмісту сторінки |

7...8 |

0 |

Зарезервовані |

9...11 |

AVL (Available) |

Зарезервовані для потреб операційної системи |

12...31 |

|

Номер сторінки у пам'яті |

![]()

10.5.

Керування оперативною пам'яттю

Як

уже зазначалося, архітектура процесорів

х86 передбачає сегментну і сегментно-сторінкову

моделі розподілу пам'яті. Засоби

сегментної організації формують верхній

рівень керування пам'яттю, а сторінкової

— нижній (який можна вмикати та вимикати

за допомогою прапорця pg

в регістрі сг0) [63, 92].

10.5.1.

Сегментний розподіл пам'яті

У

сегментній моделі пам'яті кожний сегмент

утворює свій окремий адресний простір

(див. рис. 10.1). Кількість сегментів

визначається максимальною кількістю

дескрипторів, яку може обробити процесор.

Як уже зазначалося, кожний процес

використовує одночасно дві таблиці —

LDT

і GDT;

максимальна кількість дескрипторів у

кожній із них визначається розрядністю

індексу з селектора — 13 розрядів. Тобто

в кожній таблиці може міститися до 213

дескрипторів, загалом — 16k

(16

384) сегментів. З цього випливає, що в

такому режимі кожний процес може

мати 16k

*

4 Гбайт = 64 Тбайт віртуального адресного

простору.

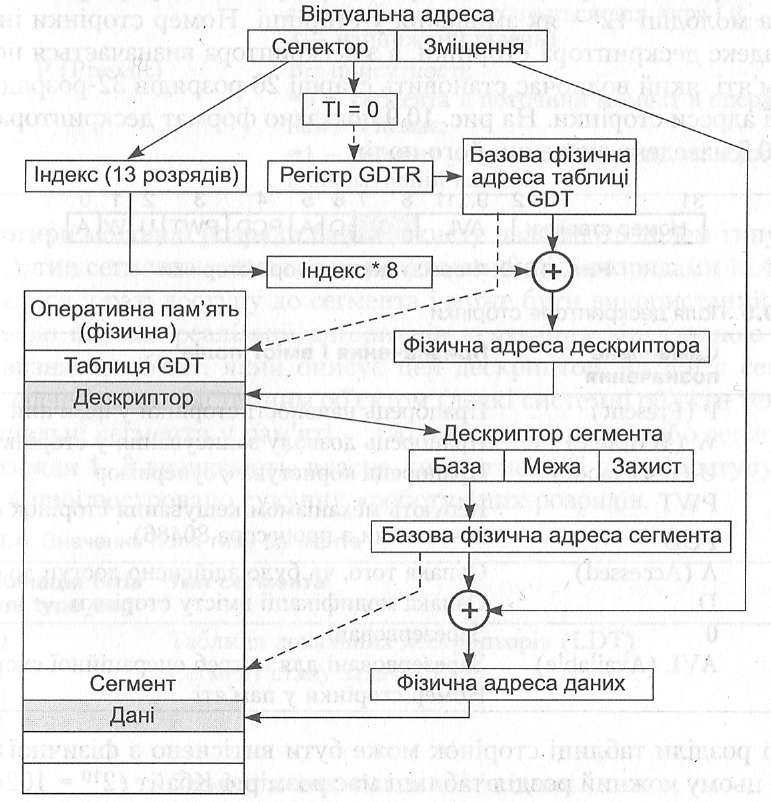

Розглянемо

механізм трансляції адреси, коли

процесор працює в такому режимі

(рис. 10.10, 10.11).

Рис.

10.10.

Механізм перетворення віртуальної

адреси на фізичну, коли процесор х86

функціонує в сегментному режимі з

використанням дескриптора сегмента з

таблиці GDT

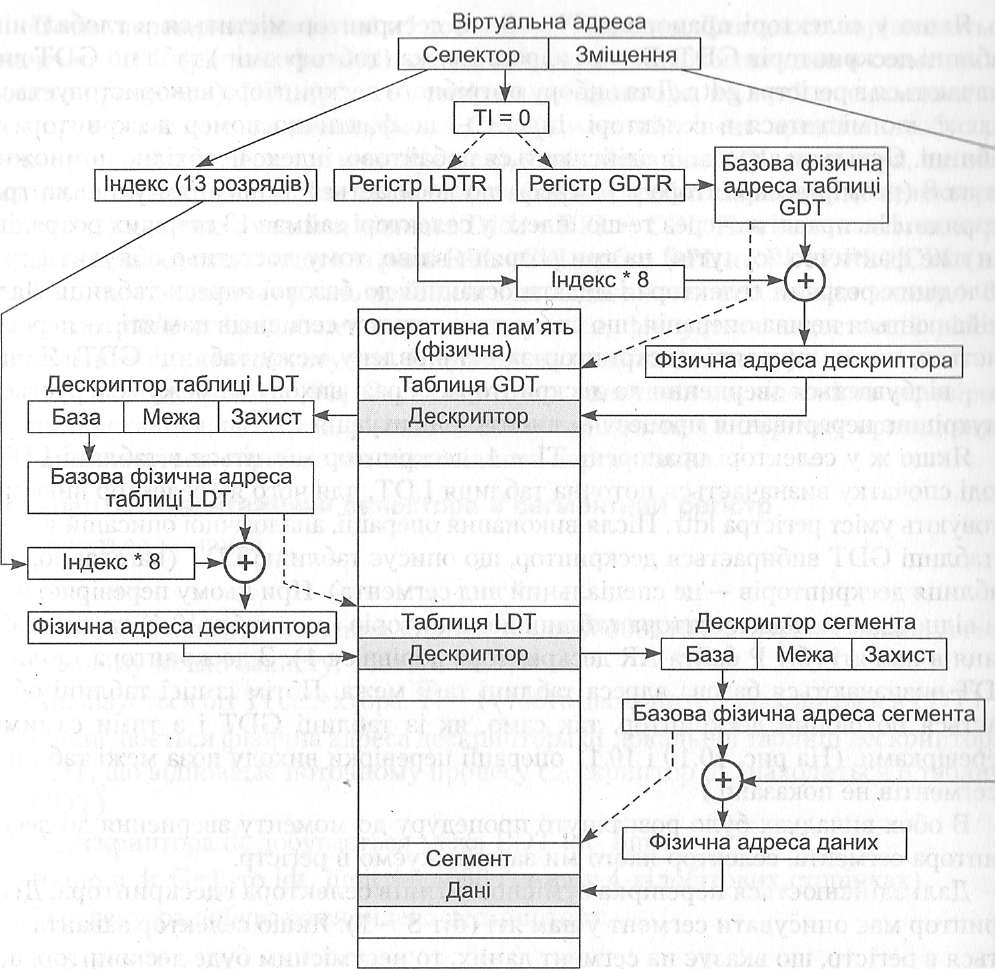

Рис.

10.11.

Механізм перетворення віртуальної

адреси на фізичну, коли процесор х86

функціонує в сегментному режимі з

використанням дескриптора сегмента з

таблиці LDT

Цей

механізм ініціюється за спроби звернутися

до будь-яких даних у пам'яті (наприклад,

коли дані завантажуються в регістр

процесора чи записуються з peгiстра

в пам'ять, та під час роботи зі стеком)

або до нового сегмента (завантаження

селектора в сегментний регістр).

Принципово цей механізм відповідає

схемі, наведеній на рис. 10.3. Насправді-ж

перша частина алгоритму виконується

лише під час завантаження селектора в

сегментний регістр. Якщо здійснюється

доступ до даних всередині сегмента,

пошук дескриптора сегмента не виконується,

позаяк процесор має спеціальні

64-розрядні регістри для зберігання

дескрипторів, що відповідають завантаженим

у сегментні регістри селекторам. Ці

дескрипторні регістри є тіньовими,

програмно недоступними. Дескриптор

завантажується разом із селектором.

Завантаження

селектора в сегментний регістр

Розглянемо

процедуру завантаження селектора в

сегментний регістр. Спочатку процесор

має знайти у пам'яті відповідний

дескриптор і здійснити необхідні

перевірки.

Якщо

у селекторі прапорець ТІ = 0, то

дескриптор міститься в глобальній

таблиці дескрипторів GDT.

Базова

адреса і межа (тобто розмір) таблиці

GDT

визначаються

з регістра gdtr.

Для

вибору потрібного дескриптора

використовується індекс, що міститься

в селекторі. Індекс — це фактично

номер дескриптора в таблиці. Оскільки

адресація здійснюється побайтово,

індекс необхідно помножити на 8

(розмір дескриптора в байтах), що

досягається зміщенням уліво на три

розряди. Насправді ж, через те що

індекс у селекторі займає 13 старших

розрядів, він вже фактично зсунутий

на три розряди вліво, тому достатньо

обнулити три молодших розряди селектора

і додати останній до базової адреси

таблиці. Далі здійснюється перша

операція, що стосується захисту

сегментів пам'яті, — перевіряється,

чи не виходить дескриптор за встановлену

межу таблиці GDT.

Якщо

ні — відбувається звернення до

дескриптора. У разі виходу за межу

генерується внутрішнє переривання

процесу — виняткова ситуація 11.

Якщо

ж у селекторі прапорець ТІ = 1, дескриптор

міститься в таблиці LDT.

Тоді

спочатку визначається поточна таблиця

LDT,

для

чого як селектор використовують

уміст регістра Idtr.

Після

виконання операції, аналогічної

описаній вище, з таблиці GDT

вибирається

дескриптор, що описує таблицю LDT

(нагадаємо, що таблиця дескрипторів

— це спеціальний вид сегмента). При

цьому перевіряється, чи відповідає

тип дескриптора таблиці дескрипторів

(див. табл. 10.4) та чи є таблиця в

пам'яті (біт Ρ байта AR

дескриптора дорівнює 1). З дескриптора

таблиці LDT

визначаються

базова адреса таблиці та її межа.

Потім із цієї таблиці обирається

потрібний дескриптор, так само, як із

таблиці GDT

і з тими самими перевірками. (На рис.

10.10 і 10.11 операції перевірки виходу

поза межі таблиць і сегментів не

показано.)

В

обох випадках було розглянуто процедуру

до моменту звернення до дескриптора

сегмента, селектор якого ми завантажуємо

в регістр.

Далі

здійснюється перевірка сумісності

типів селектора і дескриптора.

Дескриптор має описувати сегмент

у пам'яті (біт S

= 1). Якщо селектор завантажується

в регістр, що вказує на сегмент даних,

то несумісним буде дескриптор, що

описує сегмент коду із захистом від

читання (біт Ε = 1, біт R

= 0). Якщо селектор завантажується

в регістр cs,

то

сумісним буде лише сегмент коду, і

аналогічно під час завантаження

селектора в регістр ss

сумісним

буде лише сегмент стека (табл. 10.6).

Очевидно, більш суворі умови сумісності

для сегментів стека і коду спрямовані

на запобігання «підсовування»

процесору зловмисного коду через

сегменти даних. У випадку коли перевірка

дає негативний результат, фіксується

несумісність типів — генерується

виняткова ситуація 13 (загальна помилка

захисту).

Таблиця

10.6.

Дозволені комбінації бітів байта

захисту дескриптора під час виконання

операції завантаження селектора в

сегментний регістр |

Ρ |

DPL |

S |

Ε |

C/ED |

R/W |

Α |

Примітка |

CS |

χ |

χ χ |

1 |

1 |

χ |

χ |

χ |

Сегмент коду |

SS |

χ |

χ χ |

1 |

0 |

1 |

1 |

χ |

Сегмент стека |

ds, es, fs, gs |

χ |

χ χ |

1 |

1 |

χ |

1 |

χ |

Сегмент коду |

0 |

χ |

χ |

χ |

Сегмент даних або стека |

Потім перевіряються привілеї доступу до сегмента. Для цього порівнюються значення RPL (рівень привілеїв селектора, який ми завантажуємо в сегментний регістр процесора), DPL (рівень привілеїв дескриптора, на який посилається се лектор, що ми його завантажуємо) і CPL (поточний рівень привілеїв, тобто рівень привілеїв процесу, що виконується), який дорівнює RPL селектора, що зна ходиться в регістрі cs). Для сегмента стека (за спроби завантажити селектор у регістр ss) має виконуватися рівність DPL = RPL = CPL. Для решти сегментів рівень DPLMae бути не вищим за рівні RPLi CPL, тобто DPL > RPL і DPL >CPL (па гадаємо, що найвищому рівню привілеїв відповідає значення 0, а найнижчому-3).

Якщо потрібне співвідношення не виконується, фіксується недостатній рівень

привілеїв — виняткова ситуація 13 (загальна помилка захисту).

Розглянемо приклад [91]. Зауважимо, що, описуючи послідовність перевірок, ми припускалися, що у разі фіксації помилки виконання алгоритму припиняється і викликається оброблювач відповідного переривання.

Приклад 1. Завантаження селектора в сегментний регістр

Виконується команда

mov. ds, ах

Регістр ах містить значення 0x37 = 0000000000110111. Процес виконується в нульовому кільці захисту, тобто CPL = 0.

Аналізується біт ТІ селектора. ТІ = 1 (тобто дескриптор знаходиться в LDT).

Обчислюється фізична адреса дескриптора dt локальної таблиці дескрипторів LDT, що відповідає поточному процесу (дескриптор dt знаходиться в таблиці GDT).

З дескриптора dt добувається межа LDT ldt limit.

Якщо в dt G=l, то ldt_limit *= 4096 (межа у 4-кілобітових сторінках).

Із селектора добувається індекс дескриптора:

index = 6

Перевіряється, чи не виходить індекс за межі таблиці LDT:

(index +1) * 8 - 1 = 55

Якщо ldt_limit < 55, фіксується некоректність селектора (помилка 11).

З таблиці LDT добувається дескриптор d сегмента:

offset = index * 8 = 48; d_addr = ldt_base + offset

Якщо в d біт S = 0 або одночасно Ε = 1 і R = 0, фіксується несумісність типів селектора і

регістра (помилка 13).

Із селектора добувається RPL:

RPL = 3

Порівнюються CPL, RPL і DPL:

CPL = 0, RPL = З

Якщо DPL < 3, фіксується недостатній рівень привілеїв (помилка 13).

Селектор

із регістра ах завантажується в

регістр ds,

тоді ж дескриптор d

завантажується в дескрипторний

регістр, що відповідає регістру ds.

Звернення

до пам'яті

Під

час звернення до пам'яті у разі її

сегментного розподілу перевіряється,

чи дозволено операцію та чи коректно

здійснено доступ. Обмеження для

команди зчитування з пам'яті встановлено

лише для сегментів коду (біт Ε = 1): якщо

біт R

=

0 — читання заборонено. Для команди

записування в пам'ять сегмент коду —

взагалі несумісний тип, а всі інші

типи сегментів можуть бути захищені

бітом W:

якщо W

= 0, записування заборонено. В усіх

згаданих випадках генерується

виняткова ситуація 13 (загальна

помилка захисту). У табл. 10.7 наведено

дозволені комбінації бітів байта

захисту.

Таблиця

10.7. Дозволені комбінації бітів байта

захисту під час виконання операцій

звернення до пам'яті |

Ρ |

DPL |

S |

Ε |

C/ED |

R/ W |

Α |

Примітка |

Зчитування з пам'яті |

1 1 |

Χ χ χ χ |

1 1 |

0 1 |

χ χ |

χ 1 |

χ χ |

Сегмент даних або стека Сегмент коду |

Записування в пам'ять |

1 |

χ χ |

1 |

0 |

χ |

1 |

χ |

Сегмент даних або стека |

Щоб

перевірити коректність доступу,

перевіряється, чи не виходить адреса

за межу сегмента. Перевірка здійснюється

з урахуванням розміру даних і напрямку

зростання сегмента. Якщо сегмент є

сегментом стека (біт Ε = 0 та біт ED

=

1), то він зростає в бік молодших адрес,

і тоді обчислена адреса має бути не

меншою за межу сегмента. Якщо ж сегмент

є сегментом коду (біт Ε = 1) або даних

(біт Ε = 0 та біт ED

= 0), він зростає в бік старших адрес,

тому до обчисленої адреси додається

розмір даних (для команди mov

— залежно від того, який із регістрів

процесора бере участь у передаванні-прийманні

даних) і отримана адреса має бути не

більшою за межу сегмента. За наявності

помилки генерується виняткова ситуація

13 (загальна помилка захисту).

Розглянемо

такий приклад [91].

Приклад

2. Звернення до пам'яті

Виконується

команда

mov

es:[ebx+4],еах

Перевіряється

біт Ε дескриптора d,

завантажений

у дескрипторний регістр,

який

відповідає сегментному регістру es.

Якщо

Ε = 1, фіксується спроба запису в сегмент

коду (помилка 13).

Перевіряється

біт W

дескриптора

d.

Якщо

W

=

1, фіксується спроба запису

в сегмент,

захищений від запису (помилка 13).

Із

сегмента d

добувається

межа сегмента seg_limit.

Якщо

в d

значення

G=l,

то

seg_limit

*=

4096 (межа у 4-кілобайтових сторінках).

Обчислюється

зміщення:

offset

=

ebx

+

4

6. Перевіряється відсутність виходу за межу сегмента за таким алгоритмом: Якщо ED = 0 (сегмент даних зростає в бік старших адрес), то порівнюється offset + data_size — 1 = offset + 3 (зміщення останнього байта даних, розмір даних — 4 байти) і seg_limit; якщо offset + 3 > seg_limit, фіксується некоректне звернення (помилка 13).

Інакше, якщо ED = 1 (сегмент стека зростає в бік молодших адрес), то порівнюється offset і seg_limit; якщо offset < seg_limit, фіксується некоректне звернення (помилка 13).

7. З дескриптора d добувається seg_base.

8. Обчислюється адреса seg_base + offset, і в пам'ять за цією адресою заносяться дані з регістра еах.