МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙ РАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра автоматизированных систем управления

Отчет о лабораторной работе № 3

“Основы логических устройств. Комбинационные схемы”

Выполнил

студент гр. 0310

Рогова С.А..

Принял

Холопов С.И.

Рязань – 2012

Цель работы:

Изучение структуры и алгоритмов работы базовых логических элементов.

Исследование основных типов комбинационных схем: шифратора, дешифратора, мультиплексора, демультиплексора и сумматора.

Теоретическая часть:

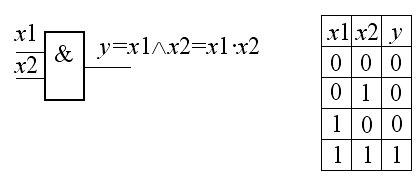

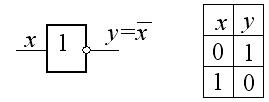

Базовыми логическими элементами являются устройства, выполняющие логические функции конъюнкции (операции И), дизъюнкции (операции ИЛИ) и инверсии (операции НЕ).

Конъюнкцию называют также операцией логического умножения. Логический элемент, реализующий данную функцию, и таблица истинности, иллюстрирующая алгоритм его работы:

Дизъюнкция, в свою очередь, называется операцией логического сложения. Логический элемент, выполняющий указанную функцию, и его таблица истинности:

Отрицание, или инверсия, реализуется элементом, изображенным на следующем рисунке. Здесь же показаны его логическая формула и таблица истинности. В схемном исполнении знак инверсии (кружок) может устанавливаться как на выходе любого логического элемента, так и на его входе. Совместное использование инверсии с элементами конъюнкции и дизъюнкции позволяет построить элементы И-НЕ и ИЛИ-НЕ.

Используя базовые логические элементы, можно реализовать комбинационную логическую схему в соответствии с описывающим ее уравнением.

К разновидностям стандартных комбинационных схем относят: шифраторы, дешифраторы, мультиплексоры, демультиплексоры и сумматоры.

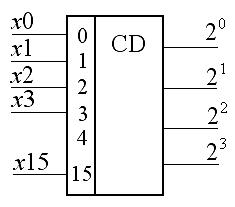

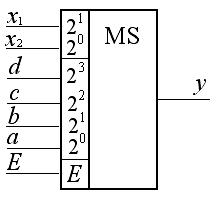

Ш ифратор,

или кодер (CD), выполняет функцию

преобразования унитарного (позиционного)

кода в двоичный код.

ифратор,

или кодер (CD), выполняет функцию

преобразования унитарного (позиционного)

кода в двоичный код.

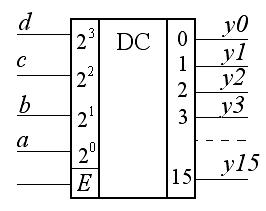

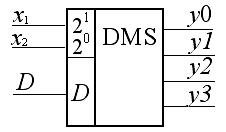

Дешифратор, или декодер (DC), – это комбинационная схема, преобразующая двоичный входной код (кодовое слово) в унитарный.

Мультиплексор (MS) – это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких информационных входов к единственному выходу.

Демультиплексоры (DMS) выполняют функцию, обратную мультиплексорам, т. е. производят коммутацию одного входа на 2n выходов, где n – число адресных выходов.

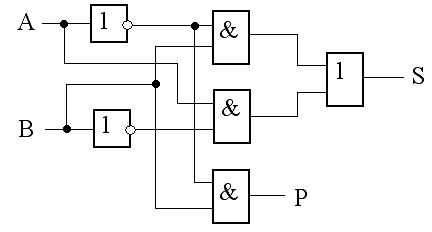

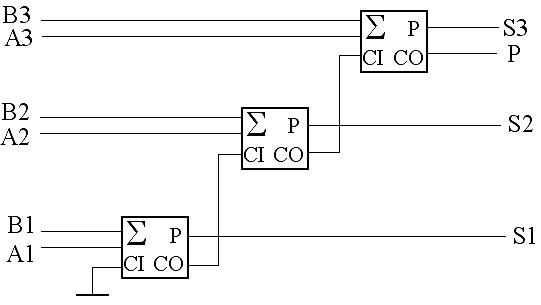

Арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ). Сумматоры представлены двумя базовыми устройствами: полусумматором и полным сумматором.

Полусумматор предназначен для суммирования двух одноразрядных двоичных чисел.

Сумматор – это узел, в котором выполняется арифметическая операция суммирования кодов двух двоичных чисел.

Задание.

№ варианта |

Формула синтезируемого логического устройства |

6 |

|

Выполнение работы:

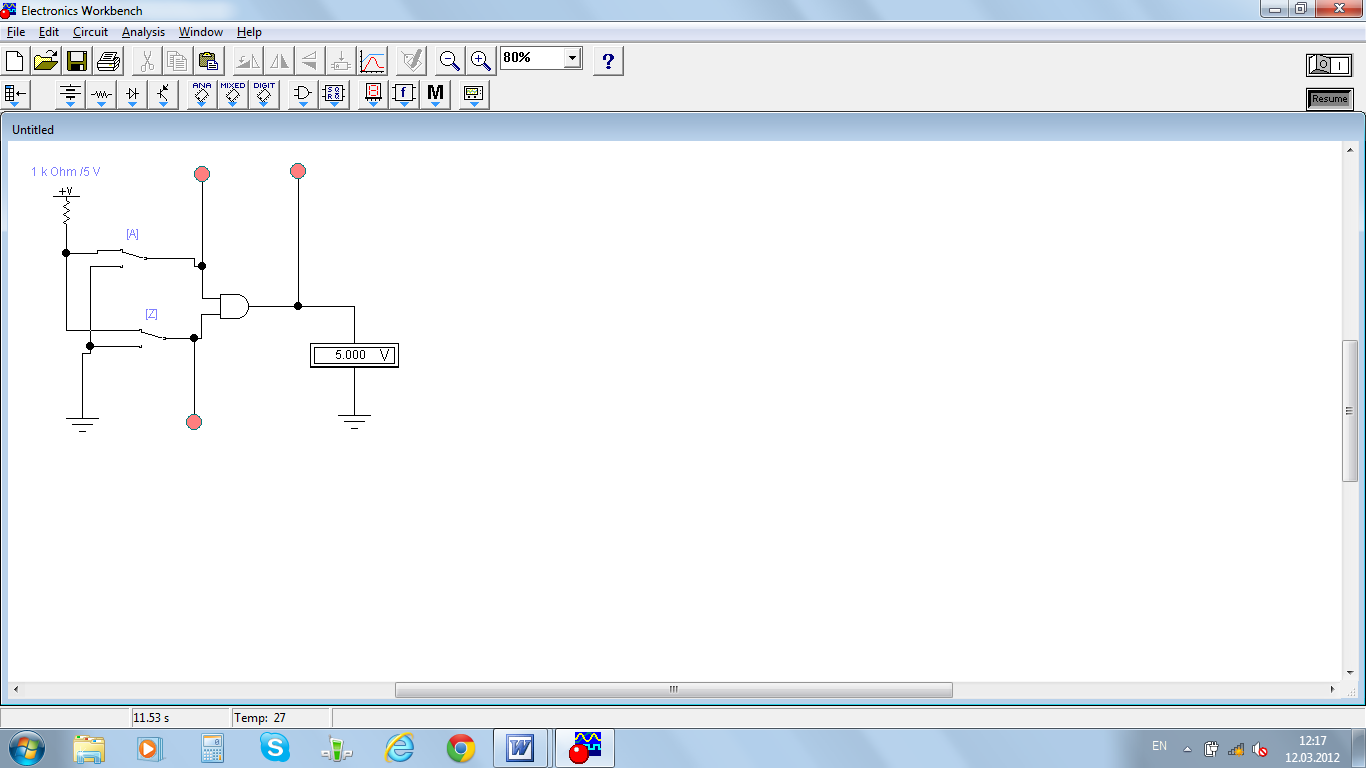

1. Исследование элемента И.

A |

B |

AB |

U, В |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

5 |

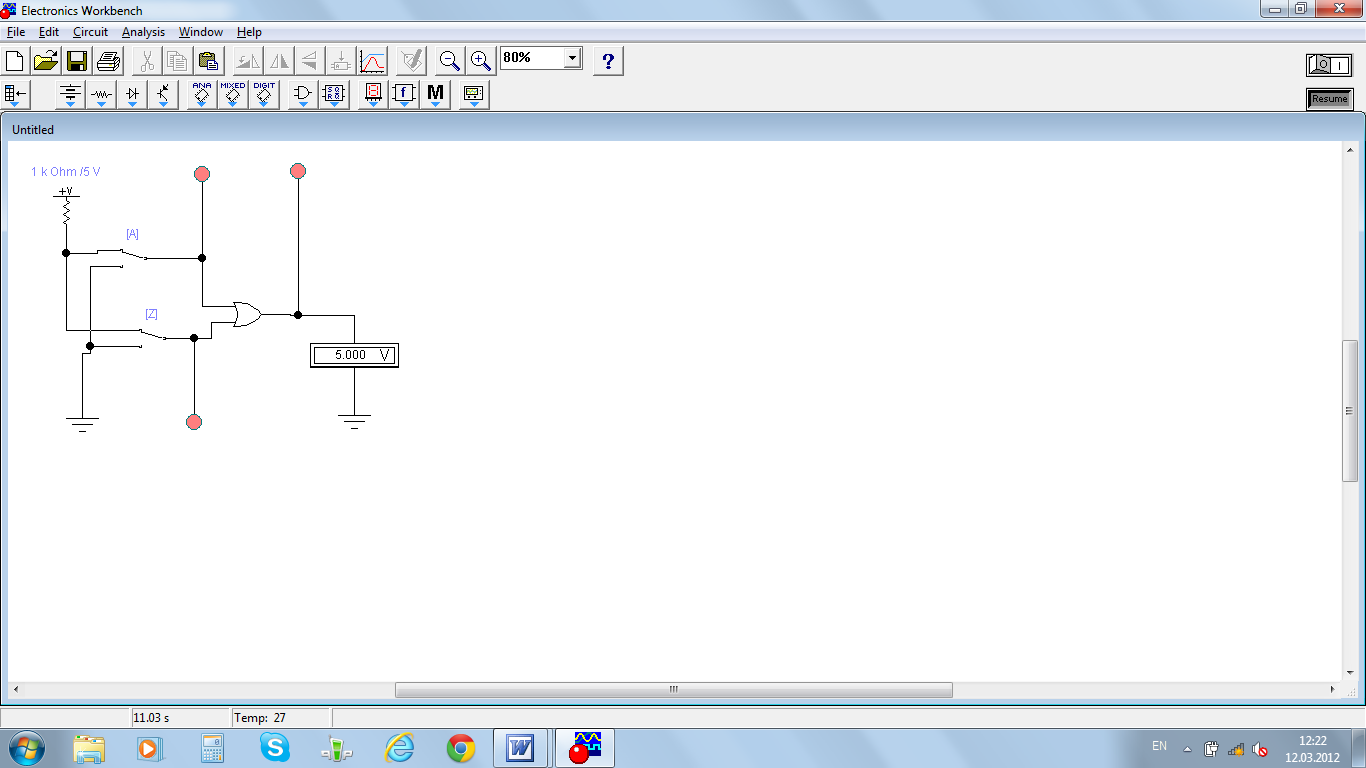

2. Исследование элементов ИЛИ и НЕ.

A |

B |

AvB |

U, В |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

1 |

5 |

1 |

1 |

1 |

5 |

A |

|

U, В |

0 |

1 |

5 |

1 |

0 |

0 |

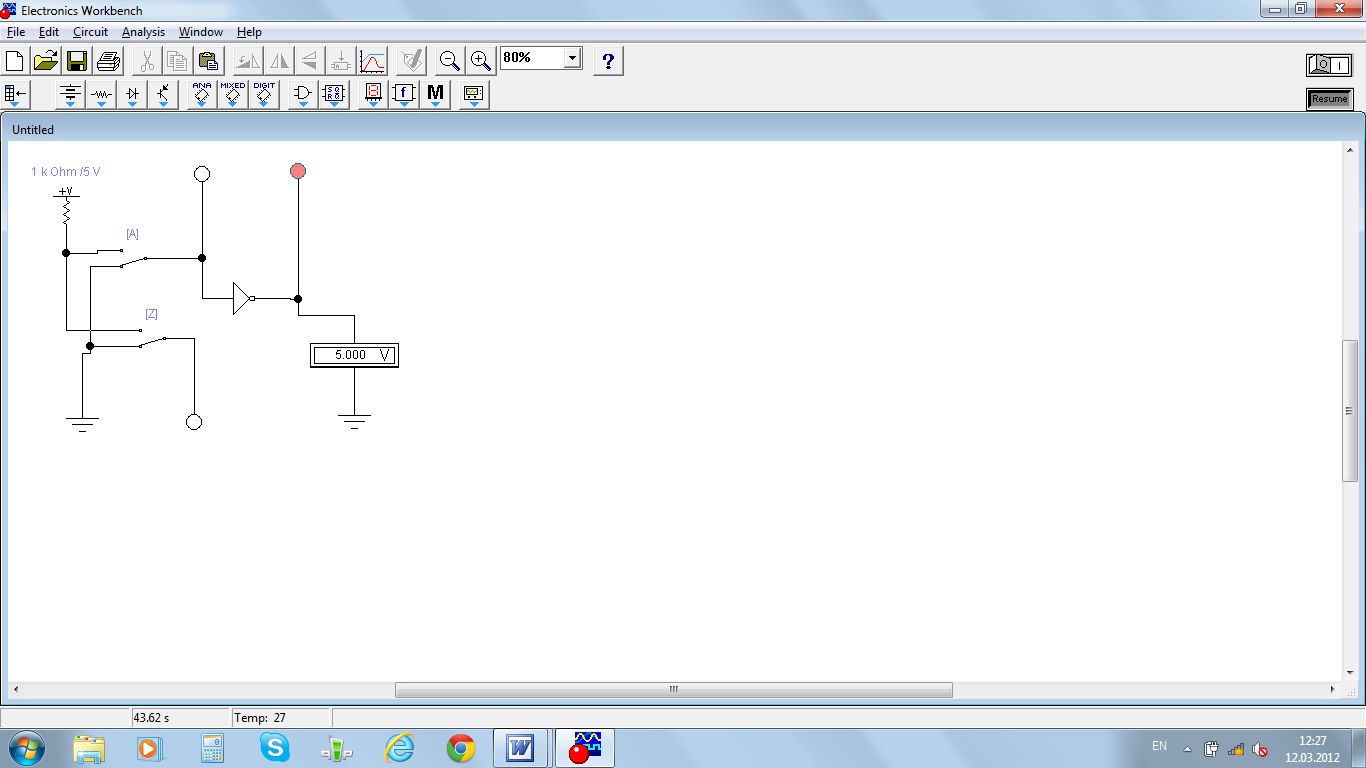

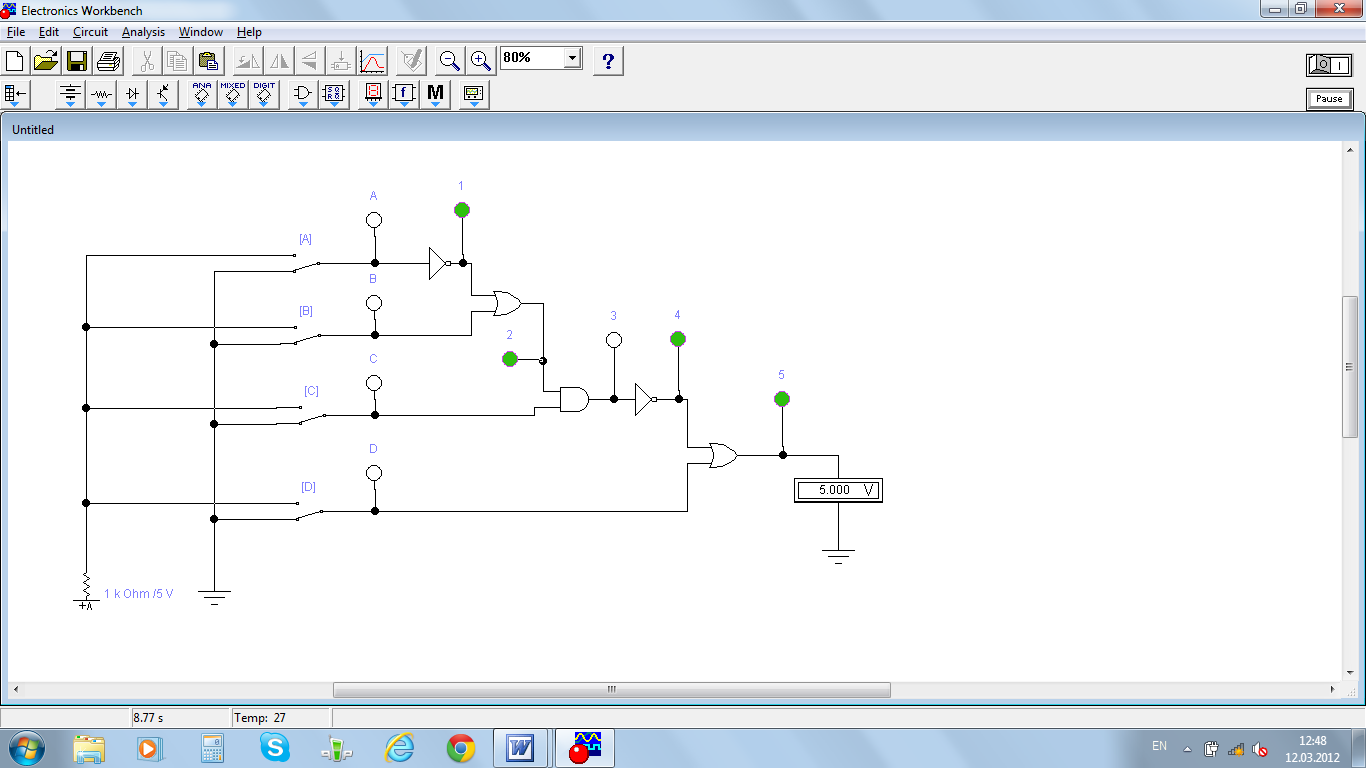

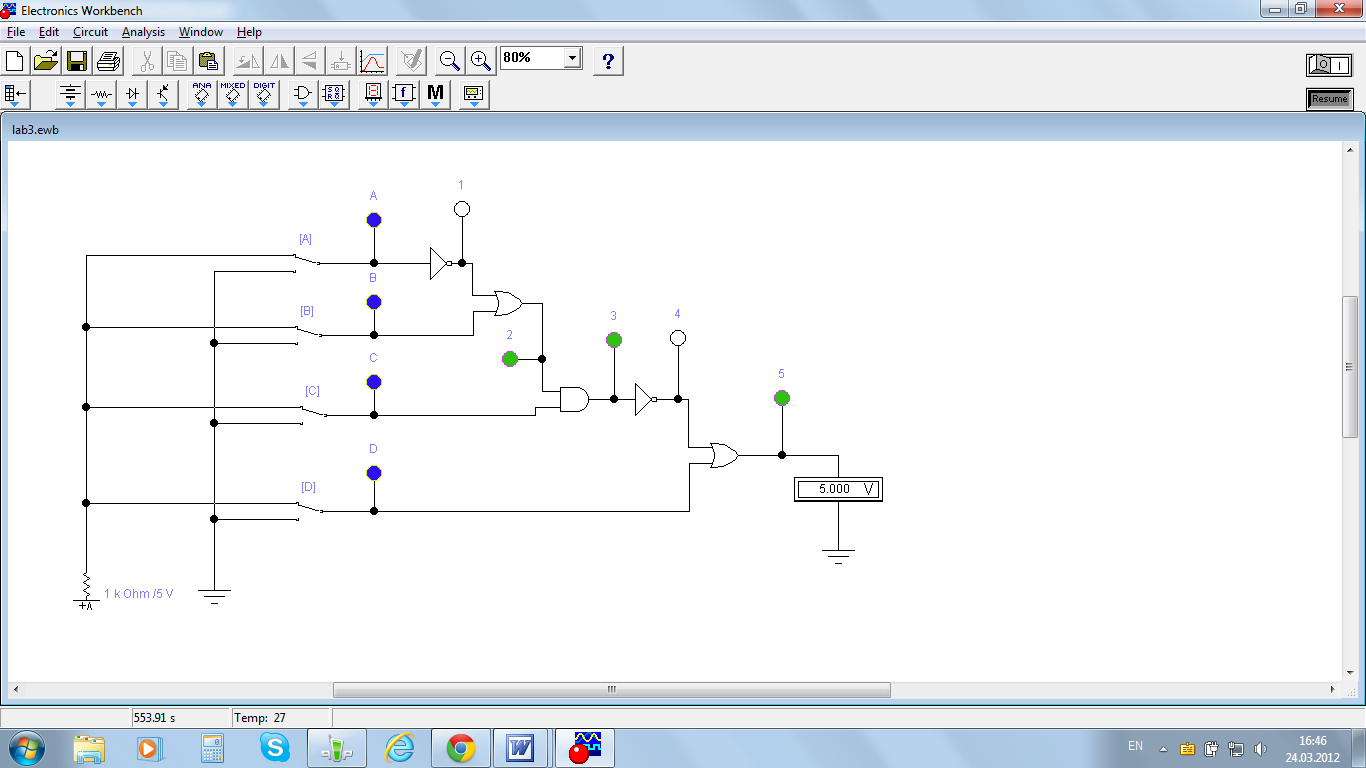

3. Исследование комбинационной схемы .

Порядок действий:

1 –

![]()

2 –

![]()

3 –

![]()

4 –

![]()

5 –

A |

B |

C |

D |

1 |

2 |

3 |

4 |

5 (Y) |

U, В |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

5 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

5 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

5 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

5 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

5 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

5 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

5 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

5 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

5 |

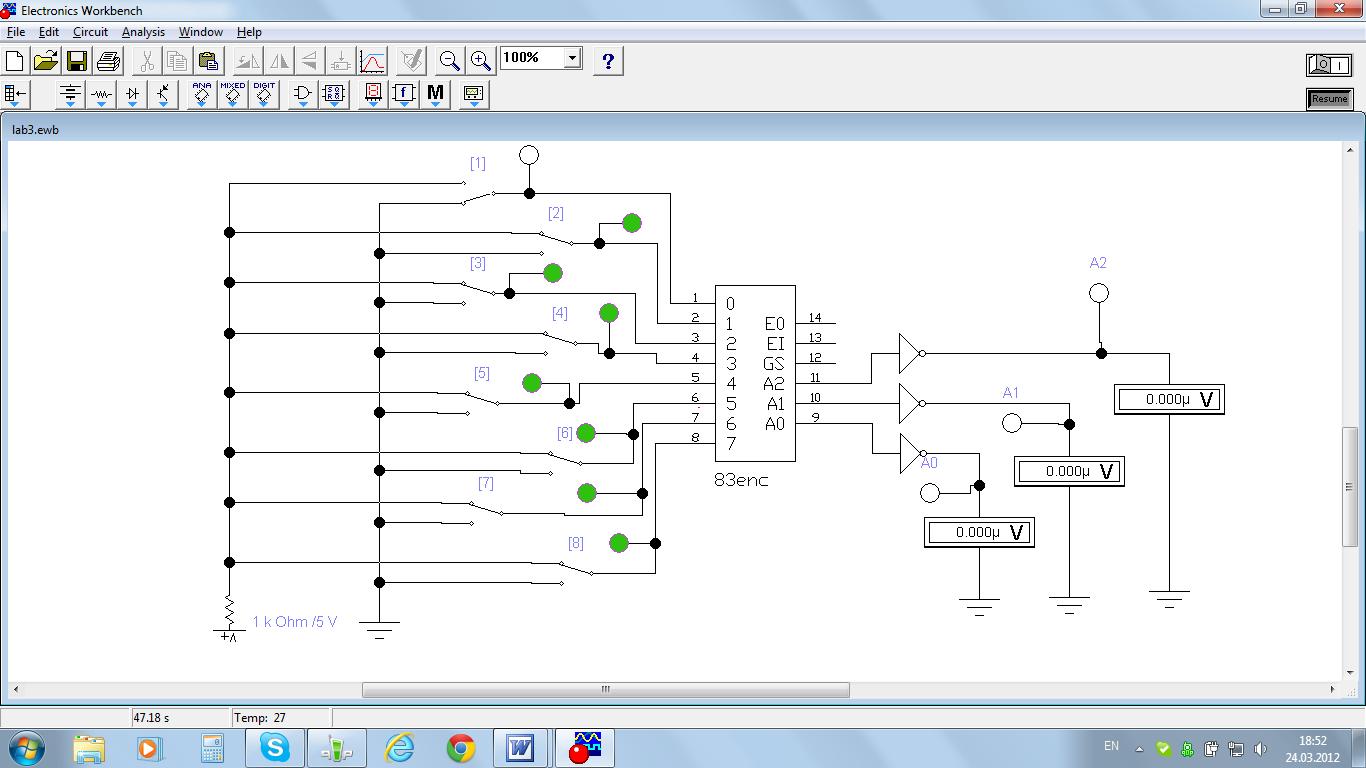

4. Исследование работы шифратора.

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

А2 |

А1 |

А0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

5. Исследование работы дешифратора.

A |

B |

C |

00 |

01 |

02 |

03 |

04 |

05 |

06 |

07 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

6. Исследование мультиплексора.

А |

В |

С |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |