- •Міністерство освіти і науки України

- •Електроніка та мікросхемотехніка конспект лекцій

- •Тема 1. Електроніка. Її одержання та застосування

- •1.1. Визначення

- •1.1.1. Фізична електроніка

- •1.1.2. Мікроелектроніка

- •1.1.3. Технологія виробництва дискретних напівпровідникових приладів і іс

- •1.2. Історичний огляд

- •1.2.1. Фізична електроніка і мікроелектроніка

- •1.2.2. Напівпровідникові і електровакуумні прилади, що передували транзистору

- •1.2.3. Історичний огляд з часу винаходу транзистора

- •Концептуальна діаграма розвітку електроніки

- •1.3. Сучасний стан електроніки

- •Моделі структур напівпровідників

- •1.4. Модель ковалентного зв'язку

- •1.4.1 Кристалічна решітка

- •Електрони і дірки

- •1.5. Модель енергетичних зон

- •Проста модель енергетичних зон

- •Тема 2. Напівпровідникові прилади

- •2.1. Принцип дії пп діодів

- •2.2. Фізичне значення параметрів діода

- •Тема 3. Випрямляючи та перетворювачі пристрої

- •Тема 4. Біполярні транзистори

- •Тема 5. Польові транзистори

- •Тема 6. ПідсилювачІ електричних сигналів

- •Тема 7. Основи мікроелектроніки і мікро схемотехніки

- •Тема 8. Аналогова мікросхемотехніка

- •Тема 9. Цифрова мікро схемотехніка Операції з|із| двійковими числами

- •Перетворення

- •Аналітично функції, які реалізуються логічними елементами, виражаються так:

- •Тема 10. Комбінаційна мікро схемотехніка

- •Шифратори і дешифратори.

- •Тема 11. Послідовна інтегральна мікро схемотехніка

- •Тема 12. Електронна схемотехніка

Шифратори і дешифратори.

Шифратором, або кодером називається комбінаційний логічний пристрій для перетворення чисел з десяткової системи числення в двійкову систему. Входам шифратора послідовно привласнюються значення десяткових чисел, тому подача активного логічного сигналу на один з входів сприймається шифратором як подача відповідного десяткового числа. Цей сигнал перетвориться на виході шифратора в двійковий код. Згідно сказаному, якщо шифратор має п виходів, число його входів повинне бути не більше ніж 2n. Шифратор, що має 2n входів і n виходів, називається повним. Якщо число входів шифратора менше за 2n, він називається неповним.

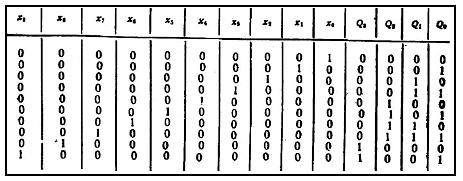

Розглянемо роботу шифратора на прикладі перетворювача десяткових чисел від 0 до 9 в двійково-десятковий код. Таблиця істинності, відповідна цьому випадку, має вигляд (табл. 10.2)

Таблиця 10.2.

Оскільки число входів даного пристрою менше за 2n = 16, маємо неповний шифратор. Використовуючи таблицю для Q3, Q2, і Q1, Q0можно записати наступні вирази:

Q3 = x8 + x9,

Q2 = x4 + x5 + x6 + x7,

Q1 = x2 + x3 + x6 + x7, (10.2)

Q0 = x1 + x3 + x5 + x7 + x9.

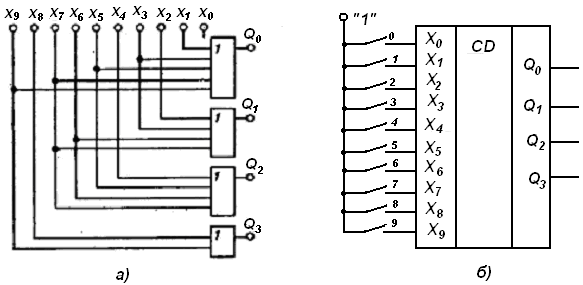

Одержана система ФАЛ характеризує роботу шифратора. Логічна схема пристрою, відповідна даній системі, приведена на рис. 10.4, а.

Неважко відмітити, що в шифраторі даного типа сигнал, що подається на вхід Хо, не використовується. Тому відсутність сигналу на будь-якому з входів Хо..Х1 трактується схемою як наявність на вході нульового сигналу.

Основне застосування шифратора в цифрових системах — це введення первинної інформації з клавіатури. При натисненні будь-якої клавіші на відповідний вхід шифратора подається сигнал логічної одиниці 1, який і перетвориться на виході в двійково-десятковий код. Варіант пристрою введення інформації показаний на рис. 10.4, б.

Мал. 10.4. Логічна схема шифратора десяткових чисел (а) і

пристрій введення інформації з клавіатури на базі шифратора (б).

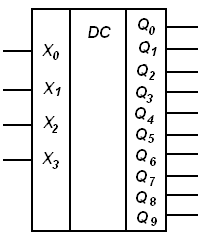

Дешифратором, або декодером називається комбінаційний логічний пристрій для перетворення чисел з двійкової системи числення в десяткову. Згідно визначенню дешифратор відноситься до класу перетворювачів кодів. Тут також розуміється, що кожному вхідному двійковому числу ставиться у відповідність сигнал, що формується на певному виході пристрою. Таким чином, дешифратор виконує операцію, зворотну шифратору. Якщо число адресних входів дешифратора п пов'язана з числом його виходів т співвідношенням m=2n, то дешифратор називають повним. Інакше, тобто якщо m<2n, дешифратор називають неповним.

Умовне зображення дешифратора показане на рис. 10.5.

Рис.10.5. Умовне зображення дешифратора.

Поведінка дешифратора описується таблицею істинності, аналогічній таблиці істинності шифратора (табл. 10.2), тільки в ній вхідні і вихідні сигнали міняються місцями. Відповідно до даної таблиці, оскільки вихідний сигнал рівний 1 тільки на одному єдиному наборі вхідних змінних, тобто для однієї конституенты одиниці, алгоритм роботи дешифратора описується рівнянням:

xi = (Q3 Q2 Q1 Q0) i (10.3)

де xі – сигнал на i-м виході дешифратора;

(Q3 Q2 Q1 Q0) i - конституента одиниці, відповідна двійковому коду i-й десяткової цифри.

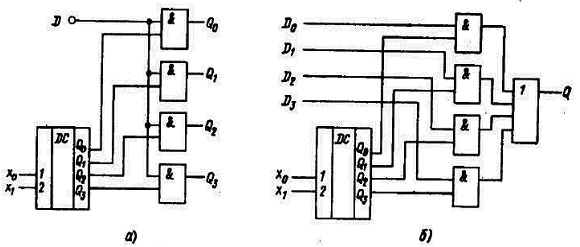

Слід відмітити, що алгоритм роботи дешифратора відрізняється від мультиплексора тільки наявністю в останній додаткового множника, відповідного значенню сигналу на інформаційному вході D. Тому при D=l демультиплексор функціонує як дешифратор. Зворотне перетворення дешифратора в демультиплексор вимагає введення допоміжних ЛЕ 2І, що виконують операцію логічного множення між загальним сигналом інформаційного входу D і відповідним логічним твором адресних сигналів (Q3 Q2 Q1 O0). Схема побудованого таким чином демультиплексора приведена на рис. 10.6, а.

Використовуючи дешифратор, можна побудувати і схему мультиплексора. Для цього схему рис. 10.6, а необхідно доповнити вихідним ЛЕ 4АБО (рис. 10.6, б).

Мал. 10.6. Реалізація демультиплексора (а) і мультиплексора (б) з використанням дешифратора.

При розробці ІС знайшло застосування декілька логічних структур дешифратора. Їх основна відмінність полягає в швидкодії і числі використовуваних елементарних ЛЕ.

Найбільш швидкодіючим і в той же час найскладнішим є дешифратор, що безпосередньо реалізовує систему ФАЛ (10.3). Такий дешифратор називається одноступінчатим або паралельним.