- •Организация и функционирование вычислительных машин

- •Раздел 1. Основные понятия архитектуры и организации эвм. 3

- •Раздел 2. Организация процессора и основной памяти вм 7

- •Раздел 3. Организация памяти в эвм 36

- •Раздел 4. Организация системы ввода-вывода в эвм. 52

- •Раздел1.Основныепонятия архитектуры и организации эвм. Состав электронной вычислительной машины (эвм)

- •Принцип программного управления и машина фон Неймана

- •Понятие архитектуры, организации и реализации эвм

- •Многоуровневая организация эвм.

- •Понятие семантического разрыва между уровнями

- •Организация аппаратных средств эвм

- •Типовая структура вм на микропроцессорных наборах

- •Раздел 2. Организация процессора и основной памяти вм

- •Типовая структура процессора и основной памяти

- •Основной цикл работы процессора

- •Организация процессора и памяти в микропроцессоре Intel 8086

- •Организация стека процессора

- •Распределение оперативной памяти в i8086, ms dos

- •Организация выполняемых программ в ms dos

- •Режимы адресации памяти в микропроцессоре Intel 8086

- •1. Регистровая адресация

- •2. Непосредственная адресация

- •3. Прямая адресация

- •4. Косвенная адресация

- •5. Адресация по базе

- •6. Косвенная адресация с масштабированием

- •7. Адресация по базе с индексированием и масштабированием

- •Система команд i8086

- •3DNow! от amd

- •Организация прерываний в процессоре Intel 80x86

- •Управление выполнением команд в эвм.

- •Способы формирования управляющих сигналов.

- •Простейшая схема формирователя управляющих сигналов

- •Способы кодирования микрокоманд.

- •Компьютеры с сокращенным набором команд.

- •Арифметические особенности risc процессоров.

- •Раздел 3. Организация памяти в эвм

- •Основные среды хранения информации.

- •Виды запоминающих устройств.

- •Память с произвольной выборкой.

- •Постоянные запоминающие устройства.

- •Ассоциативные запоминающие устройства (азу)

- •Иерархическая система памяти

- •Организация памяти типа кэш.

- •Организация структуры основной памяти в процессорах ix86.

- •Организация виртуальной памяти.

- •Организация виртуальной памяти на i386 и более старших моделях.

- •Организация работы с внешней памятью.

- •Организация работы с файлами на дисках в ms-dos.

- •Раздел 4. Организация системы ввода-вывода в эвм.

- •Архитектура систем ввода-вывода.

- •Способы выполнения операции передачи данных

- •Структуры контроллеров внешних устройств, для управления различными режимами передачи данных.

- •Программные средства управления вводом-выводом.

- •Основные компоненты процедуры управления ввода-вывода общего вида

- •Состав и реализация устанавливаемого драйвера символьного типа

- •Литература

- •Краткое введение в язык ассемблера.

- •1. Директивы задания данных

- •2. Директивы сегментации программы

- •3. Директивы группирования.

- •4. Порядок размещения сегментов.

- •5. Директивы ограничения используемых команд.

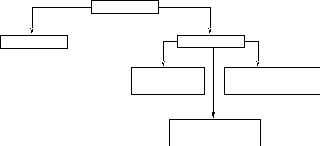

Способы выполнения операции передачи данных

передача данных

синхронная асинхронная

несовмещенный вв/выв по программному

вв/выв прерыванию

вв/выв по аппаратному

прерыванию

Синхронная передача.

-

↓

← Команда вв/выв

Передача 1

↓

← Команда вв/выв

Переача 2

↓

Это самый быстрый способ передачи данных, но ненадежный.

Асинхронная передача.

Несовмещенный ввод-вывод.

В данном случае центральный процессор после инициализации ввода-вывода с помощью команды, ожидает готовности внешнего устройства (говорят что процессор весит на флажке готовности). Этот бит представляет собой своеобразный семафор который управляет доступом данных, либо процессора, либо внешнего устройства. Это решение комфортно для внешнего устройства и неэффективно для процессора. Так как внешние устройство диктует условия, со стороны внешнего устройства это высокая скорость передачи данных. Иногда удается в цикле ожидания вставлять программу.

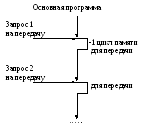

Ввод-вывод по программному прерыванию.

В данном случае некоторое внешнее устройство для осуществления передачи устанавливает запрос прерывания работы процессора и если прерывание, возможно, то выполняется передача, после повторения происходит возврат на основную работу программы.

Удобен для процессора и неэффективен для внешнего устройства, в таком режиме к процессору подключаются много медленных устройств с произвольными моментами к готовности передачи данных. Процессор является хозяином положения.

Ввод-вывод по аппаратному прерыванию (прямой доступ к памяти).

Процесс передачи осуществляется без участия центрального процессора.

У процессора занимается один цикл памяти необходимый для передачи.

В таком режиме выполняется обычно передача блоков данных, для уменьшения накладных расходов, вязаных с инициализацией канала перед операцией ввода-вывода.

Этот режим обеспечивает параллельную работу процессора и операции ввода-вывода, он быстрый, так как передача идет на уровне памяти.

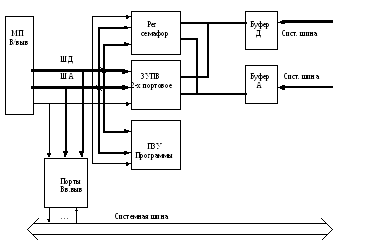

Структуры контроллеров внешних устройств, для управления различными режимами передачи данных.

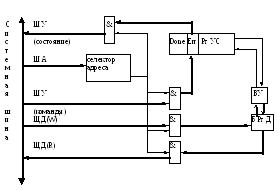

1 .

Контроллер не совмещенного ввода-вывода.

.

Контроллер не совмещенного ввода-вывода.

Основы узла:

Селектор Адреса, который выдает на выходе единицу (разрешающий сигнал), только для одного адреса (своего адреса)

Регистр Управления и Состояния – который связывается с системой управления по входу и выходу и принимает от шины управления команду, на выходе выдает состояние внешних устройств при выполнение команды.

Буферный Регистр Данных – для согласования скоростей (буфер)

Используется в двух режимах

Записи

По чтению

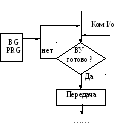

2. Контроль передачи по программному прерыванию.

Контроль состоит из двух частей:

Индивидуальный контроллер внешнего устройства.

(аналогично контроллеру не совмещенного ввода-вывода)

Общий или выделенный контроллер прерывания.

КНВВ линий связи с памятью и процессором те же, что и раньше.

От РгУС КНВВ берется признак разрешения прерываний EIи признак готовности (Done), может быть задан приоритет.

IRR– регистр приема запросов

ISR– регистр обслуживания запросов

IMR– маска прерывания

PRIOR– арбитр, схема разрешения приоритетов.

ШД – для ввода IM(маски)

Int– Выдача прерываний в процессор

Inta– Разрешение на прерывание

НВП – Номер Вектора Прерывания

Если прерывание (IRQ)INTA= ‘разрешено', то тогда команда выставляется НВП.

Далее идет передача данных по КНВВ с той лишь разницей, что процессор не висит на флаге ожидания. И так до следующего пакета данных.

Удобно для процессора.

Неудобно для устройств, так как устройство должно ожидает, пока контроллер получит разрешение.

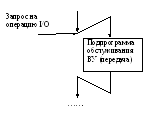

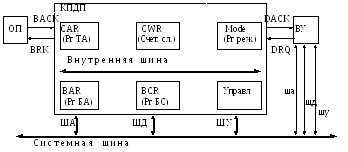

3. Передача данных в режиме аппаратного прерывания (или прямого доступа к памяти).

Основные компоненты.

CAR- Регистр текущего адреса (работает в режиме автоинкрементирования) увеличивается на

1 (байт) или 2 (слово).

CWR– счетчик слов (или байт), который работает в режиме автодекрементирования после передачи содержимое регистра уменьшается на 1(байт) или 2 (слово).

ModeR- регистр передачи(определяет характер и направление передачи).

BAR- регистр базового адреса, содержимое в процессе передачи не изменяется (служит для защиты).

BCR- регистр базового счетчика, содержит первоначальное количество слов для передачи (служит для контроля информации).

Управление – внутреннее управление передается внутри шины.

ШУ – Memrчтение памяти

Iorчтение устройства

Memwзапись памяти

Iowзапись устройства

ВУ – В режиме прямого доступа к памяти устанавливает взаимную передачу данных между памятью и внешним устройствам (HDD,Soundcardи т. д.).

Управление передачей происходит без участия процессора (Процессор должен только подготовить и инициализировать регистры контроллера.).

В обеспечении передачи задействованы все три вида контроллеров:

Контроллер памяти.

Контроллер прерываний, в к ПДП – формируется сигнал в процессоре о завершение передачи в прямом доступе.

Обычный контроллер КНВВ содержащийся во внешнем устройстве..

После подготовки устройством данного оно выставляет запрос на (DRQ) передачу в режиме прямого доступа.

В ответ контроллер прямого доступа выставляет запрос на возможность захвата шины.

Вырабатывается подтверждающий сигнал Back.

Вырабатывается подтверждающий сигнал (DACK) у контроллера к внешнему устройству.

Далее либо MemrлибоMemw

IOW IOR

после чего сбрасывается сигнал запроса шины и разрешается доступ к памяти.

BRQ 0,DACK 0

TA ++ либоCC --

Пункты с 1 по 7 называются “занятие цикла памяти”, и выполняются для передачи одного данного.

В i8086 в качестве КПДП выступала микросхема.

8237A–XT(содержит четыре канала с номерами 0 - 3, работает с одно байтовыми портами)

8237A– 5 -ATи выше (содержит две группы по четыре канала, первая как уXT(для поддержки), а вторая с шестнадцати битными портами).

Состав регистров и адресация 8237A.

00h– 07hномера регистров по каждому из каналов.

0Ahрегистр маски разрешает и запрещает работу по каждому из каналов.

номера битов:

0, 1 – номер канала

2 – разрешить, запретить

3…7 – не используются

0Bh– регистр режима

номера битов:

0, 1 – номер канала

2, 3 – тип цикл DMA

00 – цикл проверки

01 – цикл занятости

10 – цикл чтения

11 – запрещенная комбинация

4 – режим инициализации

5 – направление приращения адреса

0 – увеличение

1 – уменьшение

6, 7 – режим обслуживания

00 – по требованию

01 – одиночная передача

10 – блочная передача

11 – каскодирование (использование двух уровневых контроллеров)

0Ch– сброс триггеров байта

0Eh– сброс регистра маски

81h…8Fh– регистры страниц, текущий адрес равен 16 бит, шина адреса и шина данных (прямого доступа к памяти) равны 20 бит, регистры страниц задают адрес страницы (старшие четыре бита адреса – работают с 1Мб.), одна страница – 64 Кб. . При прямом доступе к памяти переходит границы страницы.

Для 8237A-5-ATиспользуются байтовые регистры станицы (24 бита) и появляется возможность адресовать до 16Мб оперативной памяти.

Расширенные возможности использования

специализированного процессора ввода-вывода.