- •Основные понятия архитектуры и организации эвм.

- •1. Регистровая адресация

- •2. Непосредственная адресация

- •3. Прямая адресация

- •4. Косвенная адресация

- •5. Адресация по базе

- •6. Косвенная адресация с масштабированием

- •7. Адресация по базе с индексированием и масштабированием

- •4. Сдвиговые команды.

- •5. Команды передачи управления.

- •1. Директивы задания данных

- •2. Директивы сегментации программы

- •3. Директивы группирования.

- •4. Порядок размещения сегментов.

- •5. Директивы ограничения используемых команд.

- •3DNow! от amd

- •Первый способ

- •Второй способ

Организация ЭВМ

Основные понятия архитектуры и организации эвм.

Состав ЭВМ

ЭВМ- это совокупность аппаратных и программных средств, предназначенных для обработки информации. ЭВМ- универсальный набор фиксированных аппаратных и программных средств, содержащих один основной процессор и, возможно, несколько сопроцессоров. Вычислительные системы относятся к системам, содержащим несколько процессоров (мультипроцессорность), и являются проблемно-ориентированными.

ЭВМ Аппаратные

средства Программные

средства (ПС) Процессор Набор

устройств, образующих память

Устройство связи с внешней средой

(все, что подключается к процессору

и памяти)

Шины и протоколы связи между устройствами

Операцион-ные

системы Проблемно

ориентирован-ные ПС Инструмен-тальные

ПС Системы

промежу-точного ПО

Утилиты

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Операционные системы- являются основными средствами выполнения программ. Инструментальные ПС включают все средства, необходимые для разработки программ: редакторы, компиляторы и др. Утилиты- сервисные средства, облегчающие взаимодействия пользователя и ЭВМ: архиваторы, и др. ПОПС: программные средства, предназначенные для определенной области применения: MatCAD, AutoCAD и др. СППО: программные средства, которые позволяют реализовать технологию разработки программных средств:DCOM, CORBA и др.

Обычно разделяют следующие классы ЭВМ.

Микро ЭВМ - ЭВМ со встроенными микропроцессорами (Embedded Computers, ПК и др. )

Рабочие станции (Sun Work Station)

Машины среднего класса - вычислительные системы из нескольких процессоров (HP9000, Series800, SGI- это машины, которые могут управлять несколькими машинами)

Большие машины - на уровне крупных компьютеров (Cray, CDC6600)

Супер ЭВМ - системы с параллельной архитектурой матричного типа (Iliac IV, VP-2000, Эльбрус)

Принцип программного управления и машина Фон Неймана

Концепция хранимой программы впервые была предложена Фон Нейманом.

Основные принципы хранимой программы.

команды, так же как и данные, хранятся в памяти машины, в команде указываются не сами данные, а их адреса в памяти;

команды могут обрабатывать также как и числовые данные (модификация команд), но эта тактика не применима, т.к. снижает надежность;

хранимая программа позволяет осуществлять произвольный переход от одной команды к другой.

Основные особенности первых машин (Фон Нейманского типа), построенных по изложенному принципу.

Наличие единого вычислительного устройства, включающего один процессор, память и некоторые внешние устройства;

использование линейной структуры адресации памяти со словами фиксированной длины;

централизованный принцип управления выполнения программы по последовательному алгоритму;

низкий уровень машинных команд, выполняющих элементарные операции.

Для таких машин «узким» местом является память и канал связи. Как данные, так и команды должны последовательно выбираться из памяти.

Модификации (отклонения от Фон Нейманского типа машин).

увеличена разрядность обработки данных (16 бит32 и 64 бит), повышена производительность;

активное использование конвейеризации и выборки при обработке команд;

активное использование кэш-памяти (Cash- скрытый), т.е. блоков памяти, которые являются буферами между процессором и оперативной памятью. Эта память является скрытой, т.к. пользователь не замечает обращение к ней.

Понятие архитектуры, организации и реализация

Архитектура- это множество ресурсов ЭВМ, доступных пользователю на логическом уровне, без детализации состава и характеристики процессоров, устройств памяти, внешних устройств и программного обеспечения.

Организация- это способы установления связи и взаимодействий процессора, памяти и внешних устройств, используемые для реализации возможностей, заложенных в архитектуре.

Организация:

представление и формат данных;

виды организации памяти;

состав и формат машинных команд;

состав и система прерываний;

обмен данными.

Реализация- техническое исполнение конкретных устройств, линий или шин связи и протоколов взаимодействия между ними.

Обычно на уровнях организации и реализации происходит перераспределение функций между аппаратными и программными средствами. Это порождает семейство машин одной архитектуры, но разной производительности.

Многоуровневая организация ЭВМ. Понятие семантического разрыва между уровнями

В общем случае обработку информации на ЭВМ можно рассматривать в виде иерархической системы уровней

|

СПЕЦИАЛЬНОСТЬ |

УРОВНИ |

ПРИМЕЧАНИЯ |

|

пользователь; поставляет задачи |

Концептуальный |

пользователь задает режимы и виды обработки задачи, необходимые для решения |

|

пользователь функционального ПО, решающий задачи из конкретной предметной области |

Уровень ПОС |

уровень приложений |

|

разработчик функциональных программных комплексов |

Уровень промежуточного ПО |

middleware |

|

разработчик функциональных программ |

Уровень языков высокого уровня |

ЯВУ |

|

системный программист |

Уровень ассемблера |

|

|

системный программист прикладной программист |

Уровень ОС |

обеспечение выполнения привилегированных команд, запрещенных в ассемблере |

|

область работы |

Уровень машинных команд |

цифровое кодирование и представление команд |

|

электронщик |

Уровень микрокоманд |

Описание набора элементарных операций, реализующих машинные команды |

|

электронщик |

Уровень межрегистровых передач |

реализация конкретных операций на уровне связи устройств |

|

электронщик |

Уровень вентилей |

технологический уровень, отдельное устройство машины представляется как интегральная схема |

Ассемблер- простейший язык, который не требует жесткого задания распределения памяти, близок к машинному языку. Элементарные операции- операции, выполнимые за один такт машины (т.е. микрооперации).

Каждый верхний уровень интерпретируется одним или несколькими нижними уровнями. Каждый из них можно проектировать независимо. Чем ниже уровень, на котором реализуется программа, тем более высокая производительность достижима. Допускается модификация нижних уровней, и это не влияет на более верхние.

Понятие семантического разрыва между уровнями.

Преобразование операторов языков высокого уровня в машинный код или микропрограммный уровень заставляет транслятор, во-первых, уметь распознавать операторы и команды различных уровней и, во-вторых, для любого оператора языка высокого уровня генерировать десятки или сотни команд низкого уровня. Это приводит к усложнению транслятора, увеличения трудоемкости его разработки, снижению производительности генерируемых программ. Наличие этих проблем называют семантическим разрывом между уровнями. Основным способом его преодоления является специализация машин, при которой операторы проблемно-ориентированных языков могут непосредственно выполняться аппаратными средствами машины и не требовать трансляции.

Пример: аппаратная организация графических преобразований; операции с векторами и матрицами.

Организация аппаратных средств ЭВМ.

В зависимости от способов связи устройств ЭВМ различают следующие типы организации.

ЭВМ с непосредственными связями

ВУ

ЦП ОП

ВУ

Каждое устройство может связываться с любым другим. Этот способ применялся в двух первых поколениях машин, т.к. с возрастанием числа устройств, становится очень сложно реализовать такую организацию.

ЭВМ

с канальной организацией

ВУ

ВУ

ВУ

ВУ

Контроллер

Канал

1 (Мульт.)

Канал

1 (Мульт.)

Ц

П

ОП Канал 2 (Сел.)

Контроллер ВУ

П

ОП Канал 2 (Сел.)

Контроллер ВУ

Канал

3 (Мульт.)

Канал

3 (Мульт.)

Контроллер Контроллер

ВУ

ВУ

ВУ

ВУ

ВУ

ВУ

ВУ

ВУ

Центральным элементом машины является память, которая хранит программы центрального процессора и каждого из каналов, являющимися процессорами ввода вывода, работающих параллельно со своим процессором по своей программе.

Каналы: селекторный- управляет только одним устройством и применяются для подключения быстрых устройств; мультиплексный- управляет несколькими более медленными внешними устройствами.

При данной организации все еще очень большое количество связей. Большая специализация процессоров различного типа затрудняет их интегральное исполнение. Такая организация применялась в машинах третьего и частично четвертого поколений.

Шинная

организация

ВУ

ВУ

ВУ

ВУ

Контроллер 1 Контроллер N

Шина

памяти

Шина

памяти

П

амять

ЦП

амять

ЦП

Шина

ввода / вывода

Шина

ввода / вывода

Шина

прямого доступа к памяти

Шина

прямого доступа к памяти

Контр.

пр. сост. к п. ВУ

Контр.

пр. сост. к п. ВУ

ВУ

ВУ

Используются различные адресные пространства для обращения к памяти и устройствам ввода вывода. Это требует выделенных команд ввода вывода в системе команд процессора.

ADD AX, 100 ; 100- адрес ячейки памяти

IN AX, 100 ; 100- номер устройства

Организация на общей шине (Unibus)

А

Р

Б Общая шина

Ц

П

И

П

И

Т

Р

Р

Память К1 МУЛ

ВУ1 К1 К2 К3

ВУ ВУ ВУ

Единое адресное пространство ячеек памяти и внешних устройств, следовательно все команды процессора обработки данных могут быть применены к внешним устройствам. Общая шина является «узким» местом и снижает производительность и надежность. Данная реализация в чистом виде почти не используется.

Современные процессоры на микропроцессорных наборах.

Запр.

ПДП (IRQ)

Запр.

ПДП (IRQ)

ЦП

У

ЦП

У

( CPU)

А

CPU)

А

ППД ПЗУ АДП1 ВУ1 АДПN ВУN Контроллер ПДП

(RAM) (ROM) (AD1) (IOU1) (ADN) (IOUN) (DMAN)

Д

Д

Таймер

Таймер

(TMR)

INT RQ Контроллер

прерываний

(INTU)

(INTU)

Reset Нач. сброс

(RSG)

ГТ

(CLG)

АДП- адаптер (контроллер для подключения одного устройства).

У- шина управления.

А- шина адресов.

Д- шина данных.

Запрос ПДП приостанавливает работу центрального процессора на 1 такт для прямого доступа.

Сопроцессоры:

NPS-математический сопроцессор;

APS-аналоговый процессор;

DSP-процессор цифровой обработки сигналов (digital signal processor)

Организация процессора в современных ЭВМ

(контроллерное управление)

Речь о машинах с контроллерным управлением, в которых порядок выполнения команд явно задается программой. Так же существуют машины с потоковым управлением и машины с запросным управлением (редукционные).

Процессор выполняет две функции:

обработка данных в соответствии с заданной программой;

управление всеми устройствами машины.

Управление в соответствии с заданной программой представляется в виде последовательности команд в цифровой форме. Каждая из команд имеет части:

-

операционная часть

адресная часть

Операционная часть - задает код операции и режим ее выполнения. Адресная часть - может содержать непосредственно данные, адреса данных или сведения для определения адреса данных. Формирование исполнительного адреса - период от сведений об адресе к самому адресу. В адресной части могут быть от ни одного до трех операндов.

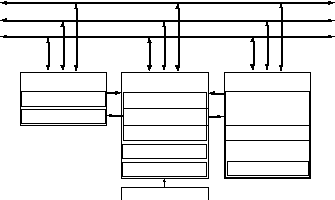

Типовая структура процессора с оперативной памятью

А

Д

У

Операционная часть Управляющая часть Память

АЛУ Внутренние регистры РАП

РОНы Рг. СС РДП

Рг. ком. Накопит.

Декодер Контр. пам.

Форм. ус. Рг. УС

ГТ

АЛУ - арифметико-логическое устройство.

РОНы - регистры общего назначения (от 8 до нескольких сотен штук).

Рг. СС - регистр слова состояния. Содержит текущее состояние процессора, в который входит уровень приоритета текущей программы, флажки завершения последней команды, режим обработки текущей команды.

Режимы обработки:

User Mode- режим пользователя. В этом режиме не могут выполнятся системные команды (команды изменения состояния процессора и команды ввода вывода);

Super Visor Mode- режим супервизора. Обеспечивается выполнение всех команд ввода вывода;

Kernel Mode-возможность выполнения всех команд.

ПС - программный счетчик. Содержит адрес текущей команды и автоматически наращивается для подготовки адреса следующей команды (исключение составляет команда перехода).

Рг. ком. - регистр команд. Содержит код исполняемой в данный момент команды.

РДП - регистр данных памяти.

Накопитель - хранит нужные элементы информации.

Основной цикл работы процессора

Этапы:

Выборка команды.

Формирование исполнительных адресов операндов, если требуется.

Выборка операндов из памяти.

Исполнение операции.

Запоминание результата.

Опрос программного прерывания.

Каждый этап выполняется за один цикл памяти.

При обработки этих этапов используется конвейерный способ (при выполнении очередного этапа одновременно происходит выполнение предыдущего следующей команды). Разумеется если одна команда изменяет содержимое какой-либо ячейки памяти, а следующая использует ее новое значение, то последняя не может начать исполняться, пока результат не будет сохранен).

-

IF

AM

OF

IF

ST

IRQ

IF

AM

OF

IF

ST

IRQ

IF

AM

OF

IF

ST

IRQ

Два вида прерываний:

программное, прерывание которое выполняется по команде программы и обрабатывается путем выполнения специальным обработчиком прерываний.

аппаратное, реализуется без участия программы процессора с помощью аппаратных средств, имеет высокий приоритет и может поступать в любой момент времени, прерывая выполнение текущей команды.

Подробнее о прерываниях будет рассказано позже.

Организация процессора и памяти вида Intel 8086

В данном процессоре длина слова составляет 16 бит, что равно 2 байтам. Минимально адресуемой и обрабатываемой единицей является байт, при этом адрес слова совпадает с адресом младшего байта и является четным. Максимальная емкость памяти 211=64 Кб. Сегментирование используется для расширения адресного пространства, максимальная длина каждого сегмента равна 64Кб. Адрес образуется парой сегмент и смещение

Segment:Offset

Смещение сдвигается на 4 бита влево и суммируется с сегментом, результатом является физический адрес.

Программно доступные регистры процессора

Начиная с 80386, процессоры Intelпредоставляют 16 основных регистров для пользовательских программ плюс еще 11 регистров для работы с числами с плавающей запятой (FPU/NPX)и мультимедийными приложениями (ММХ). Все команды так или иначе изменяют значения регистров, и всегда быстрее и удобнее обращаться с регистру, чем к памяти.

Регистры общего назначения

16-битные регистры АХ (аккумулятор), ВХ (база), СХ (счетчик), DX (регистр данных) могут использоваться без ограничений для любых целей - временного хранения данных, аргументов или результатов различных операций. На самом деле, начиная с процессора 80386, все эти регистры имеют размер 32 бита и называются они ЕАХ,EВХ,EСХ, EDX. Кроме этого, отдельные байты в 16-битных регистрах АХ - DX тоже имеют свои имена и могут использоваться как 8-битные регистры. Старшие байты этих регистров называются АН, ВН, СН, DH, а младшие - AL, DL, CL, DL.

Другие четыре регистра общего назначения - SI (индекс источника), DI (индекс приемника), BP (указатель базы), SP (указатель стека) - имеют более конкретное назначение и могут применяться для хранения всевозможных временных переменных, только когда они не используются по назначению. Регистры SIи DIиспользуются в строковых операциях, ВР и SPиспользуются при работе со стеком. Так же как и с регистрами АХ - DX,начиная с процессора 80386, эти четыре регистра являются 32 битными и называются ESI, EDI,EВР и ESPсоответственно.

Сегментные регистры

При использовании памяти для формирования любого адреса применяются два числа - адрес начала сегмента и смещение искомого байта относительно этого начала. В процессорах Intelпредусмотрены следующие сегментные регистры – CS (сегмент кода), DS (сегмент данных), ES (дополнительный сегмент), SS(сегмент стека). Начиная с 80286 появились регистры FSи GS.

Смещение следующей выполняемой команды всегда хранится в специальном регистре- IP (указатель инструкции),запись в который приведет к тому, что следующей будет исполнена какая-нибудь другая команда. На самом деле все команды передачи управления -перехода, условного перехода, цикла, вызова подпрограммы и т. п. осуществляют запись в CSи EIP.

Регистр флагов.

|

|

|

|

|

OF |

DF |

IF |

TF |

SF |

ZF |

0 |

AF |

0 |

PF |

1 |

CF |

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

CF-флаг переноса (CARRY);

PF- флаг четности (PARITY);

AF-дополнительный флаг переноса (AUXILARG);

ZF-флаг нуля (ZERRO);

SF-знаковый флаг (SIGN);

TF-флаг слежения, ловушка;

IF-флаг прерываний (INTERRAPTION);

DF-флаг направления (DIRECTION);

OF-флаг переполнения (OVERFLOW).

Организация стека процессора.

Стек может работать только со словами, заполнение стеков происходит в сторону уменьшения адресов.

По существу команды PUSH AX и POP AXвыполняются в два приема:

PUSH AX

(SP)-2SP

(AX)[SP]

POP AX

[SP]AX

(SP)+2SP

Использование:

промежуточное хранение содержимого регистра;

обмен содержимого регистров;

сохранение адресов возврата при вызове подпрограмм;

передача параметров между вызываемой и вызывающей программами;

для обработки прерываний и сохранение векторов прерываний.

Распределение оперативной памяти в i8086, MS DOS.

|

ГРАНИЦЫ УЧАЧСТКА (Кб) |

СЕГМЕНТ:СМЕЩЕНИЕ |

НАЗНАЧЕНИЕ УЧАСТКА |

|

0..1 |

0000:0000(03FF) |

256 векторов прерываний. |

|

1..60 |

0010:0000 |

область данных и резидентная часть DOS IBMBIO.COM – расширительBIOS:

IBMDOS.COM –обработчик прерываний операционной системы:

резидентная часть COMMAND.COM:

|

|

60..640 |

|

данные, программы пользователя. |

|

640..768 |

A000:0000 |

область видеоадаптеров. |

|

768..1016 |

C000:0000 FE00:0000 |

область ПЗУ; область BIOS. |

Организация выполняемых программ в MS DOS.

Существует три типа исполняемых файлов:

*.bat- задают порядок выполнения некоторой последовательности программ;

*.com- файлы исполняемых программ типаcom;

*.exe- файлы исполняемых программ типаexe.

*.com- для организации простых модулей (tiny, small, т.е. не более 64кб);comфайл формируется в загрузочном виде и не требует настройки.

*.exe- эти файлы могут иметь произвольную длину, они содержат таблицу загрузки и при их загрузке должна выполняться настройка файла для размещения его в памяти.

COM файл

|

64кб |

Данные программы |

SS:SP |

|

|

| |

|

|

100р CS:IP | |

|

|

PSP |

|

|

|

| |

|

0 |

DS, CS, ES, SS |

PSP (Program segment Prefix)- префикс сегмента программы, он содержит информацию для доступа программы к параметрам командной строки, к среде окружения, для реакции программы на критические ошибки и некоторые команды типаCtrl+C.В начальной частиPSP указан адрес обработчика прерываний для возврата вDOS. Так какCSPSPи программа не может исполняться, начиная с этого адреса, первой командой делаютORG 100 (100hIP).22

EXE файл

SS:SP

SS:SP

Стек

SS:00

Данные

DS

(сюда его

необходимо установить)

DS

(сюда его

необходимо установить)

Код

100h

CS

PSP

DS

Структура PSP.

|

0h |

DW |

CD 20вызов прерыванияDOS INT 20для завершения программы |

|

2h |

DW |

размер доступной для программы памяти в параграфах |

|

2Ch |

DW |

значение сегментного адреса среды окружения |

|

80h |

|

DTA–буферная область данных, адрес начала командной строки программы |

Режимы адресации.

Большинство команд процессора вызываются с аргументами, которые в ассемблере принято называть операндами.Операнды в программе могут задаваться в

регистрах общего назначения;

непосредственно в коде команды;

ячейках памяти, задаваемых в команде прямо или косвенно;

портах ввода вывода.

Для указания месторасположения операнда используются 7 режимов адресации.