- •Организация и функционирование вычислительных машин

- •Раздел 1. Основные понятия архитектуры и организации эвм. 3

- •Раздел 2. Организация процессора и основной памяти вм 7

- •Раздел 3. Организация памяти в эвм 35

- •Раздел 4. Организация системы ввода-вывода в эвм. 51

- •Раздел1.Основныепонятия архитектуры и организации эвм. Состав электронной вычислительной машины (эвм)

- •Принцип программного управления и машина фон Неймана

- •Понятие архитектуры, организации и реализации эвм

- •Многоуровневая организация эвм.

- •Понятие семантического разрыва между уровнями

- •Организация аппаратных средств эвм

- •Типовая структура вм на микропроцессорных наборах

- •Раздел 2. Организация процессора и основной памяти вм

- •Типовая структура процессора и основной памяти

- •Основной цикл работы процессора

- •Организация процессора и памяти в микропроцессоре Intel 8086

- •Организация стека процессора

- •Распределение оперативной памяти в i8086, ms dos

- •Организация выполняемых программ в ms dos

- •Режимы адресации памяти в микропроцессоре Intel 8086

- •5. Адресация по базе

- •6. Косвенная адресация с масштабированием

- •7. Адресация по базе с индексированием и масштабированием

- •Система команд i8086

- •3DNow! от amd

- •Организация прерываний в процессоре Intel 80x86

- •Управление выполнением команд в эвм.

- •Способы формирования управляющих сигналов.

- •Простейшая схема формирователя управляющих сигналов

- •Способы кодирования микрокоманд.

- •Компьютеры с сокращенным набором команд.

- •Арифметические особенности risc процессоров.

- •Раздел 3. Организация памяти в эвм

- •Основные среды хранения информации.

- •Виды запоминающих устройств.

- •Память с произвольной выборкой.

- •Постоянные запоминающие устройства.

- •Ассоциативные запоминающие устройства (азу)

- •Иерархическая система памяти

- •Организация памяти типа кэш.

- •Организация структуры основной памяти в процессорах ix86.

- •Организация виртуальной памяти.

- •Организация виртуальной памяти на i386 и более старших моделях.

- •Организация работы с внешней памятью.

- •Организация работы с файлами на дисках в ms-dos.

- •Раздел 4. Организация системы ввода-вывода в эвм.

- •Архитектура систем ввода-вывода.

- •Способы выполнения операции передачи данных

- •Структуры контроллеров внешних устройств, для управления различными режимами передачи данных.

- •Программные средства управления вводом-выводом.

- •Основные компоненты процедуры управления ввода-вывода общего вида

- •Состав и реализация устанавливаемого драйвера символьного типа

- •Литература

- •Краткое введение в язык ассемблера.

- •1. Директивы задания данных

- •2. Директивы сегментации программы

- •3. Директивы группирования.

- •4. Порядок размещения сегментов.

- •5. Директивы ограничения используемых команд.

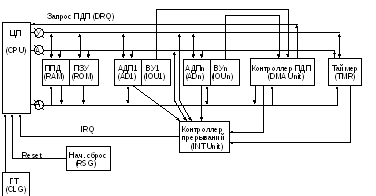

Типовая структура вм на микропроцессорных наборах

ППД – память прямого доступа (RAM–randomaccessmemory);

ПЗУ – постоянное запоминающее устройство (ROM–readonlymemory)

АДП – адаптер (контроллер для подключения одного устройства).

ПДП – прямой доступ в память (DMA-direct memory access)

ГТ – генератор тактов (CLG–clockgenerator)

RSG–ResetGenerator

У- шина управления; А- шина адресов; Д- шина данных.

Кроме центрального процессора в состав современной ВМ могут входить сопроцессоры:

математический сопроцессор (NPR–numericalprocessor);

аналоговый процессор (APR–analogprocessor);

процессор цифровой обработки сигналов (ЦОС) (DSP-digitalsignalprocessor).

Раздел 2. Организация процессора и основной памяти вм

В разделе идет речь о машинах с контроллерным управлением, в которых порядок выполнения команд явно задается программой. Машины с потоковым управлением и машины с запросным управлением (редукционные) в данном курсе не рассматриваются.

Процессорвыполняет две функции:

обработка данных в соответствии с заданной программой;

управление всеми устройствами машины.

Управление в соответствии с заданной программой представляется в виде последовательности команд в цифровой форме. Каждая из команд имеет две части:

-

Операционная часть

адресная часть

Операционная часть - задает код операции и режим ее выполнения. Адресная часть – содержит сведения о размещении операндов (данных): непосредственно сами значения данных, адреса данных в памяти или сведения для определения адресов размещения данных в памяти. Формирование исполнительного адреса – этап перехода от сведений об адресе к самому адресу. В адресной части могут быть сведения об отсутствии операндов (нульадресная или безадресная команда ) и от одного (одноадресная команда) до трех операндов (трехадресная команда).

Типовая структура процессора и основной памяти

АЛУ - арифметико-логическое устройство.

РОНы - регистры общего назначения (от 8 до нескольких сотен штук).

Рг СС - регистр слова состояния. Содержит текущее состояние процессора, в который входит уровень приоритета текущей программы, биты условий {j}завершения последней команды, режим обработки текущей команды. Возможны следующие режимы обработки (в порядке возрастания уровня):

UserMode- режим пользователя; в этом режиме не могут выполнятся системные команды (команды изменения состояния процессора и команды ввода- вывода);

SuperVisorMode- режим супервизора; обеспечивается выполнение всех команд ввода- вывода;

KernelMode- режим ядра; возможно выполнение всех команд процессора.

ПС - программный счетчик. Содержит адрес текущей команды и автоматически наращивается для подготовки адреса следующей команды (исключение составляет команда перехода);

Рг Команд - регистр команд. Содержит код исполняемой в данный момент команды;

ДешКОПиРА – дешифратор кода операции и режимов адресации;

Форм-льУС – формирователь управляющих сигналов { Уi};

РАП - регистр адреса памяти; РДП - регистр данных памяти;

РгУС – регистр управляющего слова контроллера памяти;