- •Розділ 1 аналіз предметної області та постановка задачі

- •1.1 Загальні відомості про логічні інтегральні схеми

- •1.2 Програмовані логічні інтегральні схеми

- •1.2.1 Класифікація програмованих логічних пристроїв

- •1.3 Spld (Прості pld)

- •1.4 Пристрій cpld

- •1.5. Пристрій fpga

- •1.6 Основи периферійного сканування jtag

- •1.7 Граф машини станів контролера tap (Test Access Port)

1.6 Основи периферійного сканування jtag

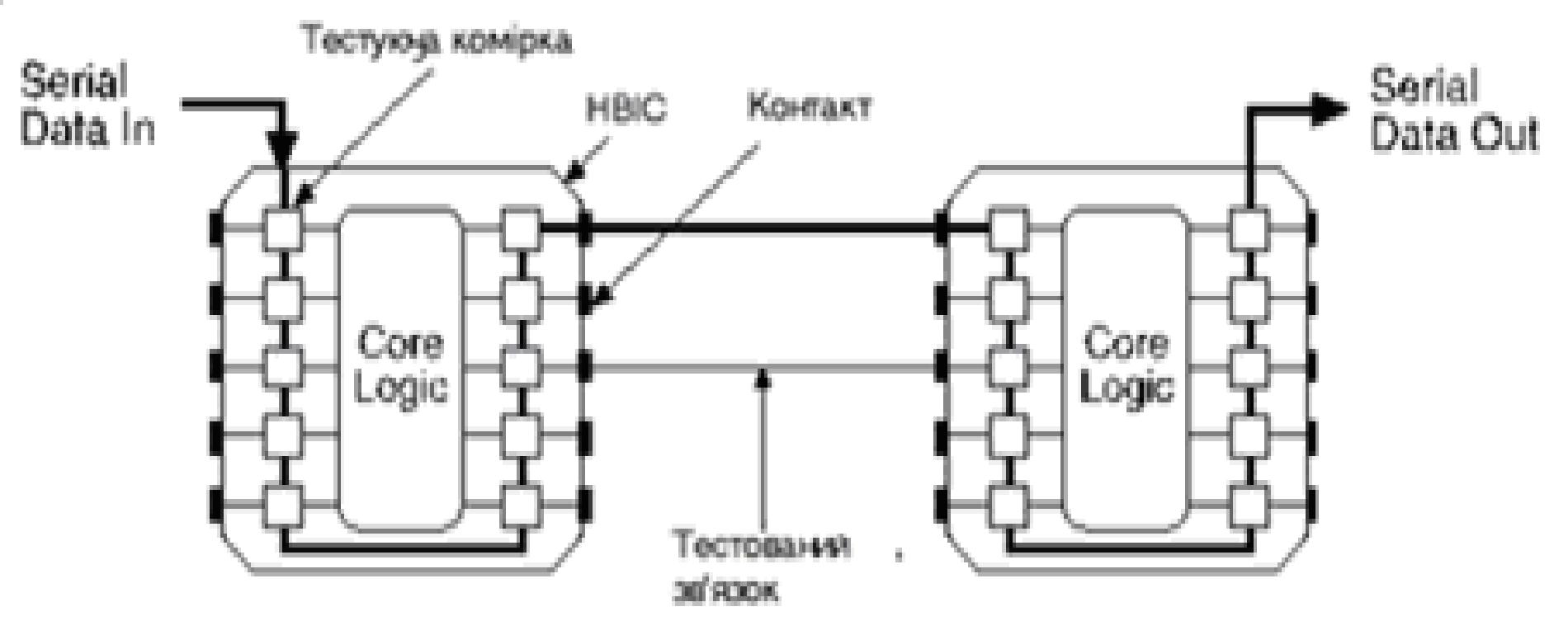

Запис файлу конфігурації в ПЛІС виконується, як правило, через інтерфейс JTAG . В 1985 році спеціальна група провідних виробників електроніки JTAG (Joint Test Action Group) висунула як промисловий стандарт для рішення проблем тестування специфікацію IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). Цей стандарт передбачав убудовування в цифрові НВІС спеціальних тестових осередків, об'єднаних у регістр зсуву й контролюючих зовнішніх сигналів (рис.1.6).

Вбудовування таких осередків забезпечує доступ до виводів чипа (точніше, до спеціальних блоків вводу-виводу) за допомогою 4-проводного послідовного інтерфейсу JTAG. Ця архітектура дозволяє не тільки контролювати, але й керувати станом виводів. У такий спосіб можна обійтися без громіздких пробників з фізичним контактом. Тестування здійснюється шляхом послідовного завантаження тестового вектора в тестові осередки й зчитування результатів. Тестувати можна як сигнали усередині ВІС, так і зв'язки між різними ВІС.

Рис.1.6 - Схема підключення тестових осередків

Кожен тестовий осередок містить 1-2 мультиплексори, керовані контролером JTAG , і 1-2 тригера, синхронізовані тактовим сигналом . Ця архітектура може бути доповнена можливістю обмінюватися й іншою інформацією із чипом. Наприклад, одержувати результат внутрішнього тесту, як це робиться в сучасних процесорах. У ПЛІС ця архітектура забезпечує можливість уведення конфігураційних даних. Усі JTAG-пристрої поєднуються в послідовний ланцюжок і неявно адресуються своїм положенням.

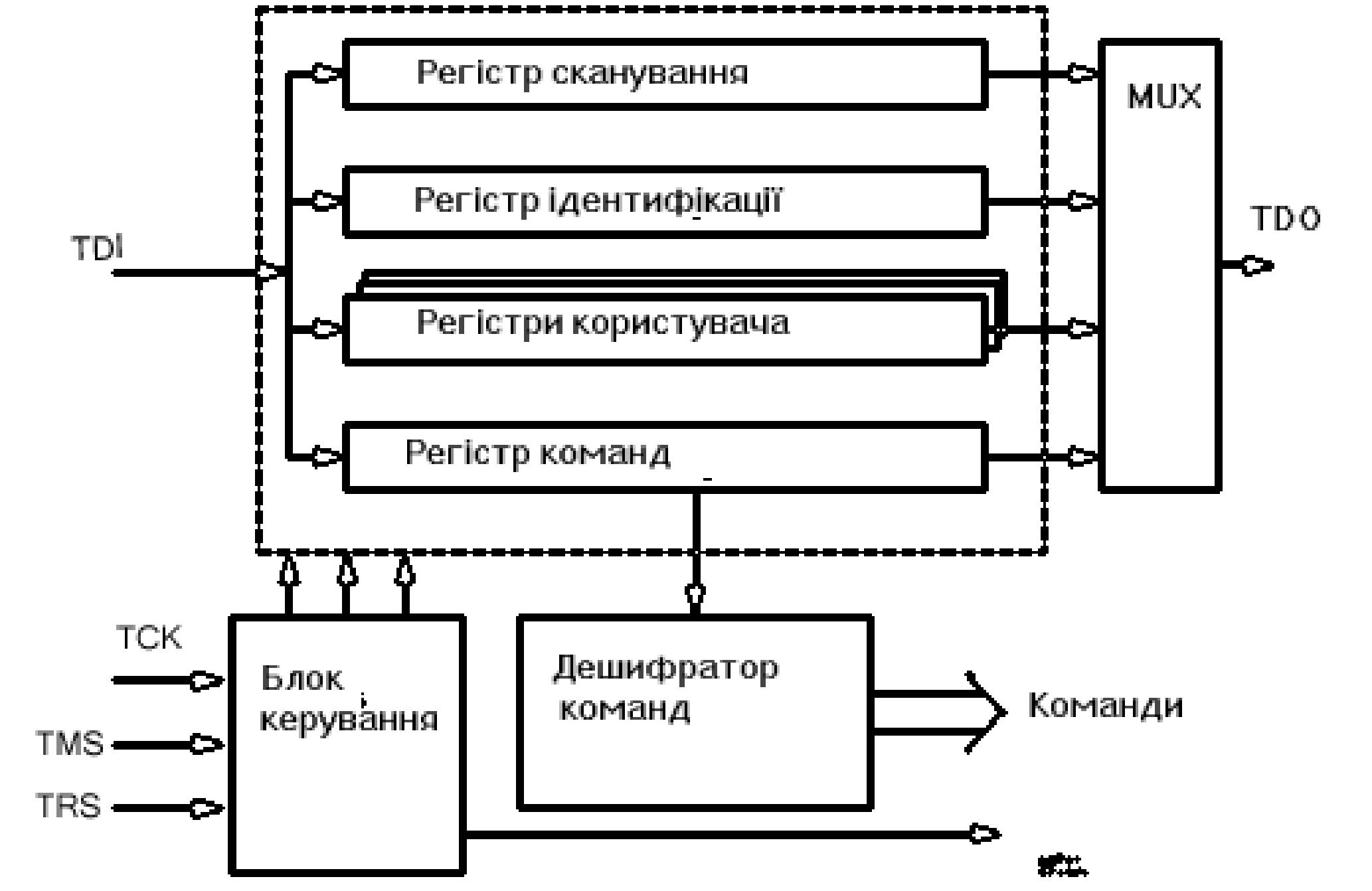

Рис.1.7 - Структура регістрів

Загальна структура JTAG-блоку наведена на рис.1.7. Вона включає набір послідовних регістрів (периферійного сканування, команд, користувача, ідентифікації), підключених до вихідного мультиплексора, контролер доступу й дешифратор команд.

Таблиця 2.1. Контакти порту JTAG

Контакт Ім'я |

Опис |

|

TDI |

Test Data Input |

Послідовний вхід регістра зсуву. Дані фіксовані по передньому фронту імпульсу на TCK |

TDO |

Test Data Output |

Послідовний вихід регістра зсуву. Дані виводяться по задньому фронту імпульсу на TCK |

TMS |

Test Mode Select |

Вхід керування машиною станів TAP-контролера. Дані фіксовані по передньому фронту імпульсу на TCK |

TCK |

Test Clock Input |

Вхід синхронізації |

TRST |

Test Reset Input |

Асинхронне скидання всієї схеми з ініціалізацією TAP-контролера. (необов'язковий контакт) |

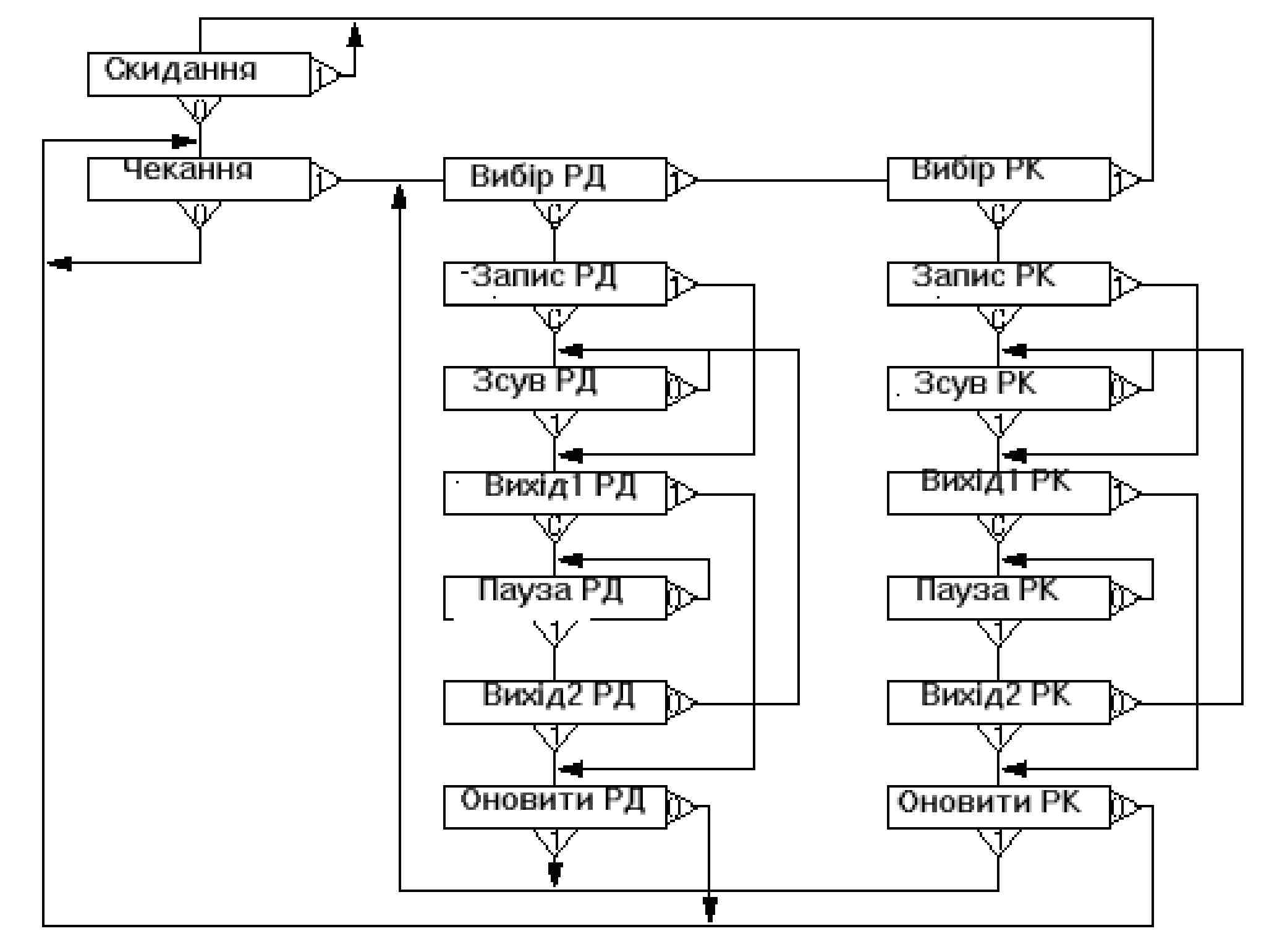

1.7 Граф машини станів контролера tap (Test Access Port)

Контролер являє собою скінченний автомат, описуваний графом станів. Як видно із графа (рис.1.8), TAP-контролер перейде у вихідний стан Скидання з будь-якого іншого не більш ніж за 5 імпульсів TCK за TMS=1. При цьому відбудеться скидання всієї схеми, а в регістр команд (РК) запишеться значення за замовчуванням (як правило, інструкція IDCODE, але може бути й інша, наприклад SAMPLE). Щоб уникнути цього скидання, слід проводити контролер TAP через безпечний стан Чекання, у якому всі робочі установки зберігаються.

Схема ВST містить цілий набір регістрів зсуву. При проході по правій гілці графа доступний регістр інструкцій довжиною від 3 біт. Завантажена інструкція визначає один з регістрів даних (РД), доступних при проході по лівій гілці, і дії з ними в певних станах TAP-контролера. Із цих регістрів, як мінімум, наявний звичайно регістр доступу до зовнішніх виводів схеми й однобітний регістр обходу.

Оскільки в ланцюжку JTAG-пристроїв усі регістри зсуву складаються в один довгий, то регістр обходу дозволяє зменшити цю довжину, представляючи обійдені пристрої всього одним бітом. Для цього використовується інструкція BYPASS. Оскільки уведення інструкції BYPASS скасовує дію раніше завантаженої інструкції, то, на жаль, неможливо зберегти стан блоків вводу-виводу, установлений інструкціями типу EXTEST й INTEST. Винятком є інструкція CLAMP, після якої можна використовувати регістр обходу. Але ця інструкція в тестових програмах практично не зустрічається.

У регістрі доступу для кожного блоку вводу-виводу ПЛІС, як правило, відведені три послідовні біти: вхід (I), вихід (O) і заборона виходу (T). Порядок виводу біт на TDO різний для ПЛІС різних фірм. Наприклад, для Xilinx - (T,O,I), а для Altera - (I,T,O).

У стані Запис в обраний регістр зсуву записується поточний стан. Для регістра інструкцій звичайно це код інструкції SAMPLE, а для регістра обходу -логічна одиниця. У стані Оновити дані з регістра зсуву переносяться у відповідний регістр зберігання.

Рис.1.8 - Граф переходів контролера

У такий спосіб інструкція SAMPLE не тільки зчитує поточний стан зовнішніх виводів, алі й записує в регістрі зберігання керуючі дані. Тому, щоб уникнути виведення випадкової інформації, її використтовують перед завантаженням інструкцій типу EXTEST або INTEST.

Під час завантаження інструкції EXTEST виходи регістра зберігання визначають стан виходів ПЛІС, тобто керують виходом і його третім станом. У такий спосіб можна протестувати зовнішні зв’язки. Інструкція INTEST, навпаки, підмінює вхідний сигнал і використовується для перевірки НВІС. Часто обмежуються однією інструкцією EXTEST, використовуючи біт входу (I) для уведення в НВІС як в інструкції INTEST.

Інструкція IDCODE підключає вбудований 32-бітний регістр із ідентифікаторами виробника, моделі й версії пристрою, який має таку структуру:.

Version |

Part Number |

Manufacturer Identity |

Fixed "1" |

Біти 31-28 |

Біти 27-12 |

Біти 11-1 |

Біт 0 |

Набір інструкцій визначається виробником. Як мінімум, наявні SAMPLE, BYPASS й EXTEST. Інші інструкції - додаткові. Як уже згадувалося, для ПЛІС можуть бути спеціальні інструкції конфігурування, а для мікропроцесорів -читання результату внутрішнього тесту.

Таблиця 2.2. Інструкції JTAG

Інструкція |

Призначення |

BUPASS "11..1" |

Обхід регістра доступу через 1-бітний регістр обходу |

SAMPLE |

Зчитування стану блоків вводу-виводу й підготовка даних для інструкцій керування |

EXTEST "00..0" |

Тест зовнішньої схеми (off-chip) |

INTEST |

Тест внутрішньої схеми (on-chip) |

RUNBIST |

Режим самотестування |

CLAMP |

Подібно EXTEST, але виходи залишаються зафіксованими за використання регістра обходу |

HIGHZ |

Установлення всіх виходів у 3-й стан |

IDCODE |

Підключення 32-бітного ідентифікаційного регістра |

USERCODE |

Додатковий 32-бітний регістр із нефіксованим значенням |

Виробники мікросхем надають інформацію про конкретну реалізацію тестування для кожного типу своєї продуції у вигляді BSDL-файлу (Boundary-Scan Description Language)..

Доступ до JTAG порту можна організувати за допомогою спеціального кабелю , підключивши їм тестовану систему до паралельного порту або порту USB комп'ютера. Для надійної роботи сигнали паралельного порту підключаються через буферні схеми.