- •1. Цель курсовой работы

- •2. Объем курсовой работы

- •3. Методика выполнения работы

- •3.1. Стратегия проектирования

- •3.2. Понятие Проекта

- •3.3. Ввод проекта

- •3.3.1. Графический ввод проекта

- •3.3.2.Иерархическое описание проекта

- •3.3.3. Описание проекта на уровне конечного автомата

- •4. Верификация проекта.

- •5. Содержание отчета по курсовой работе

- •6. Литература

3.3.1. Графический ввод проекта

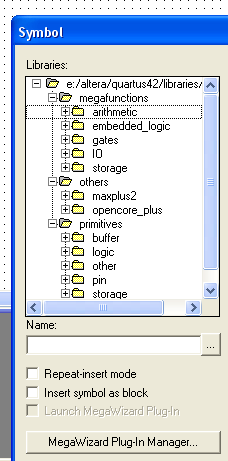

Ввод проекта осуществляется с использованием редактора Block Diagram/Schematic. При этом используются имеющиеся в библиотеке стандартные элементы (макрофункции пакета Quartus II ), хранящиеся в меню Symbol, доступном при открытом файле графического редактора.

В данном меню доступны как элементы простой логики (элементы И, ИЛИ, НЕТ, И-НЕ и т. д.), так и типовые цифровые устройства, создаваемые с использованием встроенных параметризированных функций или с помощью MegaWizard Plug-In Manager (рис.4).

Рис.4.

Информацию о функционировании используемых элементов (таблицы истинности, назначение выводов и т.д.) можно получить непосредственно из встроенного в систему Quartus II Web Edition Software Version 4.2 справочника.

После моделирования полученного проекта создается его символ (File – Create Default Symbol.). При необходимости созданный символ может быть отредактирован (File – Edit Symbol).

3.3.2.Иерархическое описание проекта

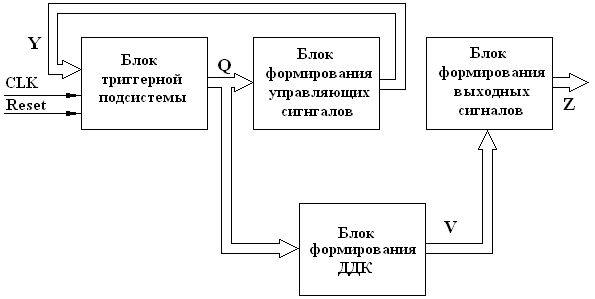

При использовании иерархического описания схему цифрового автомата разбивают на самостоятельные блоки в соответствии со структурной схемой рис.5.

Описание поведения каждого из выделенных блоков выполняется с использованием языка AHDL на поведенческом уровне (Text Editor).

Каждый из созданных блоков моделируется самостоятельно, причем на входы блоков подается возрастающая последовательность двоичных кодов соответствующей разрядности.

С использованием полученных примитивов создается файл верхнего уровня иерархии, описывающий поведение устройства в целом. Для верификации работы полученного проекта выполняется его моделирование (Simulator).

3.3.3. Описание проекта на уровне конечного автомата

Описание на уровне цифрового автомата выполняется с использованием текстового редактора пакета (Text Editor). Основой описания служит граф переходов, заимствованный из курсовой работы по дисциплине «Схемотехника электронных средств».

Рис.5.

После компиляции проекта правильность его функционирования проверяется моделированием (Simulator).

4. Верификация проекта.

Заключительным этапом выполнения курсового проекта является его верификация с использованием лабораторного стенда. Подробное описание стенда и порядок выполнения работы при программировании реальной ПЛИС подробно изложен в Методических указаниях к лабораторной работе № 1 - 4S. «Программирование ПЛИС» и «Общая технология проектирования часть 5».

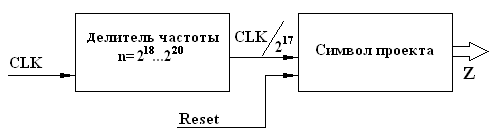

Программируются все три разработанных проекта. При этом необходимо помнить, что частота работы задающего генератора стенда составляет порядка 130 КГц и для визуальной проверки работы проекта ее необходимо дополнительно разделить на 218…220 . С этой целью проект, разработанный в графическом редакторе, дополняется вспомогательным делителем частоты, и моделирование выполняется в схеме, согласно рис.6.

Рис.6.

Делителя частоты синтезируется с использованием встроенного в пакет Quartus II Web Edition Software Version 4.2 примитива счетчика (LPM_COUNTER).

Верификация иерархического проекта выполняется с использованием пошагового режима работы. Для этого на вход CLK проекта задается последовательность одиночных импульсов, формируемых встроенным в стенд одновибратором.

Для верификации проекта, выполненного с привлечением описания на уровне конечного автомата, в текстовый файл проекта вводится дополнительный делитель, обеспечивающий заданный коэффициент деления частоты задающего генератора лабораторного стенда.

Примечания: 1. Перед программированием ПЛИС студент должен получить у преподавателя номера семисегментных индикаторов, которые необходимо использовать при верификации проектов.

2. Необходимо помнить, что программатор системы Quartus II Web Edition Software Version 4.2 производит присвоение всех имеющихся в проекте выводов, вне зависимости от того перечислены ли они специально в опции Assignment Editor или нет. Поэтому, если специально не указаны выводы ПЛИС к которым должны быть подключены некоторые выходы проекта, программатор назначит их самостоятельно. На практике, так как выходы ПЛИС жестко связаны с цепями задания входных сигналов и нагрузкой, может оказаться, что часть выходов проекта окажется подсоединенной к выводам, на которых внешними цепями принудительно формируются входные сигналы. Это приведет к нарушению алгоритма работы устройства. При использовании в проекте дополнительных тестовых выводов (например, выводов триггерной подсистемы) их рекомендуется подключать к выводам, связанным с одиночными светодиодными индикаторами.