- •Экзаменационные вопросы вмсс 3-мд-5,6 (осень-2008)

- •Аналоговые схемы

- •Цифровые схемы

- •Высоконадежная память:

- •Внешние интерфейсы компьютера

- •Внутренние интерфейсы компьютера

- •1. Дублирование информации

- •2. Контрольная сумма

- •3. Контроль паритета

- •4. Двухмерный контроль паритета

- •5. Код Хемминга

- •Циклические коды crc

Экзаменационные вопросы вмсс 3-мд-5,6 (осень-2008)

Архитектура ВМ.

Архитектура персонального компьютера — компоновка его основных частей, таких как процессор, ОЗУ, видеоподсистема, дисковая система, периферийные устройства и устройства ввода-вывода. Основы учения об архитектуре вычислительных машин заложил выдающийся американский математик Джон фон Нейман.

Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и предложил ее структуру, которая воспроизводилась в течение первых двух поколений ЭВМ. Основными блоками по Нейману являются устройство управления (УУ) и арифметико-логическое устройство (АЛУ) (обычно объединяемые в центральный процессор), память, внешняя память, устройства ввода и вывода. Схема устройства такой ЭВМ представлена на рис. 1. Следует отметить, что внешняя память отличается от устройств ввода и вывода тем, что данные в нее заносятся в виде, удобном компьютеру, но недоступном для непосредственного восприятия человеком. Так, накопитель на магнитных дисках относится к внешней памяти, а клавиатура – устройство ввода, дисплей и печать – устройства вывода.

Рис. 1. Архитектура ЭВМ, построенной на принципах фон Неймана. Сплошные линии со стрелками указывают направление потоков информации, пунктирные – управляющих сигналов от процессора к остальными узлам ЭВМ

Устройство управления и арифметико-логическое устройство в современных компьютерах объединены в один блок – процессор, являющийся преобразователем информации, поступающей из памяти и внешних устройств (сюда относятся выборка команд из памяти, кодирование и декодирование, выполнение различных, в том числе и арифметических, операций, согласование работы узлов компьютера). Более детально функции процессора будут обсуждаться ниже.

Память (ЗУ) хранит информацию (данные) и программы. Запоминающее устройство у современных компьютеров “многоярусно” и включает оперативное запоминающее устройство (ОЗУ), хранящее ту информацию, с которой компьютер работает непосредственно в данное время (исполняемая программа, часть необходимых для нее данных, некоторые управляющие программы), и внешние запоминающие устройства (ВЗУ) гораздо большей емкости, чем ОЗУ. но с существенно более медленным доступом (и значительно меньшей стоимостью в расчете на 1 байт хранимой информации). На ОЗУ и ВЗУ классификация устройств памяти не заканчивается – определенные функции выполняют и СОЗУ (сверхоперативное запоминающее устройство), и ПЗУ (постоянное запоминающее устройство), и другие подвиды компьютерной памяти.

В построенной по описанной схеме ЭВМ происходит последовательное считывание команд из памяти и их выполнение. Номер (адрес) очередной ячейки памяти. из которой будет извлечена следующая команда программы, указывается специальным устройством – счетчиком команд в УУ. Его наличие также является одним из характерных признаков рассматриваемой архитектуры.

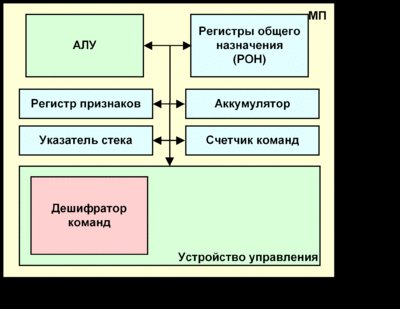

Обобщенная архитектура МП.

Устройство управления управляет работой микропроцессора, обменом с внешними устройствами и обработкой информации. В состав устройства управления входит уже известный нам дешифратор команд.

Аккумулятор предназначен для временного хранения операндов или результатов операции. Если один из операндов хранится в аккумуляторе, операция выполняется максимально быстро. Аккумулятор представляет собой регистр, разрядность которого совпадает с разрядностью микропроцессора.

Регистры общего назначения – набор регистров, предназначенных для временного хранения операндов, результатов операций или других данных. Вообще операнды, используемые в команде, могут храниться либо в одном из внутренних регистров микропроцессора, либо в запоминающем устройстве. Естественно, обращение к операндам, находящимся в ЗУ занимает больше времени. Поэтому часто используемые данные, результаты операций, используемые как операнды для последующих операций, хранятся во внутренних регистрах микропроцессора – аккумуляторе или регистрах общего назначения. Количество регистров общего назначение различно у разных МП.

Способ задания местоположения операндов в команде называется методом адресации. Существуют следующие основные методы адресации:

Непосредственная адресация – значение операнда указывается в самой команде (в виде числа)

Прямая адресация – в команде указывается адрес ячейки ЗУ, в которой находится операнд

Неявная адресация – местоположение операнда явно не указывается, но из описания операции известно, где он находится.

Регистровая адресация – операнд находится в одном из регистров общего назначения микропроцессора или в аккумуляторе. В команде указывается имя (номер, идентификатор) этого регистра.

Регистр признаков (регистр «флагов») – каждый бит этого регистра («флаг») имеет собственное значение и содержит информацию об определенном событии, произошедшем или не произошедшем в процессе выполнения предыдущей команды. Наиболее важными «флагами» являются «флаг» нуля (ZF) и «флаг» знака (NF). «Флаг» нуля равен единице, если в результате предыдущей команды был получен ноль (нулевой результат). «Флаг» знака равен единице, если в результате выполнения предыдущей команды было получено отрицательное число. Эти «флаги» могут быть использованы для организации сравнения чисел. Например, необходимо проверить условие a=b. Для этого достаточно провести вычитание a-b и проанализировать «флаг» нуля: если ZF=1, значит, результат вычитания был нулевым и величины a и b равны. Если ZF=0 – не равны. Аналогично, если после операции вычитания «флаг» знака установился в 1, это говорит о том, что был получен отрицательный результат, то есть значение b больше значения a.

Счетчик команд хранит адрес следующей выполняемой команды. После загрузки очередной команды содержимое счетчика команд увеличивается таким образом, чтобы он опять указывал на следующую команду. При этом предполагается, что в ЗУ команды программы лежат последовательно друг за другом. Если же порядок выполнения команд изменяется (например, при вызове подпрограммы), адрес очередной команды заносится в счетчик команд с помощью специальной команды ветвления.

При выполнении программы часто возникает такая специфическая ситуация, как вызов подпрограммы. При переходе к подпрограмме в счетчик команд записывается новое значение, соответствующее адресу первой команды подпрограммы. После окончания выполнения подпрограммы, должно быть продолжено выполнение основной программы. Таким образом, перед вызовом подпрограммы необходимо запомнить адрес следующей команды основной программы («адрес возврата»), для того, чтобы загрузить его в счетчик команд («восстановить счетчик команд») по окончании выполнения подпрограммы. При этом нужно учитывать, что вызовы подпрограмм могут быть «вложенными» (из первой вызывается вторая, из второй третья и так далее). Для сохранения адресов возвратов из подпрограмм используется специально организованное запоминающее устройство, называемой стеком.

Стек организован по принципу «последним вошел - первым вышел».

Стек представляет собой набор ячеек (регистров), но запись нового числа (a) всегда происходит только в самую верхнюю ячейку, называемую «вершиной» стека. При записи следующего числа (b), первое «продвигается» дальше, вглубь стека, вершина стека освобождается и в нее записывается второе число. Запись третьего (c) и последующих чисел происходит аналогично.

Извлечение данных из стека происходит в обратном порядке (рис. 59). Извлечено может быть только число, находящееся в вершине стека. При его извлечении, находящиеся в стеке данные «продвигаются» вверх и следующее число занимает место в вершине стека и может быть извлечено из него.

Стек может быть организован аппаратно или программно-аппаратно. Аппаратный стек – это специальным образом организованная группа регистров. При помещении данных в вершину стека, его содержимое физически «продвигается» путем перезаписи информации между регистрами. Работа аппаратного стека контролируется специальным блоком управления. Недостаток такого стека – аппаратная сложность и ограниченность объема данных, которые могут быть сохранены.

При программно-аппаратной реализации в качестве стека используется специально выделенная область основного запоминающего устройства. Одна из ячеек этой области является вершиной стека, и ее адрес хранится в специальном регистре микропроцессора, называемом «указатель стека». Именно такой вариант является наиболее распространенным и представлен на рис. 57. При записи данных в стек, уже находящиеся там данные никуда не перемещаются, а «перемещается» вершина стека (путем изменения значения указателя стека), рис. 60. Запись данных всегда происходит в ячейку, являющуюся в данный момент вершиной стека, адрес которой хранится в указателе стека.

При извлечении данных из стека указатель перемещается в обратном направлении (рис. 61). Чтение данных всегда происходит из ячейки, являющейся вершиной стека.

Недостаток программно-аппаратного стека – большее, чем в случае просто аппаратного стека, время, необходимое для записи/извлечения данных. Объясняется это необходимостью обращения к основному ЗУ при каждой операции со стеком. Достоинства – простота аппаратной реализации и отсутствие жестких ограничений на размер стека (фактически его размер ограничен только размером основного ЗУ).

Использование стека для хранения адресов возвратов из подпрограмм позволяет получать адреса возврата в порядке, обратном их помещению. И таким образом обеспечить корректный возврат из подпрограмм даже в случае вложенных вызовов.

В большинстве современных процессоров основной стек, доступный программам, имеет программно-аппаратную реализацию. Соответственно, МП имеет в своем составе регистр- указатель стека. Аппаратный стек применяется в специализированных процессорах

Таким образом, мы рассмотрели обобщенную архитектуру микропроцессора, включающую в себя АЛУ, УУ с ДШК, аккумулятор, РОН, счетчик команд, регистр флагов и указатель стека.

Регистры МП.

Регистр процессора — сверхбыстрая память внутри процессора, предназначенная для хранения адресов и промежуточных результатов вычислений (регистр общего назначения/регистр данных) или данных, необходимых для работы самого процессора. С помощью внутренних шин регистры связаны друг с другом. С другими блоками системы связь осуществляется под управлением программы.

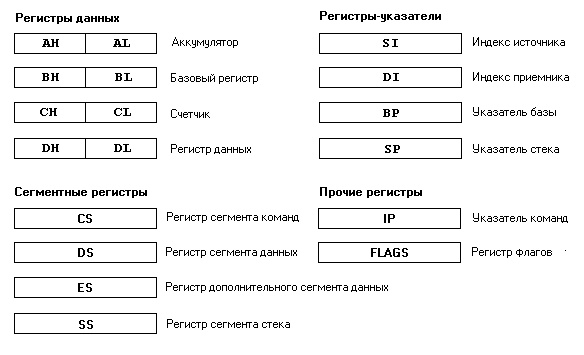

Процессор содержит двенадцать 16-разрядных программно-адресуемых регистров, которые принято объединять в три группы: регистры данных, регистры-указатели и сегментные регистры. Кроме того, в состав процессора входят счетчик команд и регистр флагов.

В группу регистров данных включаются регистры AX, BX, CX и DX. Программист может использовать их по своему усмотрению для временного хранения любых объектов (данных или адресов) и выполнения над ними требуемых операций. При этом регистры допускают независимое обращение к старшим (AH, BH, CH и DH) и младшим (AL, BL, CL и DL) половинам.

Индексные регистры SI и DI так же, как и регистры данных, могут использоваться произвольным образом. Однако их основное назначение — хранить индексы (смещения) относительно некоторой базы (т.е. начала массива) при выборке операндов из памяти. Адрес базы при этом обычно находится в одном из базовых регистров (BX или BP).

Регистр BP служит указателем базы при работе с данными в стековых структурах, но может использоваться и произвольным образом в большинстве арифметических и логических операций или просто для временного хранения каких-либо данных.

Последний из регистров-указателей, указатель стека SP, стоит особняком от других в том отношении, что используеся исключительно как указатель вершины стека.

Четыре сегментных регистра CS, DS, ES и SS хранят начальные адреса сегментов программы и, тем самым, обеспечивают возможность обращения к этим сегментам.

Регистр CS обеспечивает адресацию к сегменту, в котором находится код команд программы, регистры DS и ES — к сегментам данных (таким образом, в любой точке программа может иметь доступ к двум сегментам данных, основному и дополнительному), а регистр SS — к сегменту стека. Сегментные регистры, естественно, не могут выступать в качестве регистров общего назначения.

Указатель команд IP «следит» за ходом выполнения программы, указывая в каждый момент относительный адрес команды, следующей за исполняемой. Регистр IP программно недоступен; наращивание адреса в нем выполняет микропроцессор, учитывая при этом длину текущей команды.

Регистр флагов, эквивалентный регистру состояния процессора других вычислительных систем, содержит информацию о текущем состоянии процессора (рис. 3.2). Он включает 6 флагов состояния и 3 бита управления состоянием процессора, которые, впрочем, тоже обычно называются флагами.

Рис. 3.2. Регистр флагов

Флаг переноса CF (Carry Flag) индицирует перенос или заем при выполнении арифметических операций, а также служит индикатором ошибки при обращении к системным функциям.

Флаг паритета PF (Parity Flag) устанавливается в 1, если младшие 8 бит результата операции содержат четное число двоичных единиц.

Флаг вспомогательного переноса AF (Auxiliary Flag) используется в операциях над упакованными двоично-десятичными числами. Он индицирует перенос или заем из старшей тетрады (бита 4).

Флаг нуля ZF (Zero Flag) устанавливается в 1, если результат операции равен нулю.

Флаг знака SF (Sign Flag) показывает знак результата операции, устанавливаясь в 1 при отрицательном результате.

Флаг переполнения OF (Overflow Flag) фиксирует переполнение, т.е. выход результата операции за пределы допустимого для данного процессора диапазона значений.

Флаги состояния автоматически устанавливаются процессором после выполнения каждой команды.

Управляющий флаг трассировки TF (Trace Flag) используется в отладчиках для осуществления пошагового выполнения программы. Если TF = 1, то после выполнения каждой команды процессор реализует процедуру прерывания 1 (через вектор прерывания с номером 1).

Управляющий флаг разрешения прерываний IF (Interrupt Flag) разрешает (если равен 1) или запрещает (если равен 0) процессору реагировать на прерывания от внешних устройств.

Управляющий флаг направления DF (Direction Flag) используется особой группой команд, предназначенных для обработки строк. Если DF = 0, строка обрабатывается в прямом направлении, от меньших адресов к большим; если DF = 1, обработка строки идет в обратном направлении.

Таким образом, в отличие от битов состояния, управляющие флаги устанавливает или сбрасывает программист, если он хочет изменить настройку системы (например, запретить на какое-то время аппаратные прерывания или изменить направление обработки строк).

Система команд МП. Структура команды.

Система команд - это набор допустимых для данного процессора управляющих кодов и способов адресации данных. Система команд жестко связана с конкретным типом процессора, поскольку определяется аппаратной структурой блока дешифрации команд, и обычно не обладает переносимостью на другие типы процессоров

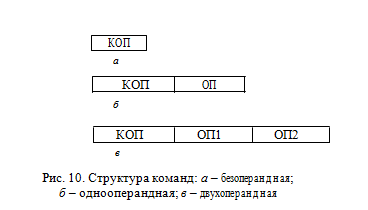

Машинная команда задается ее кодом (числом). Код команды может зани- мать один или более байтов. Код команды содержит неизменную для каждой команды часть, которая называется кодом операции (КОП). КОП определяет конкретную команду. Кроме того, в код команды могут входить один или два операнда. Операнд – это то, над чем осуществляется действие. Операндом мо- жет быть константа, регистр, ячейка памяти (точнее, операндом является содер- жимое регистра или ячейки памяти). Безоперандная (рис. 10, а) машинная ко- манда состоит только из кода операции. Однооперандная (рис. 10, б) машинная команда состоит из кода операции и одного операнда. Двухоперандная (рис. 10, в) машинная команда состоит из кода операции и двух операндов. В этом случае один из операндов является только источником, а другой источником и прием- ником одновременно.

Способ адресации – это способ получения процессором адреса операнда или перехода на основании информации из адресной части команды. Различают следующие основные способы адресации:

· прямая – адрес операнда или перехода содержится в АЧ команды;

· непосредственная – в АЧ команды содержится значение операнда;

· регистровая – в коде команды содержится указание на один или два регистра процессора, являющихся источниками операндов или приемником результата;

· косвенная регистровая – в коде команды содержится указание на какой-либо регистр процессора, содержимое которого при выполнении команды интерпретируется процессором как адрес ячейки памяти, содержащей операнд;

· косвенная базовая (иногда – индексная) – адрес операнда формируется (вычисляется) процессором в ходе выполнения команды как сумма содержимого одного из регистров и смещения (числа), задаваемого в команде, либо как сумма содержимого двух регистров. Таким образом, базовая или индексная формы адресации также являются разновидностью косвенной адресации.

Важной характеристикой команды является ее формат, определяющий структурные элементы команды, каждый из которых интерпретируется определенные образом при ее выполнении. Среди таких элементов (полей) команды выделяют следующие: код операции, определяющий выполняемое действие; адрес ячейки памяти, регистра процессора, внешнего устройства; режим адресации; операнд при использовании непосредственной адресации; код анализируемых признаков для команд условного перехода.

В ажнейшим

структурным элементом формата любой

команды является код операции (КОП),

определяющей действие, которое должно

быть выполнено. Большое число КОП в

процессоре очень важно, так как аппаратная

реализация команд экономит память и

время. Но при выборе ЭВМ необходимо

концентрировать внимание на полноте

операций с конкретными типами данных,

а не только на числе команд, на доступных

режимах адресации. Число бит, отводимое

под КОП, является функцией полного

набора реализуемых команд.

ажнейшим

структурным элементом формата любой

команды является код операции (КОП),

определяющей действие, которое должно

быть выполнено. Большое число КОП в

процессоре очень важно, так как аппаратная

реализация команд экономит память и

время. Но при выборе ЭВМ необходимо

концентрировать внимание на полноте

операций с конкретными типами данных,

а не только на числе команд, на доступных

режимах адресации. Число бит, отводимое

под КОП, является функцией полного

набора реализуемых команд.

При использовании фиксированного числа бит под КОП для кодирования всех m команд необходимо в поле КОП выделить двоичных разрядов. Однако, учитывая ограниченную длину слова мини- и микроЭВМ, различное функциональное назначение команд, источники и приемники результатов операций, а также то, что не все команды содержат адресную часть для обращения к памяти и периферийным устройствам, в малых ЭВМ для кодирования команд широко используется принцип кодирования с переменным числом бит под поле КОП для различных групп команд.

В некоторых командах необходим только один операнд и они называются однооперандными (или одноадресными) командами в отличие от двухоперандных (или двухадресных), в которых требуются два операнда. При наличии двух операндов командой обычно изменяется только один из них. Так как информация берется только из одной ячейки, эту ячейку называются источником; ячейка, содержимое которой изменяется, называется приемником. Локализацию и обращение к операндам обеспечивают режимы адресации. При введении нескольких режимов адресации необходимо отвести в команде биты, указывающие режимы адресации для каждого операнда. Если предусмотрено восемь режимов адресации, то для задания каждого из них нужно три бита. Почти во всех форматах команд первые биты отводятся для кода операции, но далее форматы команд разных ЭВМ сильно отличаются друг от друга. Остальные биты должны определять операнды или их адреса, и поэтому они используются для комбинации режимов, адресов регистров, адресов памяти, относительных адресов и непосредственных операндов. Обычно длина команды варьируется от 1 до 3 и даже 6 байт. По форматам команд можно судить о возможностях ЭВМ.

Архитектура базового МП86. АЛУ и регистр флагов.

Более подробно изучать архитектуру процессора удобней на примере кон- кретного процессора. В данных методических указаниях выбран микропроцес- сор 8088. Выбор этого процессора обусловлен, с одной стороны, его относи- тельной простотой, с другой – выпускаемые в настоящее время процессоры фирмы INTEL, используемые в персональных компьютерах, полностью под- держивают архитектуру процессора 8088. Поэтому он не потерял своей актуаль- ности.

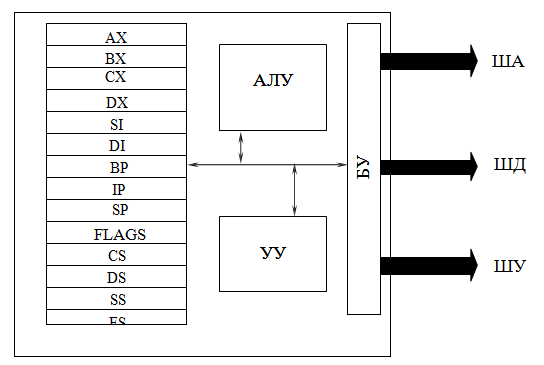

Под микропроцессором понимается процессор ЭВМ, выполненный в виде одной (иногда нескольких) микросхемы. Архитектура микропроцессора 8088 изображена на рис. 5.

Рис. 5. Архитектура микропроцессора 8088

Микропроцессор имеет 20-разрядную шину адреса и, значит, адресное про-

странство микропроцессора составляет 220 = 1 Мбайт. Шина данных

8-разрядная. Все регистры внутренней памяти 16-разрядные. Регистры АХ, ВХ, CX, DX, SI, DI, BP при первом знакомстве с микропроцессором можно отнести

к регистрам общего назначения, т. е. не имеющим обособленного, специального назначения. Назначение остальных регистров следующие:

IР – регистр программного счетчика;

SР – регистр указателя стека;

FLAGS – регистр флагов;

CS – регистр сегмента кода;

DS – регистр сегмента данных; SS – регистр сегмента стека;

ES – регистр дополнительного сегмента.

Более подробно об этих регистрах будет сказано ниже.

Регистры

АХ,

ВХ,

CX,

DX

могут

быть

использованы

как

два

независимых

Регистры

АХ,

ВХ,

CX,

DX

могут

быть

использованы

как

два

независимых

8-разрядных регистра (рис. 6). При этом для регистра АХ 8-разрядные регистры будут называться AH и AL. Для остальных регистров названия соответственно

будут ВН и BL, CH и CL, DH и DL.

AX

AH AL

AH AL

Рис. 6. Регистр АХ

Регистр флагов. Биты этого регистра называются флагами. Каждый флаг имеет специальное назначение и название (рис. 7). В этом регистре сохраняется информация о некоторых признаках выполненных арифметических и логиче- ских операций. Эти признаки в дальнейшем используются при выполнении ко- манд условных переходов.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

|

|

|

|

OF |

DF |

IF |

TF |

SF |

ZF |

|

AF |

|

DF |

|

CF |

Рис. 7. Регистр FLAGS

Кроме того несколько флагов имеют другое назначение. Назначения флагов и их названия следующие:

CF – флаг переноса. Устанавливается в единицу при наличии переноса из старшего разряда;

PF – флаг четности. Устанавливается в единицу, если результат содержит четное число единиц;

AF – флаг вспомогательного переноса. Устанавливается в единицу при на-

личии переноса из 7-го разряда;

ZF – флаг нуля. Устанавливается в единицу, если результат равен нулю;

SF – флаг знака. Устанавливается в единицу, если старший разряд резуль-

тата равен единице (результат отрицательный);

OF – флаг переполнения. Устанавливается в единицу, если при выполнении арифметических операций произошло переполнение разрядной сетки.

При ненаступлении описанных выше событий флаги устанавливаются в ноль.

IF – флаг разрешения прерываний. Если флаг установлен в единицу, то внешние маскируемые прерывания разрешены. Если флаг установлен в ноль, то прерывания запрещены. Флаг устанавливается в единицу командой STI, в ноль –

командой CLI, (пояснение терминов в п. 2.14);

DF – флаг направления. Используется командами пересылки строк;

TF – флаг пошагового режима. Если флаг установлен в единицу, то после выполнения каждой машинной команды генерируется внутреннее прерывание с

номером 1. Это позволяет индицировать результаты после выполнения каждой машинной команды. Такой режим используется при отладке программ.

АЛУ представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций, а также операции логического сдвига, обнуления, установки и т. п.

АЛУ состоит из регистра аккумулятора, регистра временного хранения, ПЗУ констант, сумматора, дополнительного регистра (регистра В), аккумулятора, регистра состояния программы.

Операции в АЛУ

Выполняемые в АЛУ операции можно разделить на следующие группы:

операции двоичной арифметики для чисел с фиксированной точкой;

операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

операции десятичной арифметики;

операции индексной арифметики (при модификации адресов команд);

операции специальной арифметики;

операции над логическими кодами (логические операции);

операции над алфавитно-цифровыми полями.

Классификация АЛУ

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

для чисел с фиксированной точкой;

для чисел с плавающей точкой;

для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие прием из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметическо-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определенных микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Сегментная организация памяти МП86 в реальном режиме.

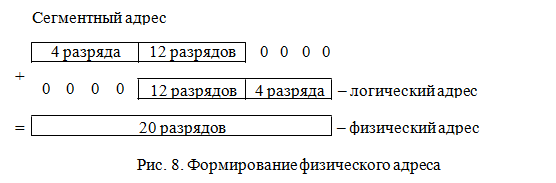

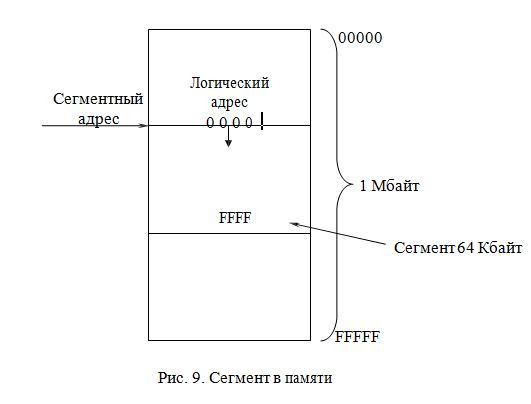

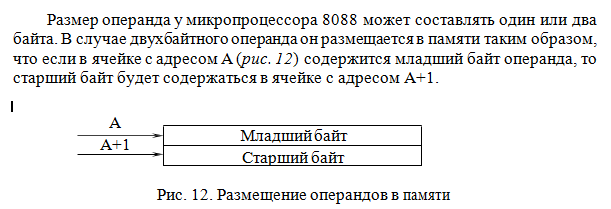

Как отмечалось выше, шина адреса микропроцессора – 20-разрядная, и ад- ресное пространство составляет 1 Мбайт. Микропроцессор имеет сегментную организацию доступа к памяти, суть которой состоит в следующем. Полный

20-разрядный адрес в 1 Мбайтном адресном пространстве называется физиче-

ским адресом. Физический адрес в микропроцессоре 8088 образуется путем сложения двух компонент адреса, как показано на рис. 8. Верхняя компонента называется сегментным адресом. Сегментный адрес 16-разрядный, хранится в одном из сегментных регистров. Нижняя компонента называется логическим адресом или смещением. Логический адрес также 16-разрядный. При сложении недостающие 4 разряда сегментного адреса всегда дописываются нулями, как это и показано на рис. 8.

Такой способ формирования адреса памяти может быть представлен сле- дующим образом (рис. 9). Сегментный адрес задает адрес начала участка памя- ти, называемого сегментом. Логическая компонента адреса задает адрес относи- тельно начала сегмента. Так как логический адрес 16-разрядный, то размер сег- мента составляет 64 Кбайта (216). Как видно из рис. 8, при изменении сегментно- го адреса на единицу физический адрес изменится на 16. Поэтому адрес начала сегмента можно задавать с шагом в 16 байт. Это так же видно, если логический адрес положить равным нулю. Так как в микропроцессоре имеется 4 сегментных регистра, в оперативной памяти можно организовать 4 независимых сегмента. В зависимости от содержимого сегментных регистров сегменты могут быть как не перекрывающимися, так и частично или полностью перекрываться.

Порядок выполнения линейной программы.

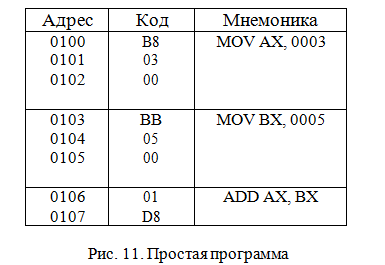

П рограмма

для

ЭВМ

представляет

собой

последовательность

машинных команд,

в

результате

выполнения

которых

решается

поставленная

задача.

Про-

грамма

во

время

выполнения

размещается

в

оперативной

памяти.

На

рис.

11

приведена

простая

программа

для

микропроцессора

8088.

В

графе

«Адрес»

ука-

заны

логические

адреса

каждого

байта

команд.

В

графе

«Код»

приведен

код

со-

ответствующей

команды.

Первая

команда

осуществляет

пересылку

в

регистр

AX

константы

0003,

вторая

соответственно

пересылает

в

регистр

BX

константу

рограмма

для

ЭВМ

представляет

собой

последовательность

машинных команд,

в

результате

выполнения

которых

решается

поставленная

задача.

Про-

грамма

во

время

выполнения

размещается

в

оперативной

памяти.

На

рис.

11

приведена

простая

программа

для

микропроцессора

8088.

В

графе

«Адрес»

ука-

заны

логические

адреса

каждого

байта

команд.

В

графе

«Код»

приведен

код

со-

ответствующей

команды.

Первая

команда

осуществляет

пересылку

в

регистр

AX

константы

0003,

вторая

соответственно

пересылает

в

регистр

BX

константу

0005. Мнемоника ADD означает сложение. Таким образом, третья команда сло- жит содержимое регистров AX и BX, результат будет записан в регистр AX. Можно сказать, что данная программа складывает константы 0003 и 0005, ре- зультат сохраняет в регистре AX. В приведенной программе все команды явля- ются простыми, т. е. выполняются одна за одной.

Стек и указатель стека. Выполнение программы с использованием стека.

Стек (стопка) – это способ обращения к оперативной памяти по принципу "первым пришел, последним ушел". Стек используется для временного хране- ния данных и организации вызова и возврата из подпрограмм. Причем послед- нее является основным назначением стека. Такой способ обращения реализуется

с помощью регистра указателя стека SP. Содержимое этого регистра восприни- мается как адрес верхушки стека. Под верхушкой стека понимается адрес по- следней записи в стек. Применительно к микропроцессору 8088 в регистре SP содержится логическая часть адреса верхушки стека, а сегментная берется из регистра SS.

З апись

в стек осуществляется командой PUSH, а

чтение из стека – коман- дой РОР. В

микропроцессоре 8088 при записи в стек

содержимое регистра SP уменьшается,

затем операнд записывается в ячейку

памяти, адрес которой со- держится в

регистре SP. При чтении из стека читается

содержимое ячейки памя- ти, адрес которой

содержится в регистре SP, после чего

содержимое регистра SP увеличивается.

В микропроцессоре 8088 запись и чтение

стека осуществляется только по два

байта, поэтому при операциях чтения и

записи содержимое реги- стра SP изменяется

на два.

апись

в стек осуществляется командой PUSH, а

чтение из стека – коман- дой РОР. В

микропроцессоре 8088 при записи в стек

содержимое регистра SP уменьшается,

затем операнд записывается в ячейку

памяти, адрес которой со- держится в

регистре SP. При чтении из стека читается

содержимое ячейки памя- ти, адрес которой

содержится в регистре SP, после чего

содержимое регистра SP увеличивается.

В микропроцессоре 8088 запись и чтение

стека осуществляется только по два

байта, поэтому при операциях чтения и

записи содержимое реги- стра SP изменяется

на два.

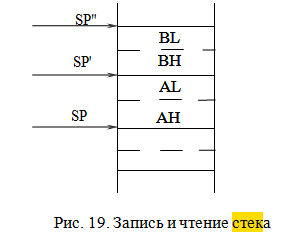

Допустим, выполняется следующая последовательность машинных команд: PUSH AX

PUSH BX РОР AX РОР BX

Процесс записи и чтения из стека представлен на рис. 19. При выполнении первой команды содержимое регистра SP уменьшилось на два (стало SP'), со- держимое регистра AX записывается в ячейку памяти, на которую теперь ука-

зывает регистр SP. При выполнении второй команды, аналогично, регистр SP еще раз уменьшается на два (становится SP") и в соответствующие ячейки запи- сывается содержимое регистра BX. При выполнении команды РОР AX в регистр AX записывается содержимое ячеек памяти, на которые указывает регистр SP,

после чего его содержимое увеличивается на два, становится снова SP'. После выполнения команды РОР BX содержимое регистра SP снова увеличивается на два и становится при этом равным первоначальному значению.

Как можно заметить, в результате выполнения данной последовательности команд содержимое регистров AX и BX поменялось местами. Во избежание этого при написании программ чтение данных из стека необходимо производить в порядке, обратном записи.

Основные функциональные узлы ВМ.

Операционный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация.

Т

риггер

—

устройство, которое может находиться

в одном из двух устойчивых состояний и

сохранять его теоретически бесконечно

долго. Любой триггер является схемой с

памятью или автоматом. Переключение

триггера происходит по входному сигналу

извне.

риггер

—

устройство, которое может находиться

в одном из двух устойчивых состояний и

сохранять его теоретически бесконечно

долго. Любой триггер является схемой с

памятью или автоматом. Переключение

триггера происходит по входному сигналу

извне.

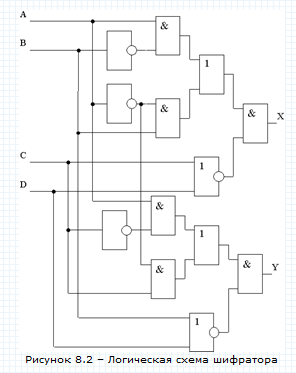

Шифратор - это логическая схема с N входами и М выходами.

Назначение шифратора - выдавать на выходе информацию о том, на какой из входов подан сигнал, используя при этом кодовое слово, содержащее минимум двоичных разрядов, требующееся для этого задания.

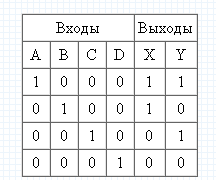

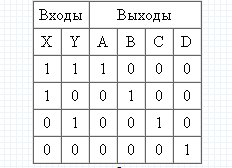

Один из простейших примеров шифратора является шифратор, имеющий четыре входа и два выхода. Этот пример мы и рассмотрим. Составим таблицу, в которой каждому входному сигналу сопоставим последовательность из двух выходных сигналов.

Н![]() а

основании данной таблицы истинности

составим формулу для функций X и Y:

а

основании данной таблицы истинности

составим формулу для функций X и Y:

На основании полученных функций построим логическую схему. Схема должна иметь четыре входа для переменных А, В, C, D и два выхода для функций X, Y. Схема должна иметь четыре входа и два выхода.

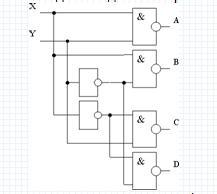

Д

ешифратор

- преобразователь кодов, выполняющий

преобразование входных двоичных кодов

в выходной унитарный код. Унитарный код

двоичного n – разрядного числа

представляется 2n разрядами, только один

из разрядов которого равен 1 (или 0).

Условное описание дешифратора задаётся

формулой nxm (n на m), для полного дешифратора

это формула nx2n. Примерами полных являются

дешифра торы:

1x2, 2x4, 3x8, 4x16.

ешифратор

- преобразователь кодов, выполняющий

преобразование входных двоичных кодов

в выходной унитарный код. Унитарный код

двоичного n – разрядного числа

представляется 2n разрядами, только один

из разрядов которого равен 1 (или 0).

Условное описание дешифратора задаётся

формулой nxm (n на m), для полного дешифратора

это формула nx2n. Примерами полных являются

дешифра торы:

1x2, 2x4, 3x8, 4x16.

Рассмотрим пример. Составим таблицу, в которой каждому выходному сигналу сопоставляется последовательность из двух входных сигналов. На основании данной таблицы истинности составим формулу для функций A, B, C и D:

На основании полученных функций построим логическую схему. Схема должна иметь два входа и четыре выхода.

М![]() ультиплексором

называется комбинационная схема, имеющая

m+2m входов и один выход, где m – количество

адресных входов, а 2m – количество

информационных входов мультиплексора.

Адреса представляются в двоичном коде

и им присваивается номер j. Каждому

адресу с номером j соответствует свой

информационный вход Aj , сигнал с которого

при данном адресе проходит на выход.

Основным назначением мультиплексора

является коммутация 2m входных сигналов

на один выход. Таким образом, мультиплексор

выполняет функцию

ультиплексором

называется комбинационная схема, имеющая

m+2m входов и один выход, где m – количество

адресных входов, а 2m – количество

информационных входов мультиплексора.

Адреса представляются в двоичном коде

и им присваивается номер j. Каждому

адресу с номером j соответствует свой

информационный вход Aj , сигнал с которого

при данном адресе проходит на выход.

Основным назначением мультиплексора

является коммутация 2m входных сигналов

на один выход. Таким образом, мультиплексор

выполняет функцию

Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексор можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора для усиления входного сигнала лучше поставить инвертор.

Сумматор - логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учет знаков чисел, выравнивание порядков слагаемых и тому подобное.

Сумматоры классифицируются по разным признакам:

1. В зависимости от системы исчисления:

Двоичные

Двоично-десятичные (двоично кодированые)

Десятичные

Прочие (пример: амплитудные)

2. По количеству одновременно обрабатываемых разрядов складываемых чисел:

Одноразрядные

Многоразрядные

3. По числу входов и выходов одноразрядных двоичных сумматоров:

Четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

Полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд);

Полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд).

4. По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

Последовательные, в которых обработка чисел ведется поочередно, разряд за разрядом, на одном и том же оборудовании;

П

араллельные,

в которых слагаемые складываются

одновременно по всем разрядам, и для

каждого разряда имеется свое оборудование.

араллельные,

в которых слагаемые складываются

одновременно по всем разрядам, и для

каждого разряда имеется свое оборудование.

Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. На рисунке 14.1 приведена таблица истинности этого сумматора. Ее можно получить исходя из правил суммирования в двоичной арифметике.

Рисунок 14.1 – Таблица истинности сумматора по модулю 2.

Рисунок

14.2 - Принципиальная схема, реализующая

таблицу истинности сумматора по модулю

2.

Рисунок

14.2 - Принципиальная схема, реализующая

таблицу истинности сумматора по модулю

2.

Влияние параметров ИМС на функциональные возможности ВМ.

ИМС - микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус, или без такового, в случае вхождения в состав микросборки.

Часто под интегральной схемой (ИС) понимают собственно кристалл или плёнку с электронной схемой, а под микросхемой (МС, чипом) — ИС, заключённую в корпус. В то же время выражение чип-компоненты означает «компоненты для поверхностного монтажа» (в отличие от компонентов для пайки в отверстия на плате). Интегральная микросхема может обладать законченным, сколь угодно сложным, функционалом — вплоть до целого микрокомпьютера (однокристальный микрокомпьютер).