- •Структура алу.

- •2 Структура алу

- •Организация работы центрального процессора и оперативной памяти.

- •3. Устройство управления.

- •Основная память. Распределение адресного пространства ibm pc xt.

- •Распределение адресного пространства ibm pc at.

- •Страничная организация памяти. Структура страниц.

- •Виртуальная память при страничной организации.

- •8. Виртуальная память при сегментно-страничной организации.

Виртуальная память при страничной организации.

Рисунок 19 – Страничная организация памяти

В физической ОП находятся активные страницы, которые используются в данный момент, а в ВЗУ – пассивные. Обмен страницами между ОП и ВЗУ происходит под управлением ОC с использованием таблиц страниц, которые формирует ОC при распределении памяти на страницы. Таблица страниц всегда находится в физической ОП и содержит виртуальный адрес страницы P, соответствующий ему физический адрес страницы, и тип физической памяти (ОП или ВЗУ), где находится страница.

Преобразование виртуального адреса в физический: Лист 2 рис. Б. При обращении к памяти номер виртуальной страницы P берётся из виртуального адреса и служит для входа в таблицу страниц за номером физической страницы P(n, p), где n – номер программы. Этот номер вместе с номером байта l, взятым из виртуального адреса, образует физический адрес, по которому происходит обращение к ОП.

Если страница находится в ВЗУ, то ОС организует передачу её в физическую ОП и только после этого возможно обращение к странице.

8. Виртуальная память при сегментно-страничной организации.

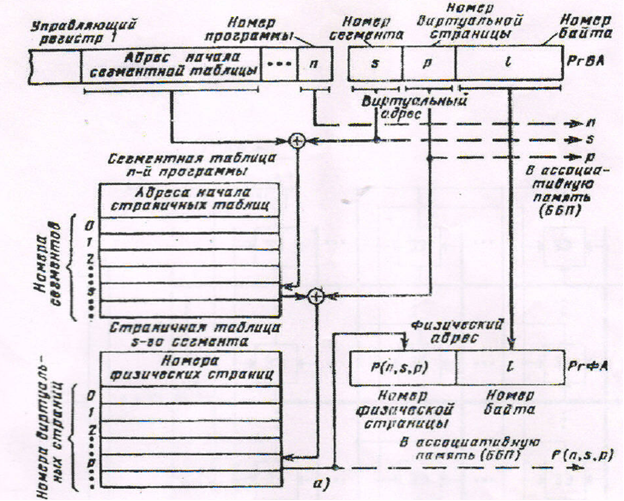

Рисунок 20 - Виртуальная память при сегментно-страничной организации

На практике память делится на сегменты, состоящие из страниц. Если стра-ница стандартна и равна 4К, то сегменты в PM имеют разный объём. Виртуальный адрес страницы дополняется номером сегмента S. Для преобразования виртуального адреса в физический используются 2 вида таблиц – таблица сегментов и таблица страниц, которые формируются ОC при распределении памяти на сегменты и страницы и всегда находятся в физической ОП. Таблица сегментов содержит номер сегмента данной программы и начальные адреса соответствующих им таблиц страниц. Таблица страниц содержит номер виртуальной страницы, соответствующий ей номер физической страницы и тип памяти (ОП или ВЗУ), где находится страница.

Преобразование адресов происходит за 2 обращения к ОП (2 этапа).

Первый этап:

Из специального регистра берётся адрес начала таблицы сегментов и складывается с номером сегмента S из регистра виртуального адреса РгВА. Получается адрес, по которому из таблицы сегментов считывается адрес начала таблицы страниц.

Второй этап:

Адрес начала таблицы страниц суммируется с номером виртуальной страницы p из РgВА. По полученному адресу выбирается номер искомой физической страницы P(n,s,p), где n – номер программы. Если эта страница находится в физической ОП, то её номер сразу заносится в регистр физического адреса РгФА. К нему добавляется номер байта в странице l и по полученному физическому адресу происходит обращение.

Если в ВЗУ, то производится прерывание по страничному сбою. ОC передаёт страницу из ВЗУ в ОП, при этом меняет номер физической страницы P(n,s,p) и только после этого производится обращение.

Одновременно сформированный физический адрес страницы P(n,s,p) передаётся в ББП – буфер быстрой переадресации, куда уже занесён виртуальный адрес страницы n,s,p. ББП – это кэш у современных МП и он хранит эти данные для небольшого числа недавно используемых страниц, поэтому при каждом обращении к ОП преобразование адресов начинается с просмотра ББП лист 3 рисунок б, где ассоциативным признаком является виртуальный адрес страницы. Если виртуальный адрес хранится в ББП, то выбирается соответствующий ему физический и двухэтапного обращения к ОП производится не будет.

9. Мультипроцессорные системы SMP, FRC.

10. Формат дескриптора сегмента.

11. Таблицы дескрипторов (GDT, IDT, LDT).

12. Пользовательские регистры 32-разрядных микропроцессоров.

13. Регистры защищенного режима GDTR, IDTR, LDTR, TR.

14. Регистры управления CR0…CR3.

Определить номер модуля банка и номер ячейки ОЗУ, если на шине адреса выставлен адрес 27D8h.

Шина 16-ти разрядная. Значит два старших разряда А14 и А 15 – номер модуля. А13 и А12 – номер банка. А11 – А0 – номер ячейки.

А15 – А14 – номер модуля |

А13 – А12 – номер банка |

А11 – А0 – номер ячейки |

00 – 0 номер |

10 – 2 банк |

0111 1101 1000 – 2008 ячейка |

Сформировать 20-ти разрядную шину адреса, если слово данных считывается из ячейки с адресом 0D38h, второго банка третьего модуля.

Разрядность ША = 20. Значит два старших байта А19 и А18 – номер модуля. А17 и А16 – номер банка. А15 – А0 – номер ячейки.

Номер модуля |

Номер банка |

В 16 – ой системе |

Номер ячейки |

Ответ |

11 |

10 |

Е |

0D38 |

E0D38h |

Сформировать начальные и конечные адреса всех сегментов основной памяти в реальном режиме работы МП I80486.

В реальном режиме работы размер сегмента всегда постоянен и равен 64 Кб.

Размер страницы = 4 Кб. 16 страниц в сегменте.

Разрядность ША = 32 бита

VОП = 4 Гб

В реальном режиме работы используется только 1 Мб физической памяти

Память Base Memory, (640 Kб) |

|

|

|

||

Область сегментов |

8 сегмент |

00 08 04 00 h |

0000 0000 0000 1000 0000 0100 0000 0000 b |

К. адрес |

|

00 07 04 01 h |

0000 0000 0000 0111 0000 0100 0000 0001 b |

Н. адрес |

|||

7 сегмент |

00 07 04 00 h |

0000 0000 0000 0111 0000 0100 0000 0000 b |

К. адрес |

||

00 06 04 01 h |

0000 0000 0000 0110 0000 0100 0000 0001 b |

Н. адрес |

|||

6 сегмент |

00 06 04 00 h |

0000 0000 0000 0110 0000 0100 0000 0000 b |

К. адрес |

||

00 05 04 01 h |

0000 0000 0000 0101 0000 0100 0000 0001 b |

Н. адрес |

|||

5 сегмент |

00 05 04 00 h |

0000 0000 0000 0101 0000 0100 0000 0000 b |

К. адрес |

||

00 04 04 01 h |

0000 0000 0000 0100 0000 0100 0000 0001 b |

Н. адрес |

|||

4 сегмент |

00 04 04 00 h |

0000 0000 0000 0100 0000 0100 0000 0000 b |

К. адрес |

||

00 03 04 01 h |

0000 0000 0000 0011 0000 0100 0000 0001 b |

Н. адрес |

|||

3 сегмент |

00 03 04 00 h |

0000 0000 0000 0011 0000 0100 0000 0000 b |

К. адрес |

||

00 02 04 01 h |

0000 0000 0000 0010 0000 0100 0000 0001 b |

Н. адрес |

|||

2 сегмент |

00 02 04 00 h |

0000 0000 0000 0010 0000 0100 0000 0000 b |

К. адрес |

||

00 01 04 01 h |

0000 0000 0000 0001 0000 0100 0000 0001 b |

Н. адрес |

|||

1 сегмент |

00 01 04 00 h |

0000 0000 0000 0001 0000 0100 0000 0000 b |

К. адрес |

||

00 00 04 01 h |

0000 0000 0000 0000 0000 0100 0000 0001 b |

Н. адрес |

|||

Область ВП (1 Кб) |

0000 0000 0000 0000 0000 0100 0000 0000 b |

К. адрес |

|||

0000 0000 0000 0000 0000 0000 0000 0000 b |

Н. адрес |

||||

Сформировать начальный и конечный адреса физической ОП объемом 256 мегабайт, если nша=36.

VОП = 64 Гб (всего)

VОП = 256 Мб (дано) 228

|

|

|

|

HMA (свыше 1 мб ОП) |

|

0000 0001 0000 0000 0000 0000 0000 0000 0000 b |

01 00 00 00 0 h |

|

|

|

|

EMA |

|

|

|

0000 0000 0000 0001 0000 0000 0000 0000 0001 b |

00 01 00 00 1 h |

||

UMA |

0000 0000 0000 0001 0000 0000 0000 0000 0000 b |

00 01 00 00 0 h |

|

0000 0000 0000 0000 1010 0000 0000 0000 0001 b |

00 00 A0 00 1 h |

||

Base Memory |

0000 0000 0000 0000 1010 0000 0000 0000 0000 b |

00 00 A0 00 0 h |

|

|

|

||

0000 0000 0000 0000 0000 0000 0000 0000 0000 |

00 00 00 00 0 h |

||

5. Определить начальный и конечный адреса высшей памяти HMA для МП Intel Pentium II.

Ша 32 – разрядная (232 = 4 Гб)

-

Память HMA

(4 095 Мб)

1111 1111 1111 1111 1111 1111 1111 1111 b

FF FF FF FF h

0000 0000 0001 0000 0000 0000 0000 0001 b

00 10 00 01 h

Память UMA

(384 Кб)

0000 0000 0001 0000 0000 0000 0000 0000 b

00 10 00 00 h

0000 0000 0000 1010 0000 0000 0000 0001 b

00 0A 00 01 h

Память Base Memory

(640 Kб)

0000 0000 0000 1010 0000 0000 0000 0000 b

00 0A 00 00 h

0000 0000 0000 0000 0000 0000 0000 0000 b

00 00 00 00 h

640 Кб = 219 + 2 17

6. Найти объем физической ОП МП Intel Pentium III, если с адреса 04000000h начинается виртуальная память.

-

Виртуальная память (начальный адрес)

0000 0100 0000 0000 0000 0000 0000 0000 b

04 00 00 00

Физическая память (конечный адрес)

0000 0011 1111 1111 1111 1111 1111 1111 b

03 FF FF FF

Пространство ФА

Начальный адрес

0000 0000 0000 0000 0000 0000 0000 0000 b

VФ ОП = 226 = 1 Мб * 2 6 = 1 Мб * 64 = 64 Мб

7. Сформировать физический адрес двойного слова в ОП в защищенном режиме МП I80486, если содержимое регистров: EBX=00C81A74h; ESI=0000034Ah; EIP=0002B14Dh и база сегмента в дескрипторе равна 013F8942h.

В реальном режиме работы физически адрес (ФА) находится по формуле:

ФА = Эффективный адрес(ЭА) ⊕ База сегмента

ЭА = Базовый РГ ⊕ Индексный Рг ⊕ Рг смещения

В защищённом режиме работы МП физический адрес определяется также,

Регистр |

Действие |

16-ная с.с. |

2-ная с.с. |

||

EBX |

⊕ |

00 C8 1A 74h |

0000 0000 1100 1000 0001 1010 0111 0100 b |

||

EIP |

00 02 B1 4Dh |

0000 0000 0000 0010 1011 0001 0100 1101 b |

|||

EBX⊕ EIP = |

00 CA AB 39h |

0000 0000 1100 1010 1010 1011 0011 1001 b |

|||

ESI |

⊕ |

00 00 03 4Ah |

0000 0000 0000 0000 0000 0011 0100 1010 b |

||

EBX⊕ EIP⊕ ESI = ЭА |

00 CA A8 73h |

0000 0000 1100 1010 1010 1000 0111 0011 b |

|||

База сегмента |

⊕ |

01 3F 89 42h |

0000 0001 0011 1111 1000 1001 0100 0010 b |

||

ЭА ⊕ База сегмента = ФА |

01 F5 21 31h |

0000 0001 1111 0101 0010 0001 0011 0001 b |

|||

Физический адрес (без страничного преобразования) |

01 F5 21 31h |

0000 0001 1111 0101 0010 0001 0011 0001 b |

|||

Х1⊕Х2 = Х1* Х2

+ Х1* Х2

где Х1 - инверсное значение Х1

Х2 - инверсное значение Х2

8. Определить состояние МПС на базе i80486, если в управляющий регистр CR0 загружены следующие данные: а)100xxxxxxxxxx1x1; б) xxxxxxxxxx110011.

Разряд регистра |

|

|

PE |

1 |

устанавливает защищённый режим на уровне сегментов |

MP |

Х |

|

EM |

1 |

численная операция вызывают недоступность сопроцессора |

TS |

Х |

|

ET |

Х |

|

NE |

Х |

|

6 |

Х |

|

7 |

Х |

|

8 |

Х |

|

9 |

Х |

|

10 |

Х |

|

11 |

Х |

|

12 |

Х |

|

13 |

0 |

|

14 |

0 |

|

15 |

1 |

|

WP |

|

|

|

|

|

AM |

|

|

|

|

|

NW |

|

|

CD |

|

|

PG |

|

|

CR0

MSW – Machine Status Word

CR0 содержит системные флаги управления, относящиеся ко всей системе в целом, а не к выполнению одной команды.

Младшие 16 бит – MSW.

NE – Number error – численная ошибка. NE = 1 разрешает стандартный механизм сообщения об ошибках.

ET – Extended type – тип расширения. ET=1 показывает команды математического сопроцессора.

TS – задача переключена. Устанавливается в 1 при каждом переключении задач.

EM – эмуляция – работает в паре с TS. При переключении задач TS=1, EM=0. Если же TS=1 и EM = 1, то численная операция вызывают недоступность сопроцессора.

MP – присутствие сопроцессора. Начиная с i486DX сопроцессор встроен, поэтому MP равен 1 всегда.

PE! – protect enable – разрешение защиты. PE равный единицы устанавливает защищённый режим на уровне сегментов.

Остальные флаги

PG! – страничное преобразование. =1 разрешает деление сегментов на страницы.

CD – Cash disable – запрещение кэш L1.

NW – несквозная запись в кэш L2. NW = 0 разрешает сквозную запись, 1 – запрещает, что может привести к переполнению кэш L2 и пустой L1.

AM – маска выравнивания. AM=1 разрешает контроль выравнивания по двоичной маске.

WP! – Write Protect. Защита записи. WP = 1 защищает от записи страницу уровня пользователя от обращения супервизора. WP функционирует только при разрешённом страничном преобразовании, то есть CR0[31] = 1 – PG.

9. Закодировать в упакованном и неупакованном форматах кода BCD десятичное число -5482D.

Упакованный формат

В неупакованном формате каждая десятичная цифра обозначается при переводе в двоично-десятичную системы счисления не четырьмя, а восемью битами. Дополнительные четыре бита называются зоной и заполняются единицами («1»)

Digital |

Упакованный формат Binary-digital |

Неупакованный формат Binary-digital |

5 |

0101 |

1111 0101 |

4 |

0100 |

1111 0100 |

8 |

1000 |

1111 1000 |

2 |

0010 |

1111 0010 |

D |

1101 |

1111 1101 |

5482D |

0101 0100 1000 0010 1101 |

1111 0101 1111 0100 1111 1000 1111 0010 1111 1101 |

Знак 1101 – минус - плюс |

|

|

10. Определить базовый адрес и предел дескрипторных таблиц GDT и IDT, если содержимое регистров: GDTR=00B000007FFFh, IDTR=00B080003FFFFh

Базовый = 00B00000h

Предел = 7FFFh