- •Курсовая работа по предмету “Электроника и микросхемотехника” по теме “тема”

- •Содержание

- •Введение

- •Цель работы. Постановка задачи

- •Обзор литературы

- •3. Структурная и функциональная схемы электронного блока

- •3.1. Структурная схема электронного блока

- •3.2. Функциональная схема электронного блока

- •Основные технические характеристики двигателя

- •4. Электрическая принципиальная схема

- •4.1. Расчет выходного импульсного каскада

- •4.2. Расчет предмощного каскада

- •4.3. Расчет гальванической развязки

- •4.4. Расчет элементов задержки

- •4.5. Расчет модулятора

- •4.6 Задатчик

- •4.6.1 Информационные каскады

- •Основные технические данные термометров сопротивления

- •4.6.2 Расчет операционого усилителя

- •4.7. Обратные связи

- •4.8. Расчет схемы защиты от перегрузок и коротких замыканий

- •4.9. Расчет источников питания

- •5.Системные расчеты

- •5.1. Передаточная функция элементов схемы

- •5.2. Лах и фчх электронного блока

- •5.3. Выводы о качественных показателях сау

- •Заключение

- •Литература

- •Приложение

4.4. Расчет элементов задержки

При переключении мощных транзисторов, как правило, транзистор быстрее открывается, чем закрывается (при закрывании сказывается запаздывание из-за эффекта рассасывания неосновных носителей в базе). С учетом этого в стволе, где находятся транзисторы VT1, VT2, могут протекать большие неуправляемые токи (сквозные токи), которые приведут к отказу VT. Стандартный способ борьбы – организация временных задержек на открывание VT, а сигнал на закрывание подается мгновенно.

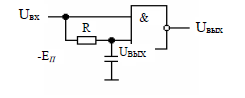

Простое схемное решение изображено на рисунке 4.4.1, где R - сопротивление не более 100 Ом для исключения режима «оборванный вход».

Рисунок 4.4.1 - Схема формирования временной задержки.

Схема И мгновенно срабатывает при входном сигнале – логический ноль. Но когда на входе будет логическая единица (2,4 – 5В), то срабатывание схемы будет тогда, когда емкость зарядится до величины опрокидывания схемы (около 1,2 В).

Существенный недостаток в том, что при таком схемном решении для ТТЛ–логики можно получить максимальную задержку чуть больше 2 мкс (емкость заряжается не только через R, но и через входное сопротивление микросхемы – порядка 3,6 КОм).

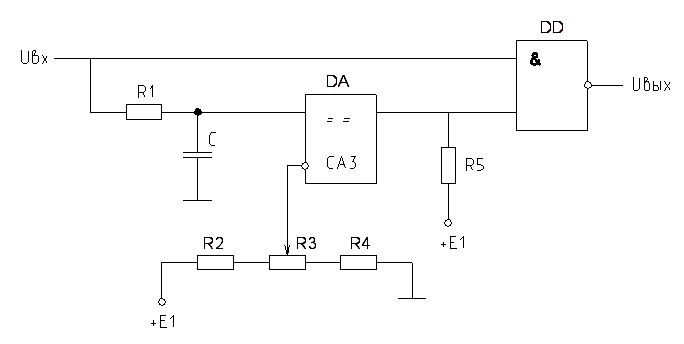

Данную схему можно модифицировать для получения большей задержки (исключить эффект зарядки С через Rвх логики) (рис. 4.4.2).

Рисунок 4.4.2 - Схема формирования временной задержки.

В качестве компаратора DA1 выбираем, как и в предыдущих каскадах микросхему К554СА3, а в качестве инвертора микросхему К555ЛА3.

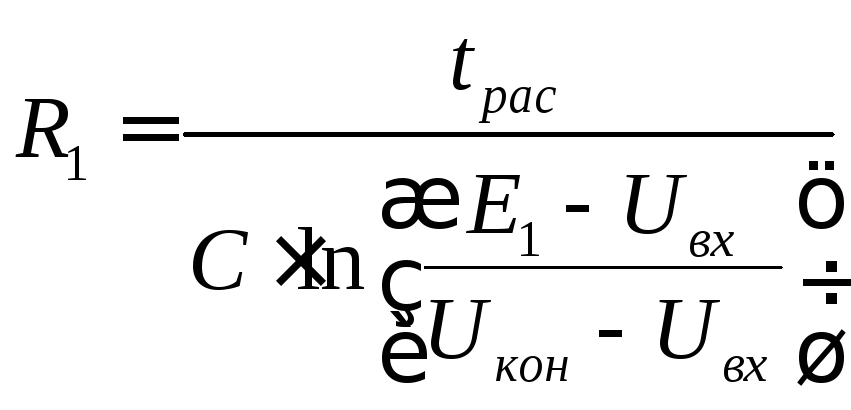

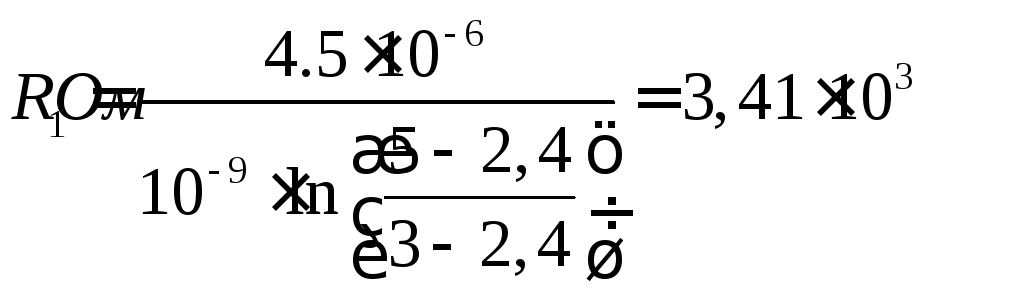

Для расчета RC-цепи используем формулу:

(4.4.1)

(4.4.1)

где

![]() ;

;

![]() –минимальное

напряжение выхода схемы ШИМ,

–минимальное

напряжение выхода схемы ШИМ,

![]() ;

;

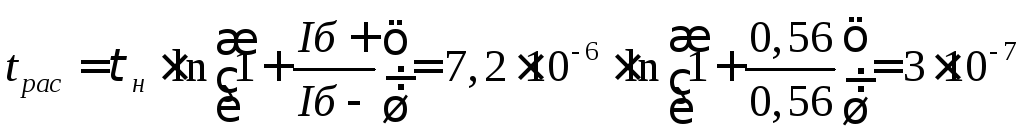

(4.4.2)

(4.4.2)

![]() (справочные

данные VT1, транзисторов предмощного

каскада и оптопары);

(справочные

данные VT1, транзисторов предмощного

каскада и оптопары);

![]() (напряжение

срабатывания DA1);

(напряжение

срабатывания DA1);

С принимаем равным 1нФ.

Тогда:

![]()

Тогда:

.

.

Принимаем

стандартное значение

![]() .

.

На

инверсный вход компаратора подается

через делитель![]() напряжение

напряжение![]() .

Суммарное сопротивление

.

Суммарное сопротивление![]() равно

равно![]() ,

тогда приняв

,

тогда приняв![]() ,

будем иметь

,

будем иметь![]() .

.

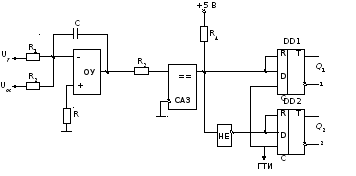

4.5. Расчет модулятора

В курсовом проекте используем интегральный

метод формирования ШИМ[1]. Принципиальная

схема представлена на рисунке 4.5.1.

курсовом проекте используем интегральный

метод формирования ШИМ[1]. Принципиальная

схема представлена на рисунке 4.5.1.

Рисунок 4.5.1 – Схема интегральной ШИМ

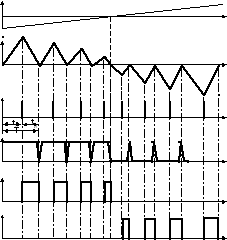

Схема состоит из интегратора, компаратора, инвертора и двух D-триггеров ТМ2. Временные диаграммы ее работы изображены на рисунке 4.5.2.

Эта схема обладает высокой помехоустойчивостью, т.к. и сигнал управления Uy и сигнал обратной связи проходят через интегратор, который является фильтром. При отрицательном знаке Uy на выходе интегратора формируется положительное напряжение Uc и в такт с ГТИ переключается только триггер DD1, при смене знака Uy - триггер DD2, что обеспечит движение якоря двигателя в ту или иную сторону. Таким образом, триггер DD1 должен управлять одной парой транзисторов VT1, VT2, другой – транзисторами VT3, VT4 выходного каскада.

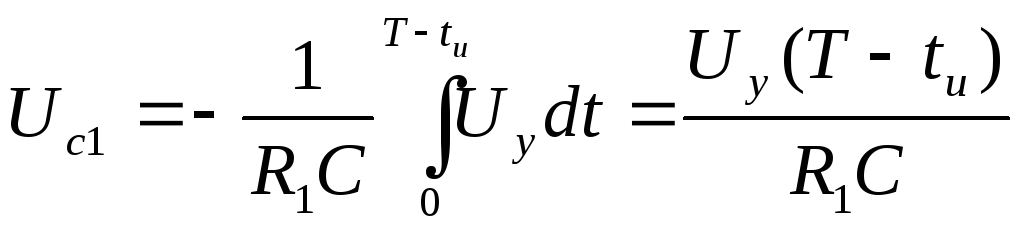

Когда на двигатель не подается управление, то Uoc = 0 и напряжение на выходе интегратора

. (4.5.1)

. (4.5.1)

Когда двигатель запитан, то

,

(4.5.2)

,

(4.5.2)

а полярность напряжений Uy и Uoc должна быть противоположной. Двигатель снова будет обесточен, когда Uс2 = 0 в момент времени t = T. Расчет будем вес вести для Uy = Uy max, тогда tи = tи max.

Uy

Uy

t

Uc

t

ГТИ

t

Uиых комп

t

Q1

t

Q2

t

Рисунок 4.5.2 - Временные диаграммы интегральной ШИМ

Для схемы интегратора выберем универсальный биполярно-полевой операционный усилитель TDB0155, так как он широко распространен. Он имеет следующие характеристики:

Таблица 5.5.1

|

Тип микросхемы |

КyU×103 |

Uсм, мВ |

Iвх, нА |

∆Iвх, нА |

υUиых, В/мкс |

Кос сф, дБ |

Uвх, В |

Uвх сф, В |

Uвых, В |

Iвых, мА (Rн , кОм) |

UИП, В |

IПОТ, мА |

|

TDB0155 |

50 |

10 |

1 |

0,2 |

2 |

- |

10 |

10 |

11,5 |

(2) |

±15 |

4 |

Примем Uy max ≤ 0,8 U+(-)y max ≤ 0,8 ∙ 12 ≤ 9,6 В. Примем Uy max = 9 В.

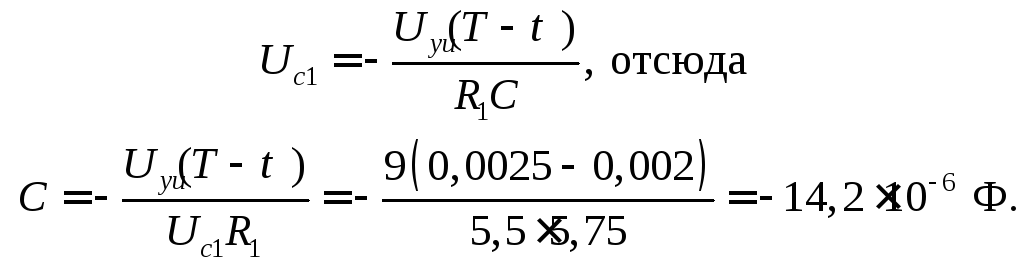

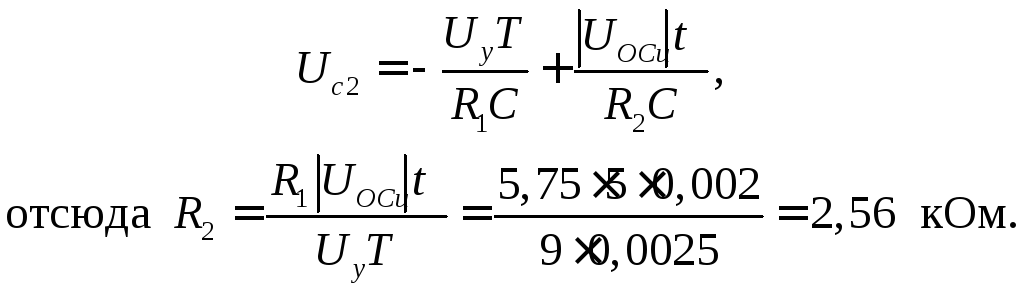

Рассчитаем схему так, чтобы интегратор не заходил в насыщение, т.е. зададимся напряжением Uc1 исходя из следующего условия: Uc1 ≤ U+(-)y max ≤ 12 В.

С целью однотипности элементной базы электронного блока, принимаем, что источником сигнала для первого каскада модулятора принят такой же операционный усилитель, что и в схеме модулятора.

Исходя из этого, рассчитаем величину резистора R1 по формуле:

![]() . (4.5.3)

. (4.5.3)

Принимаем стандартное значение R1 = 6,2 кОм.

Подставляя значение R1 в формулу (4.5.1) найдем значение величины С. При этом принимаем Uc1 не более половины допустимой величины для гарантии работы в активной области, т.е. Uc1 = 5,5 В:

(4.5.4)

(4.5.4)

Затем в (5.5.2) принимаем, что напряжение Uc2 в конце периода равно нулю.

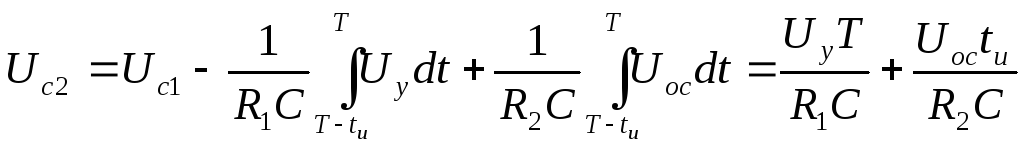

После этого, зададимся напряжением UOC = 5В, получим значение R2:

(4.5.5)

(4.5.5)

Примем стандартное значение R2 = 2,7 кОм.

Значения R3 без расчетов примем равным 1 кОм.

Резистор R4 зададим в тех же пределах (он необходим, так как компаратор типа САЗ имеет открытый коллектор).

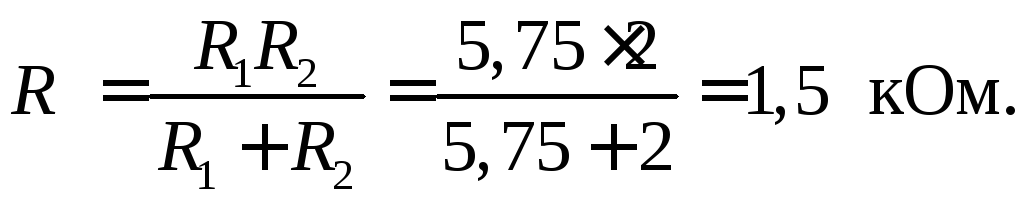

Значение R рассчитаем как параллельное соединение R1 и R2:

(4.5.6)

(4.5.6)

Примем стандартное значение R = 1,8 кОм.

С целью однотипности элементной базы электронного блока возьмем металлодиэлектрические резисторы общего назначения типа С2-33Н.

Для увеличения чувствительности, входного сопротивления, а также снижения потребляемой мощности пороговых устройств возьмем универсальный компаратор К554СА3.Он имеет два выхода: открытый коллектор (вывод 9) и эммитерный (вывод 2). Из-за этих особенностей он пригоден для обслуживания любых цифровых микросхем умеренного быстродействия.

В

качестве генератора тактовых импульсов

(ГТИ) возьмем любой, частота которого

fГТИ

будет равной

и который будет иметь на выходе крутые

фронты, т.к. пологие фронты не опрокинут

триггер.

и который будет иметь на выходе крутые

фронты, т.к. пологие фронты не опрокинут

триггер.

Когда Uy меньше Uy max, то напряжение на выходе интегратора Uc1 max будет понижаться по абсолютной величине, и этим определяется более короткий промежуток tи.

Сигналы

Q1

и

![]() ,Q2

и

,Q2

и

![]() должны

управлять транзисторами мощного каскада.

должны

управлять транзисторами мощного каскада.