- •6.050901 «Радіотехніка»

- •6.170102 «Системи технічного захисту інформації»

- •Изучение основных характеристик логических элементов основных типов

- •1. Методические указания к лабораторной работе

- •1.1. Исследование статических характеристик логических элементов

- •1.2. Исследование динамических характеристик логических элементов

- •2. Содержание отчета

- •3. Приложение

- •3.1. Описание учебно-лабораторного стенда “logic”

- •3.2. Описание микросхем, входящих в состав стенда и используемых для снятия переходной характеристики

- •3.3. Описание микросхем, используемых для снятия динамических характеристик

- •Двухвходового элемента и-не

- •Исследование базовых логических элементов и их комбинаций

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •Синтез комбинационных схем с одним выходом

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •3. Приложение.

- •3.1. Варианты заданий для выполнения лабораторной работы

- •Исследование триггеров

- •1. Методические указания к лабораторной работе

- •1.1. Исследование r-s триггеров

- •1.1.1. Исследование асинхронного r-s триггера

- •1.1.2. Исследование синхронного r-s триггера

- •1.1.3. Исследование r-s триггеров r, s и e типов

- •1.2. Исследование d-триггеров

- •1.2.1. Исследование d – триггера со статическим управлением

- •1.2.2. Исследование d – триггера с динамическим управлением

- •1.3. Исследование т-триггера

- •1.4. Исследование универсального j-k триггера

- •2. Содержание отчета

- •3. Приложение

- •Исследование двоичных счетчиков

- •1. Методические указания к лабораторной работе

- •1.1. Счетчики

- •1.2. Синтез синхронных счетчиков

- •1.2.1. Синтез цепей возбуждения

- •Матрица переходов j-k триггера

- •1.2.2. Синтез цепи переноса в следующие разряды

- •1.3. Динамические параметры счетчиков

- •2.Порядок выполнения работы

- •3. Отчет по работе.

- •Исследование регистров

- •1. Методические указания к лабораторной работе

- •1.1. Регистры

- •1.1.1. Регистры сдвига

- •1.1.2. Регистр сдвига на один разряд

- •1.1.3. Регистр сдвига на k разрядов

- •1.1.4. Реверсивные регистры сдвига

- •1.1.5. Параллельный ввод информации в регистрах сдвига

- •1.1.6. Регистры с обратными связями

- •1. 2. Проектирование многофункциональных регистров

- •1.3. Проектирование комбинационной схемы

- •1.4. Динамические параметры регистров

- •2. Порядок выполнения работы

- •3. Отчет по работе.

- •Состязания сигналов в цифровых схемах

- •1. Краткие теоретические сведения

- •2. Состязания в комбинационных схемах

- •2.1. Статические и динамические состязания сигналов

- •2.2. Синтез схем, свободных от статических состязаний

- •Статического состязания сигналов

- •2.3. Функциональные и логические состязания сигналов

- •На выходе схемы может появиться ложный импульс.

- •2.4. Синтез схем, свободных от логических состязании

- •2.5. Анализ комбинационных схем с целью выявления состязаний

- •3. Состязания сигналов в последовательностных схемах

- •4. Условия надежного функционирования асинхронной схемы

- •4.1. Критические состязания

- •4.2. Существенные состязания

- •5. Порядок выполнения работы

- •6. Отчет по работе должен содержать:

- •Изучение стенда, команд микроконтроллеров семейства mcs-51

- •1. Цель работы

- •2. Приборы и оборудование

- •3. Краткие теоретические сведения

- •3.1.Организация памяти и функционирование микроконтроллера

- •3.2. Запись исходного текста программы на языке программирования asm-51

- •3.3. Встроенные имена

- •3.4. Определяемые имена

- •3.5 Числа

- •3.6. Группа команд пересылки данных

- •3.7. Группа логических команд

- •3.8. Группа арифметических команд

- •3.9. Группа команд управления

- •3.10. Директивы ассемблера asm-51

- •4. Пример выполнения работы

- •5. Задание на выполнение работы.

- •6. Отчет по работе.

- •Изучение программирования встроенных таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •1.1. Режим 0

- •1.2. Режим 1

- •1.3. Режим 2

- •1.4. Режим 3

- •1.5. Управление таймерами-счётчиками.

- •1.7. Использование таймера в качестве частотомера.

- •2. Пример выполнения работы

- •1. Краткие теоретические сведения

- •1.1. Регистр приоритетов прерываний

- •1.2. Регистр разрешения прерываний

- •1.3. Начальные адреса прерываний

- •2. Задание на выполнение работы.

- •3. Отчет по работе.

- •Изучение способов программирования преобразования в двоично-десяичный код и программирования прерываний таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •Структура регистра ie

- •Адреса векторов прерывания

- •Регистр приоритетов прерываний

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

- •Изучение способов построения аналого-цифровых преобразователей с использованием микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

3. Задание на выполнение работы.

Предлагается доработать программу так, чтобы преобразование в упакованный BCD формат осуществлялось с использованием операции вычитания с заемом, производилась динамическая индикация не только секунд, но и минут на левых знакоместах динамического индикатора. Следует обеспечить также сброс и остановку секундомера кнопкой SW15 и запуск кнопкой SW16.

4. Отчет по работе.

Отчет по работе должен содержать:

1. Цель работы;

Краткие теоретические сведения о системе прерываний микроконтроллера

MCS-51 и способах программирования преобразований в упакованный BCD формат;

Листинг работающей в соответствии с индивидуальным заданием программы;

Выводы по работе.

Лабораторная работа № 12

Изучение способов построения аналого-цифровых преобразователей с использованием микроконтроллера mcs-51

Цель работы

Изучение возможностей построения аналого-цифровых преобразователей с использованием MCS-51.

Приборы и оборудование

1. Компьютер с программой – транслятором ASM51.EXE (x8051.EXE) в объектный модуль, программой – редактора связей (преобразования объектного модуля в исполняемый) rl51.EXE и программой преобразования исполняемого модуля в загрузочный OH.EXE или программы fd51.EXE, совмещающей возможности программ rl51.EXE и OH.EXE (при использовании x8051.EXE возможна замена программ rl51.EXE и OH.EXE, необходимых для получения загрузочного модуля, программой LINK.EXE), программой загрузки исполняемого модуля в стенд EVAL32.EXE.

2. Учебно-отладочный стенд EV8031/AVR (V3.2).

1. Краткие теоретические сведения

Аналого-цифровые преобразователи (АЦП) предназначены для преобразования аналоговых (непрерывных) сигналов в цифровую форму. Преобразование аналогового сигнала происходит в определенные моменты времени, которые называются точками отсчета. Количество отсчетов за единицу времени определяет частоту дискретизации (преобразования), которая, в свою очередь, определяется быстродействием и условиями использования АЦП. Интервал времени между отсчетами Тотс и частота дискретизации fпр связаны соотношением:

Тотс = 1/fпр.

В измерительной технике для преобразования медленно меняющихся процессов частота преобразования может быть установлена небольшой - единицы Герц и менее. В устройствах, где требуется преобразовывать сигналы в масштабе реального времени, частота преобразования выбирается из условия достижения максимальной точности восстановления цифрового сигнала в аналоговую форму. Например, преобразование речевого сигнала в дискретную форму. При этом частота дискретизации определяется как fпр = 2Fмах, где Fмах - максимальная частота речевого сигнала.

Для обеспечения преобразования без искажений требуется выполнение условия:

tпр < Тотс,

где tпр - время преобразования АЦП одного отсчета.

Основные параметры АЦП определяются также как и параметры ЦАП.

По принципу дискретизации и структуре построения АЦП делятся на две группы: 1-группа АЦП с применением ЦАП и 2-группа АЦП без ЦАП.

К первой группе относятся:

- АЦП последовательного счета (развёртывающего типа);

- АЦП последовательного приближения (поразрядного уравновешивания);

- следящий АЦП.

К второй группе относятся:

- АЦП прямого преобразования;

- АЦП двойного интегрирования;

- АЦП дифференциального кодирования.

Каждый тип АЦП имеет свои достоинства и недостатки. На практике встречаются все выше перечисленные типы АЦП.

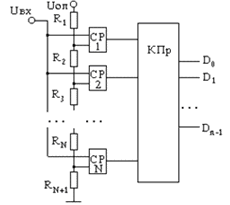

Сравнительные характеристики АЦП. Наибольшим быстродействием обладают АЦП прямого преобразования. Время преобразования tпр достигает 10 -20 нсек. Они используются для преобразования сигналов сверх быстро протекающих процессов и сигналов телевизионного изображения (цифровое телевидение). Они отличаются высокой стоимостью и большой потребляемой мощностью. Функциональная схема АЦП прямого преобразования приведена на рис. 12.1. Она содержит 2n компараторов, делитель опорного напряжения и преобразователь позиционного кода в параллельный двоичный код. Промышленностью выпускаются 4, 6, 8 - разрядные АЦП прямого преобразования. Время преобразования этих АЦП определяется исключительно только временем распространения сигнала в компараторах tздкр и преобразователе кодов tздпр, т.е. tпр = tздкр + tздпр.

Рис. 12.1. Функциональная схема АЦП прямого преобразования:

СР1...СРN – сравнивающие устройства (компараторы); R1...RN –резисторы делителя опорного напряжения; N – число ступеней квантования (N=2n)

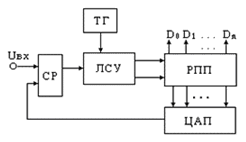

По своему быстродействию на втором месте находятся АЦП последовательного приближения (рис. 12.2). Время преобразования n- разрядного АЦП определяется как tпр = nТ + 3Т, где Т - период следования тактовых импульсов, соответствующий времени выборки одного кванта. Дополнительные 3 такта используются для старта( запуска) и формирования сигналов признака завершения процесса преобразования (сигнала “конец преобразования”).

Рис. 12.2. Функциональная схема АЦП последовательного преобразования:

СР – компаратор напряжения; ТГ – тактовый генератор; ЛСУ – логическая схема управления; РПП – регистр последовательного приближения;

ЦАП – цифро-аналоговый преобразователь

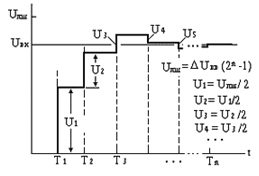

Принцип работы АЦП последовательного приближения иллюстрируется на рис. 12.3. После запуска, на выходе АЦП устатанавливается число, соответствующее половине напряжения полной шкалы Uпш/2. Это напряжение сравнивается с входным напряжением Uвх и, в зависимости от результата сравнения, компаратор вырабатывает два сигнала: U1 , когда Uвых ЦАП > Uвх и U2 при Uвых ЦАП < Uвх . Если Uвых ЦАП меньше, чем Uвх ЛСУ вырабатывает команду, при которой к содержимому регистра последовательного приближения РПП прибавляется число, соответствующее половине напряжения, установленного в предыдущем такте. Если же Uвых ЦАП > Uвх , то из содержимого РПП это число вычитается (см. рис. 12.3). Это происходит до тех пор, пока напряжение приращения не станет равным DUкв , т.е. Un = DUкв =Uпш/2n..

Рис.12.3. Диаграмма выходного напряжения ЦАП, соответствующая десятичному эквиваленту выходного двоичного кода АЦП

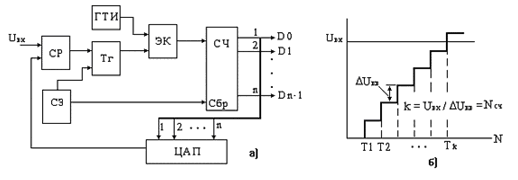

Наибольшим временем преобразования (среди АЦП с использованием ЦАП) обладает АЦП последовательного счета tпр = 2n Т. Они проще в изготовлении и имеют наименьшую стоимость. Погрешность преобразования таких АЦП определяется, в основном, погрешностью ЦАП и может быть доведена до значений прецизионных преобразователей. АЦП последовательного счета переводит аналоговый сигнал в цифровой последовательно, начиная с младшего значащего разряда до цифрового кода на выходе, соответствующего уровню входного аналогового напряжения АЦП. Структурная схема такого АЦП приведена на рис. 12.4, а.

С генератора тактовых импульсов через электронный ключ ЭК, который открывается в момент выборки входного аналогового сигнала схемой запуска (СЗ), последовательность импульсов поступает на n- разрядный двоичный счетчик (СЧ).

Рис. 12.4. АЦП последовательного счета (а) и его временная диаграмма (б)

Выход счетчика является выходом АЦП и одновременно управляет схемой ЦАП, вырабатывающей ступенчато нарастающее напряжение (см. рис. 12.4, б). В момент, когда выходное напряжение ЦАП станет равным входному, компаратор (СР) вырабатывает сигнал, опрокидывающий триггер (ТГ). При этом, сигнал с выхода триггера закроет электронный ключ и остановит счетчик. Содержание счетчика Nсч после его остановки будет соответствовать числу, определяемому входным аналоговым сигналом Nсч = Uвх/ DUкв.

Наибольшее число в счетчике соответствует входному напряжению, равному Uпш. При этом Nсч = 2n.

Упрощенная схема АЦП, работающего в два основных такта (АЦП двухтактного (двойного) интегрирования), приведена на рис. 12.5.

Рис.12.5. Упрощенная схема АЦП двухтактного интегрирования

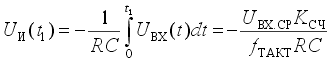

Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1 постоянно; в качестве таймера используется счетчик с коэффициентом пересчета Kсч, так что

(12.1)

(12.1)

К моменту окончания интегрирования выходное напряжение интегратора составляет

(12.2)

(12.2)

где Uвх.ср. - среднее за время t1 входное напряжение. После окончания стадии интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. При этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 12.6.

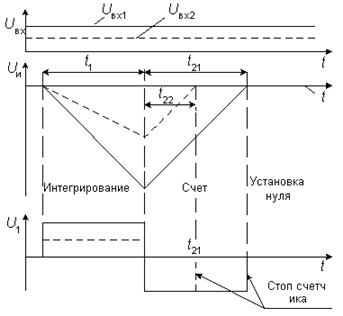

Рис.12.6. Временные диаграммы АЦП двухтактного интегрирования

Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается. Интервал времени, в котором проходит стадия счета, определяется уравнением

(12.3)

(12.3)

Подставив значение Uи(t1) из (2) в (3) с учетом того, что

(12.4)

(12.4)

где n2 - содержимое счетчика после окончания стадии счета, получим результат

(12.5)

(12.5)

Из этой формулы следует, что отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при использовании простого тактового генератора, поскольку существенные временные или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

Из выражений выражений (12.1)...(12.5) следует, что в окончательный результат входят не мгновенные значения преобразуемого напряжения, а только значения, усредненные за время t1. Поэтому переменное напряжение ослабляется тем сильнее, чем выше его частота.

Способ двойного интегрирования позволяет хорошо подавлять сетевые помехи. АЦП двойного интегрирования относится к наиболее медленно работающим преобразователям. Однако, высокая точность, низкий уровень шумов и низкая стоимость делают их незаменимыми для применения в щитовых приборах, мультиметрах, цифровых термометрах и т.п. Этому способствует также то, что результаты преобразования в интегрирующих АЦП часто представляются в десятичном коде или же в удобном виде для представления цифр десятичной системы счисления.

АЦП многотактного интегрирования имеют ряд недостатков. Во-первых, нелинейность переходной статической характеристики операционного усилителя, на котором выполняют интегратор, заметным образом сказывается на интегральной нелинейности характеристики преобразования АЦП высокого разрешения. Для уменьшения влияния этого фактора АЦП изготавливают многотактными. Например, 13-разрядный AD7550 выполняет преобразование в четыре такта. Другим недостатком этих АЦП является то обстоятельство, что интегрирование входного сигнала занимает в цикле преобразования только приблизительно третью часть. Две трети цикла преобразователь не принимает входной сигнал. Это ухудшает помехоподавляющие свойства интегрирующего АЦП. В-третьих, АЦП многотактного интегрирования должен быть снабжен довольно большим количеством внешних резисторов и конденсаторов с высококачественным диэлектриком, что значительно увеличивает место, занимаемое преобразователем на плате и, как следствие, усиливает влияние помех.

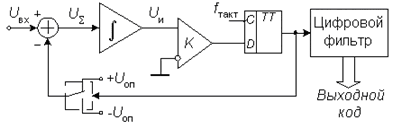

Эти недостатки во многом устранены в конструкции сигма-дельта АЦП (в ранней литературе эти преобразователи назывались АЦП с уравновешиванием или балансом зарядов). Своим названием эти преобразователи обязаны наличием в них двух блоков: сумматора и интегратора. Один из принципов, заложенных в такого рода преобразователях, позволяющий уменьшить погрешность, вносимую шумами, а следовательно увеличить разрешающую способность - это усреднение результатов измерения на большом интервале времени. Основные узлы АЦП - это сигма-дельта модулятор и цифровой фильтр. Наиболее широко в составе ИМС используются однобитные сигма-дельта модуляторы, в которых в качестве АЦП используется компаратор, а в качестве ЦАП - аналоговый коммутатор (рис. 12.6).

Рис.12.6. Структурная схема сигма-дельта АЦП

Для формирования выходного кода такого преобразователя необходимо каким-либо образом преобразовать последовательность бит на выходе компаратора в виде унитарного кода в последовательный или параллельный двоичный позиционный код. В простейшем случае это можно сделать с помощью двоичного счетчика. При использовании двоичного счетчика в качестве преобразователя потока битов, поступающих с выхода компаратора, необходимо выделять фиксированный цикл преобразования, длительность которого равна произведению Kсч fтакт. После его окончания должно производиться считывание результата, например, с помощью регистра-защелки и обнуление счетчика. В этом случае с точки зрения помехоподавляющих свойств сигма-дельта АЦП близки к АЦП многотактного интегрирования. Более эффективно с этой точки зрения применение в сигма-дельта АЦП цифровых фильтров с конечной длительностью переходных процессов.

Сравнение сигма-дельта АЦП с АЦП многотактного интегрирования показывает значительные преимущества первых. Прежде всего, линейность характеристики преобразования сигма-дельта АЦП выше, чем у АЦП многотактного интегрирования равной стоимости. Это объясняется тем, что интегратор сигма-дельта АЦП работает в значительно более узком динамическом диапазоне, и нелинейность переходной характеристики усилителя, на котором построен интегратор, сказывается значительно меньше. Емкость конденсатора интегратора у сигма-дельта АЦП значительно меньше (десятки пикофарад), так что этот конденсатор может быть изготовлен прямо на кристалле ИМС. Как следствие, сигма-дельта АЦП практически не имеет внешних элементов, что существенно сокращает площадь, занимаемую им на плате, и снижает уровень шумов.

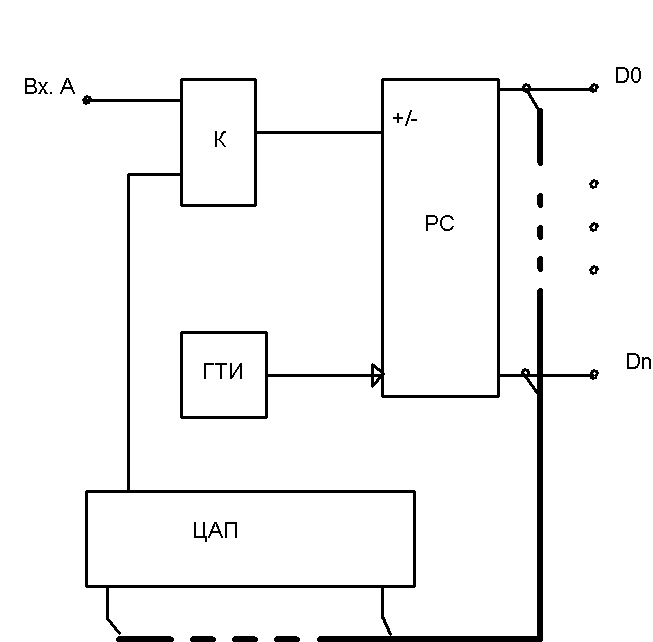

АЦП дифференциального кодирования (рис. 12.7) содержат реверсивный счётчик, код с которого поступает на вспомогательный ЦАП. Входной сигнал и сигнал со вспомогательного ЦАП сравниваются на компараторе. Благодаря отрицательной обратной связи с компаратора на счётчик код на счётчике постоянно меняется так, чтобы сигнал со вспомогательного ЦАП как можно меньше отличался от входного сигнала. По прошествии некоторого времени разница сигналов становится меньше, чем МЗР, при этом код счётчика считывается как выходной цифровой сигнал АЦП. АЦП этого типа имеют очень большой диапазон входного сигнала и высокое разрешение, но время преобразования зависит от входного сигнала, хотя и ограничено сверху. В худшем случае время преобразования равно Tmax=(2n)/fс, где n — разрядность АЦП, fс — частота генератора тактовых импульсов.

Рис. 12.7. АЦП дифференциального кодирования.

К- аналоговый компаратор, РС- реверсивный счетчик, ГТИ- генератор тактовых импульсов, ЦАП- цифро-аналоговый преобразователь.

АЦП дифференциального кодирования обычно являются хорошим выбором для оцифровки сигналов реального мира, так как большинство сигналов в физических системах не склонны к скачкообразным изменениям.

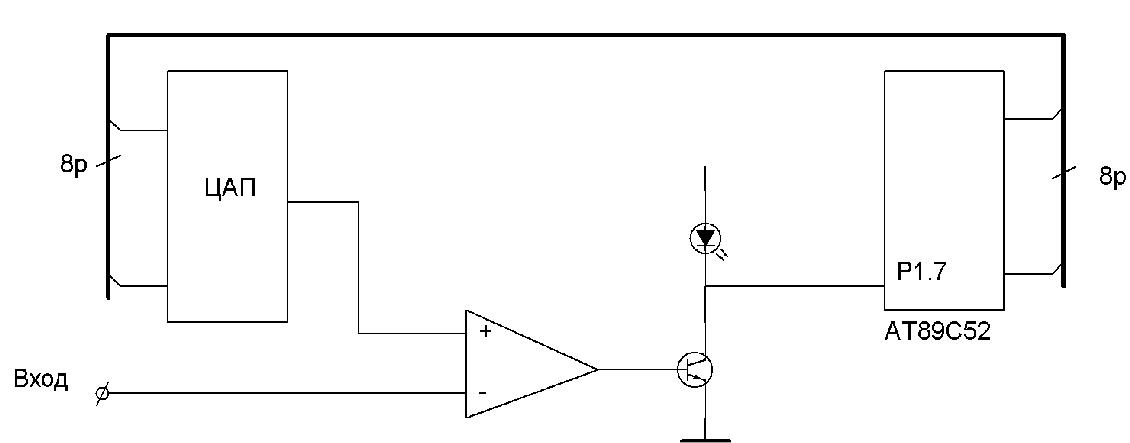

В составе учебно-отладочного стенда EV8031/AVR (V3.2) на плате расширения имеется 8-ми разрядный цифро-аналоговый преобразователь (ЦАП) с регистром, подключенный к микроконтроллеру ( внешний адрес ЦАП 0F000h). Выход ЦАП подключен к не инвертирующему входу компаратора, при этом на второй вход компаратора может подаваться напряжение от внешнего источника или встроенного источника в зависимости от положения перемычек. Выход компаратора подключен выводу Р1.7 микроконтроллера AT89C52. Упрощенная схема этой части стенда приведена на рис. 12.8.

Рис. 12.8. Упрощенная схема стенда для изучения аналого-цифрового преобразования

Используя стенд можно реализовать аналого-цифровые преобразователи (АЦП) следующих типов:

- АЦП дифференциального кодирования;

- АЦП последовательного приближения;

- сигма-дельта АЦП.

В настоящей работе изучаются первые два типа как наиболее часто используемые.

Рис. 12.9. Упрощенный алгоритм аналого-цифрового преобразования с использованием принципа дифференциального кодирования с последующей индикацией полученных результатов.

Упрощенные алгоритмы преобразования с использованием первого и второго методов приведены на рис. 12.9 и рис. 12.10 соответственно.

Алгоритм, приведенный на рис. 12.9 используется для преобразования в цифровой код медленно меняющихся аналоговых процессов. Алгоритм, приведенный на рис. 12.10 выполняет преобразование быстрее и в оптимальном случае требует для преобразования восьми итераций, каждая состоит из ~ двух машинных циклов плюс время задержки, необходимое для завершения переходных процессов в компараторе.

Рис. 12.10. Упрощенный алгоритм аналого-цифрового преобразования с использованием принципа последовательного приближения с последующей индикацией полученных результатов