- •6.050901 «Радіотехніка»

- •6.170102 «Системи технічного захисту інформації»

- •Изучение основных характеристик логических элементов основных типов

- •1. Методические указания к лабораторной работе

- •1.1. Исследование статических характеристик логических элементов

- •1.2. Исследование динамических характеристик логических элементов

- •2. Содержание отчета

- •3. Приложение

- •3.1. Описание учебно-лабораторного стенда “logic”

- •3.2. Описание микросхем, входящих в состав стенда и используемых для снятия переходной характеристики

- •3.3. Описание микросхем, используемых для снятия динамических характеристик

- •Двухвходового элемента и-не

- •Исследование базовых логических элементов и их комбинаций

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •Синтез комбинационных схем с одним выходом

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •3. Приложение.

- •3.1. Варианты заданий для выполнения лабораторной работы

- •Исследование триггеров

- •1. Методические указания к лабораторной работе

- •1.1. Исследование r-s триггеров

- •1.1.1. Исследование асинхронного r-s триггера

- •1.1.2. Исследование синхронного r-s триггера

- •1.1.3. Исследование r-s триггеров r, s и e типов

- •1.2. Исследование d-триггеров

- •1.2.1. Исследование d – триггера со статическим управлением

- •1.2.2. Исследование d – триггера с динамическим управлением

- •1.3. Исследование т-триггера

- •1.4. Исследование универсального j-k триггера

- •2. Содержание отчета

- •3. Приложение

- •Исследование двоичных счетчиков

- •1. Методические указания к лабораторной работе

- •1.1. Счетчики

- •1.2. Синтез синхронных счетчиков

- •1.2.1. Синтез цепей возбуждения

- •Матрица переходов j-k триггера

- •1.2.2. Синтез цепи переноса в следующие разряды

- •1.3. Динамические параметры счетчиков

- •2.Порядок выполнения работы

- •3. Отчет по работе.

- •Исследование регистров

- •1. Методические указания к лабораторной работе

- •1.1. Регистры

- •1.1.1. Регистры сдвига

- •1.1.2. Регистр сдвига на один разряд

- •1.1.3. Регистр сдвига на k разрядов

- •1.1.4. Реверсивные регистры сдвига

- •1.1.5. Параллельный ввод информации в регистрах сдвига

- •1.1.6. Регистры с обратными связями

- •1. 2. Проектирование многофункциональных регистров

- •1.3. Проектирование комбинационной схемы

- •1.4. Динамические параметры регистров

- •2. Порядок выполнения работы

- •3. Отчет по работе.

- •Состязания сигналов в цифровых схемах

- •1. Краткие теоретические сведения

- •2. Состязания в комбинационных схемах

- •2.1. Статические и динамические состязания сигналов

- •2.2. Синтез схем, свободных от статических состязаний

- •Статического состязания сигналов

- •2.3. Функциональные и логические состязания сигналов

- •На выходе схемы может появиться ложный импульс.

- •2.4. Синтез схем, свободных от логических состязании

- •2.5. Анализ комбинационных схем с целью выявления состязаний

- •3. Состязания сигналов в последовательностных схемах

- •4. Условия надежного функционирования асинхронной схемы

- •4.1. Критические состязания

- •4.2. Существенные состязания

- •5. Порядок выполнения работы

- •6. Отчет по работе должен содержать:

- •Изучение стенда, команд микроконтроллеров семейства mcs-51

- •1. Цель работы

- •2. Приборы и оборудование

- •3. Краткие теоретические сведения

- •3.1.Организация памяти и функционирование микроконтроллера

- •3.2. Запись исходного текста программы на языке программирования asm-51

- •3.3. Встроенные имена

- •3.4. Определяемые имена

- •3.5 Числа

- •3.6. Группа команд пересылки данных

- •3.7. Группа логических команд

- •3.8. Группа арифметических команд

- •3.9. Группа команд управления

- •3.10. Директивы ассемблера asm-51

- •4. Пример выполнения работы

- •5. Задание на выполнение работы.

- •6. Отчет по работе.

- •Изучение программирования встроенных таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •1.1. Режим 0

- •1.2. Режим 1

- •1.3. Режим 2

- •1.4. Режим 3

- •1.5. Управление таймерами-счётчиками.

- •1.7. Использование таймера в качестве частотомера.

- •2. Пример выполнения работы

- •1. Краткие теоретические сведения

- •1.1. Регистр приоритетов прерываний

- •1.2. Регистр разрешения прерываний

- •1.3. Начальные адреса прерываний

- •2. Задание на выполнение работы.

- •3. Отчет по работе.

- •Изучение способов программирования преобразования в двоично-десяичный код и программирования прерываний таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •Структура регистра ie

- •Адреса векторов прерывания

- •Регистр приоритетов прерываний

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

- •Изучение способов построения аналого-цифровых преобразователей с использованием микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

Статического состязания сигналов

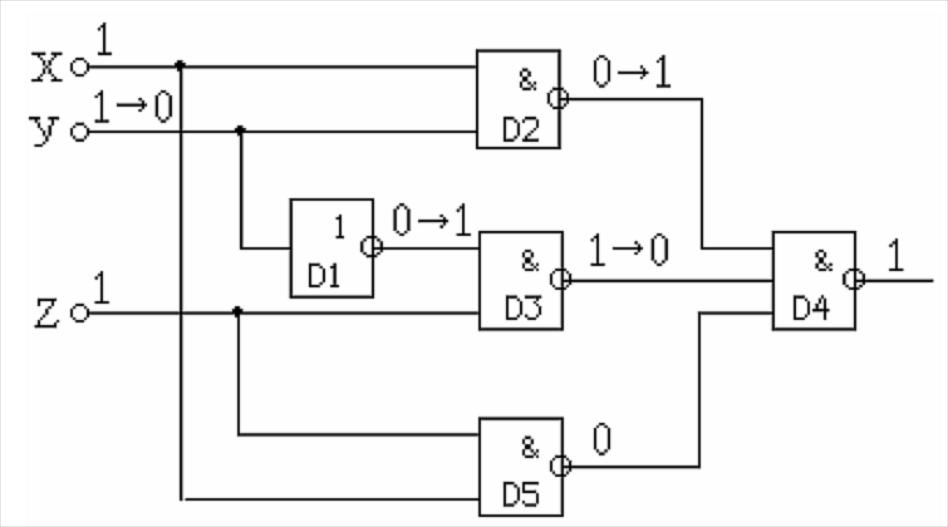

На рис. 7.5 этот дополнительный член в выражении для функции

f(X,Y,Z) = XY+YZ+XZ реализован элементом D5.

Рис. 7.5. Комбинационная схема, свободная от статически х состязаний сигналов

Во время изменения входного состояния неизменный сигнал нуля на выходе элемента D5 не позволяет переключаться элементу D4 и тем самым избавляет схему от кратковременного ложного сигнала на выходе.

2.3. Функциональные и логические состязания сигналов

Состязания в комбинационной схеме различают также в зависимости от количества входов, которые изменились при переходе от одного входного состояния в другое. Состязания, обусловленные одновременным изменением нескольких входных сигналов, отличаются от состязаний, возникающих при изменении одного входного сигнала, тем, что они не всегда могут быть устранены преобразованием выражения для функции. Если состязание возникает при одновременном изменении М входных сигналов, то в этом случае его называют М-состязанием.

Определение 3. Комбинационная схема содержит статическое М-состязание при одновременном изменении М входных сигналов, если:

выходной сигнал перед изменением равен выходному сигналу после изменения входного состояния;

во время переключения входных сигналов на выходе может появиться ложный импульс.

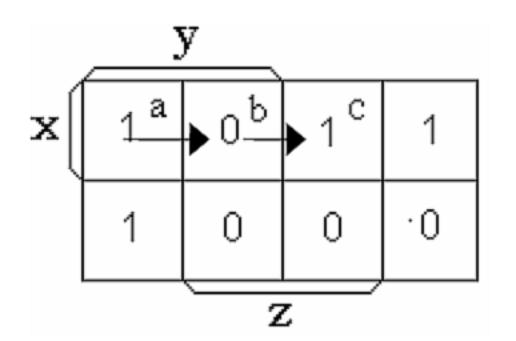

Существуют два различных типа статических М-состязаний. Первый тип, называемый функциональным состязанием, проиллюстрируем с помощью карты Карно, изображенной на рис. 7.6.

Допустим, входное состояние изменяется от X = 1, Y = 1, Z = 0 (состояние "а") к Х= 1, Y = 0, Z = 1 (состояние "с"). Если изменение переменной Z произойдет быстрее, чем изменение переменной Y, то временно наступит промежуточное состояние "b" (X= Y = Z = = 1). Так как на данном наборе функция равна 0 (см. рис. 7.6), то на выходе схемы может появиться нулевой ложный импульс.

Пусть переход из состояния входов А к входному состоянию В осуществляется изменением т переменных, т.е.

![]() где ai

представляет

собой значение 0 или 1 входной переменной

xi.

где ai

представляет

собой значение 0 или 1 входной переменной

xi.

Рис. 7.6. Иллюстрация функционального состязания

Определение 4. Комбинационная схема содержит функциональное состязание при переходе из А в В, если для булевой функции, которую реализует схема, справедливы два условия:

f(A)=f(B) и

существуют единичные и нулевые значения функции в 2т-клетках подкуба (am+1,… ,аn).

Очевидно, что если схема содержит функциональное состязание при переходе из А в B, то должен быть некоторый набор для изменяющихся переменных х1 . . ., хт для которого функция не равна f(A), f(B). Следовательно, существует возможность такого распределения задержек в схеме, при котором входные изменения достигают выхода в последовательности, вызывающей ложные импульсы. Данное состязание является внутренне присущим функции и не может быть устранено ее преобразованием, если допускается изменение входных сигналов в произвольном порядке.

Второй тип статических М-состязаний, называемый логическими состязаниями, похож на статические состязания в том, что оба типа состязаний могут быть устранены с помощью выбора подходящего выражения, используемого для построения схемы.

Определение 5. Комбинационная схема содержит логическое состязание при переходе из А в В, если справедливы следующие условия: