- •6.050901 «Радіотехніка»

- •6.170102 «Системи технічного захисту інформації»

- •Изучение основных характеристик логических элементов основных типов

- •1. Методические указания к лабораторной работе

- •1.1. Исследование статических характеристик логических элементов

- •1.2. Исследование динамических характеристик логических элементов

- •2. Содержание отчета

- •3. Приложение

- •3.1. Описание учебно-лабораторного стенда “logic”

- •3.2. Описание микросхем, входящих в состав стенда и используемых для снятия переходной характеристики

- •3.3. Описание микросхем, используемых для снятия динамических характеристик

- •Двухвходового элемента и-не

- •Исследование базовых логических элементов и их комбинаций

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •Синтез комбинационных схем с одним выходом

- •1. Методические указания к лабораторной работе

- •1.1. Исследование базовых логических элементов

- •2. Содержание отчета

- •3. Приложение.

- •3.1. Варианты заданий для выполнения лабораторной работы

- •Исследование триггеров

- •1. Методические указания к лабораторной работе

- •1.1. Исследование r-s триггеров

- •1.1.1. Исследование асинхронного r-s триггера

- •1.1.2. Исследование синхронного r-s триггера

- •1.1.3. Исследование r-s триггеров r, s и e типов

- •1.2. Исследование d-триггеров

- •1.2.1. Исследование d – триггера со статическим управлением

- •1.2.2. Исследование d – триггера с динамическим управлением

- •1.3. Исследование т-триггера

- •1.4. Исследование универсального j-k триггера

- •2. Содержание отчета

- •3. Приложение

- •Исследование двоичных счетчиков

- •1. Методические указания к лабораторной работе

- •1.1. Счетчики

- •1.2. Синтез синхронных счетчиков

- •1.2.1. Синтез цепей возбуждения

- •Матрица переходов j-k триггера

- •1.2.2. Синтез цепи переноса в следующие разряды

- •1.3. Динамические параметры счетчиков

- •2.Порядок выполнения работы

- •3. Отчет по работе.

- •Исследование регистров

- •1. Методические указания к лабораторной работе

- •1.1. Регистры

- •1.1.1. Регистры сдвига

- •1.1.2. Регистр сдвига на один разряд

- •1.1.3. Регистр сдвига на k разрядов

- •1.1.4. Реверсивные регистры сдвига

- •1.1.5. Параллельный ввод информации в регистрах сдвига

- •1.1.6. Регистры с обратными связями

- •1. 2. Проектирование многофункциональных регистров

- •1.3. Проектирование комбинационной схемы

- •1.4. Динамические параметры регистров

- •2. Порядок выполнения работы

- •3. Отчет по работе.

- •Состязания сигналов в цифровых схемах

- •1. Краткие теоретические сведения

- •2. Состязания в комбинационных схемах

- •2.1. Статические и динамические состязания сигналов

- •2.2. Синтез схем, свободных от статических состязаний

- •Статического состязания сигналов

- •2.3. Функциональные и логические состязания сигналов

- •На выходе схемы может появиться ложный импульс.

- •2.4. Синтез схем, свободных от логических состязании

- •2.5. Анализ комбинационных схем с целью выявления состязаний

- •3. Состязания сигналов в последовательностных схемах

- •4. Условия надежного функционирования асинхронной схемы

- •4.1. Критические состязания

- •4.2. Существенные состязания

- •5. Порядок выполнения работы

- •6. Отчет по работе должен содержать:

- •Изучение стенда, команд микроконтроллеров семейства mcs-51

- •1. Цель работы

- •2. Приборы и оборудование

- •3. Краткие теоретические сведения

- •3.1.Организация памяти и функционирование микроконтроллера

- •3.2. Запись исходного текста программы на языке программирования asm-51

- •3.3. Встроенные имена

- •3.4. Определяемые имена

- •3.5 Числа

- •3.6. Группа команд пересылки данных

- •3.7. Группа логических команд

- •3.8. Группа арифметических команд

- •3.9. Группа команд управления

- •3.10. Директивы ассемблера asm-51

- •4. Пример выполнения работы

- •5. Задание на выполнение работы.

- •6. Отчет по работе.

- •Изучение программирования встроенных таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •1.1. Режим 0

- •1.2. Режим 1

- •1.3. Режим 2

- •1.4. Режим 3

- •1.5. Управление таймерами-счётчиками.

- •1.7. Использование таймера в качестве частотомера.

- •2. Пример выполнения работы

- •1. Краткие теоретические сведения

- •1.1. Регистр приоритетов прерываний

- •1.2. Регистр разрешения прерываний

- •1.3. Начальные адреса прерываний

- •2. Задание на выполнение работы.

- •3. Отчет по работе.

- •Изучение способов программирования преобразования в двоично-десяичный код и программирования прерываний таймеров микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •Структура регистра ie

- •Адреса векторов прерывания

- •Регистр приоритетов прерываний

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

- •Изучение способов построения аналого-цифровых преобразователей с использованием микроконтроллера mcs-51

- •1. Краткие теоретические сведения

- •2. Пример выполнения работы

- •3. Задание на выполнение работы.

- •4. Отчет по работе.

2. Состязания в комбинационных схемах

2.1. Статические и динамические состязания сигналов

Состязания в комбинационных схемах классифицируют различным образом. В зависимости от характера переключения выходного сигнала схемы состязания подразделяют на статические и динамические.

Определение 1. Статическое состязание — это такое состязание сигналов, которое приводит к возможности кратковременного появления на выходе комбинационной схемы сигнала 0 (или1) при переходе от одного входного состояния в другое, каждое из которых формирует на выходе неизменный сигнал 1 (или 0).

Иногда состязания в комбинационной схеме называют риском. Если при переходе между парой входных состояний, формирующих на выходе схемы сигнал 1, возможно кратковременное появление на выходе сигнала 0, то говорят, что данный переход вызывает риск в единице (или статический 1-риск).

Если при переходе между парой входных состояний, формирующих на выходе схемы сигнал 0, возможно кратковременное появление на выходе сигнала 1, то говорят, что данный переход вызывает риск в нуле (или статический 0-риск).

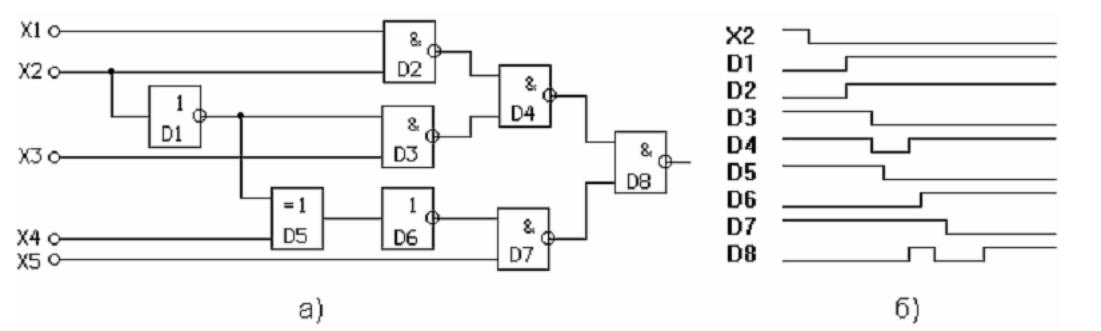

Пример риска в единице приведен на рис. 7.1.

Определение 2. Динамическое состязание — это такое состязание сигналов, которое приводит к возможности кратковременного появления на выходе комбинационной схемы сигнала 0 (или 1) при переходе от одного входного состояния в другое, первое из которых формирует на выходе сигнал 1 (0), а второе — сигнал 0 (1).

Переходный процесс, соответствующий динамическому состязанию сигналов в комбинационной схеме, приведен на рис. 7.3.

Рис. 7..3. Динамическое состязание сигналов в схеме

При переходе от входного набора X1 = X2 = ХЗ =Х4 = Х5 = 1 к набору X2 = 0, X1 = Х5 = Х4 = Х5 = 1 на выходе схемы произойдет многократное изменение сигнала, тогда как должно быть лишь одно изменение из 0 в 1.

Динамические состязания более редки, чем статические. При динамических состязаниях первое изменение выходного сигнала всегда совпадает с требуемым переключением, поэтому их влияние на поведение схемы в целом менее опасно. В дальнейшем будем рассматривать только статические состязания.

2.2. Синтез схем, свободных от статических состязаний

Комбинационная схема считается свободной от состязаний, если ее поведение не зависит от распределения задержек в цепях прохождения сигнала. Будем рассматривать только переходы между парами смежных входных состояний, которые формируют одно и то же значение выхода.

Два входных состояния являются смежными, если они отличаются значением только одной переменной.

Обычно процесс разработки комбинационных схем начинается с нахождения минимальной ДНФ (КНФ) функции. При синтезе схем без статических состязаний необходимо несколько изменить процедуру отыскания выражения для функции. Если используется карта Карно, то необходимо на ней выбирать покрытия таким образом, чтобы каждая пара смежных входных наборов, на которых функция равна 1 (или 0), входила хотя бы в одно покрытие.

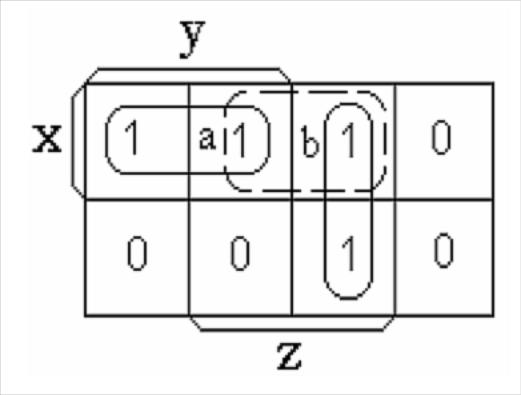

Рассмотрим функцию, занесенную на карту Карно (рис. 7.4). Минимальное выражение для этой функции:

![]()

Комбинационная схема, построенная на элементах И-НЕ по этому выражению, приведена на рис. 7.1(a). В минимальном выражении функции два смежных входных состояния, помеченных на диаграмме буквами а и b (см. рис. 7.4), не входят в одно покрытие. Переход между этими состояниями и был рассмотрен выше (см. рис. 7.1(б)). Покрытие этой пары смежных входных состояний произведением XZ устраняет условия статического состязания.

Рис. 7.4. Покрытие функции, необходимое для устранения