- •Введение

- •1. Омэвм avr семейства Mega

- •1.1. Технические характеристики микроконтроллера avr aTmega8515

- •1.2 Условное графическое обозначение (уго) микроконтроллера avr aTmega8515

- •1.3. Структура микроконтроллера аTmega8515

- •1.4. Организация памяти

- •1.4.1. Карта памяти

- •1.4.2. Память программ (Flash – пзу)

- •1.4.3. Память данных

- •Регистровая память (рон и рвв)

- •Файл регистров общего назначения

- •Регистр X, регистр y и регистр z

- •Регистр статуса – sreg

- •1.4.4. Оперативная память (озу или ram)

- •Регистр управления mcu - mcu Control Register - mcucr

- •1.4.5. Энергонезависимая память данных (eeprom)

- •1.5. Режимы адресации памяти данных

- •1.7. Стек. Указатель стека - Stack Pointer - sp

- •1.8. Тактирование. Режимы пониженного энергопотребления

- •1.8.1. Тактовый генератор

- •Система реального времени (rtc)

- •1.8.2. Сброс. Источники сброса

- •Сброс по включению питания

- •Внешнее управление сбросом

- •Сброс по сторожевому таймеру

- •1.8.3. Режимы энергосбережения (Sleep Modes)

- •1.9. Прерывания (interrupts)

- •Время отклика на прерывание

- •Обработка прерываний и сброса

- •Регистр флагов прерываний – gifr (General Interrupt Flag Register)

- •Регистр управления внешними прерываниями – gicr

- •Регистр масок прерывания по таймерам/счетчикам - timsk (Timer/Counter Interrupt Mask Register)

- •Регистр флагов прерываний по таймерам/счетчикам tifr

- •1.10. Таймеры/счетчики (timer/counters)

- •1.10.1. Таймер/счетчик t/c0

- •Регистр управления т/с0 - tccr0 (The Timer/Counter0 Control Register) Регистр tccr0 предназначен для управления модулем т/c0. Формат регистра tccr0:

- •Регистр сравнения выхода т/с0

- •Режимы работы т/с0

- •Изменение состояния ос0 определяется разрядами сом01:сом00 регистра tccr0 (состояние вывода ос0 изменяется в соответствии с таблицей 11).

- •1.10.2. Таймер/счетчик 1 – t/c1

- •1.11. Сторожевой таймер (Watchdog Timer)

- •Регистр управления сторожевым таймером – wdtcr

- •1.12. Универсальный синхронно-асинхронный приемопередатчик (usart)

- •Регистр данных usart - udr - (usart I/o Data Register)

- •Регистр ucsra

- •Регистр ucsrв

- •Регистр ucsrс

- •Формат кадра

- •Скорость обмена данными

- •Передача данных

- •Прием данных

- •1.13. Последовательный периферийный интерфейс spi

- •1.14. Аналоговый компаратор (Analog Comparator)

- •2. Система команд

- •Команды логических операций

- •Команды арифметических операций и сдвига

- •Команды операций с битами

- •Команды пересылки данных

- •Команды передачи управления

- •Теоретическая часть

- •1.1. Методические указания по выполнению лабораторной работы

- •1.1.1. Создайте новый проект.

- •1.1.2. Напишите и отладьте программу lab1

- •. Содержание отчета

- •3.2. Практическая работа №1 Изучение системы команд мк avr aTmega8515

- •2. Содержание отчета

- •3.3. Лабораторная работа №2 Изучение работы с портами ввода/вывода мк avr

- •Контрольные вопросы

- •Литература

Регистр сравнения выхода т/с0

OCR0 – (Timer/Counter0 Output Compare Register)

Регистр сравнения выходов является 8-разрядным регистром с возможностью чтения/записи. Регистр OCR0 расположен по адресу ($31($51)). Выполнение процедуры сравнения определяется регистром TCCR0. Совпадение при сравнении произойдет только тогда, когда таймер/счетчик досчитает до значения содержимого OCR. Программная запись одного и того же значения в таймер/счетчик и в регистр сравнения выхода не приведет к формированию совпадения при сравнении.

Совпадение при сравнении приведет к установке флага прерывания по совпадению в течение тактового цикла CPU следующего за совпадением.

Режимы работы т/с0

Normal – наиболее простой режим работы Т/С. В этом режиме счетный регистр функционирует как обычный суммирующий счетчик. По каждому тактовому импульсу осуществляется инкремент регистра. При переходе через значение $FF возникает переполнение и счет продолжается со значения $00. В том же такте тактового сигнала, в котором обнуляется счетный регистр, устанавливается в «1» флаг переполнения – TOV0.

При равенстве счетного регистра и регистра сравнения устанавливается в «1» флаг прерывания по событию «совпадение» – OCF0.

Наряду с установкой флага при равенстве счетного регистра и регистра сравнения может изменяться состояние вывода ОС0 МК. Изменение состояния ОС0 определяется разрядами СОМ01:СОМ00 регистра TCCR0.

Таблица 13. Состояние вывода ОС0 МК

-

СОМ01

СОМ00

Описание состояния вывода ОС0

0

0

T/C отключен от вывода ОС0.

0

1

Состояние вывода изменяется на противоположное.

1

0

Вывод ОС0 сбрасывается в 0.

1

1

Вывод ОС0 устанавливается в1.

СТС (сброс при совпадении) – счетный регистр функционирует как обычный суммирующий счетчик, инкремент которого осуществляется по каждому импульсу тактового сигнала. Максимально возможное значение счетного регистра и разрешающая способность счетчика определяется регистром сравнения ОCR0. После достижения значения, записанного в регистре сравнения, счет продолжается со значения $00. В том же такте устанавливается флаг OCF0.

Изменение состояния ос0 определяется разрядами сом01:сом00 регистра tccr0 (состояние вывода ос0 изменяется в соответствии с таблицей 11).

Fast PWM (быстродействующая ШИМ) – в этом режиме генерируются сигналы с широтно-импульсной модуляцией. Режим используется в регулировании мощности, выпрямлении и др. Счетный регистр функционирует как суммирующий счетчик, инкрементирующий состояние по каждому тактовому импульсу. Состояние счетчика изменяется от $00 до $FF, после чего сбрасывается и цикл повторяется.

Особенностью схемы сравнения в этом режиме является двойная буферизация записи в регистр ОCR0 – записываемое число сохраняется в специальном буферном регистре. Изменение содержимого регистра сравнения происходит только в момент достижения счетчиком максимального значения $FF. Это исключает появление несимметричных импульсов сигнала на выходе модулятора (помех), которые были бы неизбежны при непосредственной записи в регистр сравнения. Изменение состояния ОС0 определяется разрядами СОМ01:СОМ00 регистра TCCR0:

Таблица 14. Состояние вывода ОС0 МК

СОМ01 |

СОМ00 |

Описание состояния вывода ОС0 |

0 |

0 |

T/C отключен от вывода ОС0. |

0 |

1 |

Зарезервировано. |

1 |

0 |

Вывод ОС0 сбрасывается в 0 при равенстве счетного регистра и регистра сравнения. Устанавливается в 1 при обнулении счетного регистра. |

1 |

1 |

Вывод ОС0 устанавливается в1 при равенстве счетного регистра и регистра сравнения. Сбрасывается в 0 при обнулении счетного регистра. |

Phase correct PWM (ШИМ с точной фазой) – также используется для генерации сигналов с широтно-импульсной модуляцией. В этом режиме счетный регистр изменяет состояние по импульсу тактового сигнала от $00 до $FF, а затем обратно от $FF до $00. Максимальная частота тактового сигнала в этом режиме в 2 раза меньше максимальной частоты в режиме Fast PWM. Этот режим предпочтительнее использовать при решении задач управления двигателем. Изменение состояния ОС0 определяется разрядами СОМ01:СОМ00 регистра TCCR0:

Таблица 15. Состояние вывода ОС0 МК

СОМ01 |

СОМ00 |

Описание состояния вывода ОС0 |

0 |

0 |

T/C отключен от вывода ОС0. |

0 |

1 |

Зарезервировано. |

1 |

0 |

Вывод ОС0 сбрасывается в 0 при прямом счете. Устанавливается в 1 при обратном счете. (Вывод ОС0 изменяет состояние, если регистр сравнения равен регистру счета). |

1 |

1 |

Вывод ОС0 устанавливается в1 при прямом счете. Сбрасывается в 0 при обратном счете. (Вывод ОС0 изменяет состояние, если регистр сравнения равен регистру счета). |

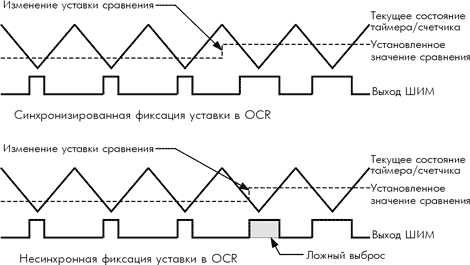

В ШИМ режиме при записи содержимое регистра сравнения выхода пересылается на временное хранение. Содержимое фиксируется при достижении таймером/счетчиком состояния $FF. Такой прием предохраняет от появления ШИМ импульсов увеличенной ширины (ложных выбросов) в случае несинхронной записи OCR0 или OCR2. Пример (для состояния СОМ01: СОМ00=1:0) см. на рис.21.

Рис. 21. Эффект несинхронной фиксации OCR