- •1 Введение

- •2 Основная часть

- •Раздел 1 архитектура и принципы построения эвм

- •Тема 1.1 Основные характеристики эвм

- •Тема 1.2 Общие принципы построения микро эвм

- •1) Протоколы обмена информации

- •2) Протоколы арбитража

- •3) Параллельная и последовательная передачи

- •4) Временная синхронизация процессов в микро эвм.

- •5) Режимы работы микро эвм

- •6) Формирование системной шины микро эвм.

- •Тема 1.3 Классификация средств вт

- •4 Микро эвм (пэвм).

- •Раздел 2. Функциональная и структурная организация эвм

- •Тема 2.1 Внутренняя структура эвм

- •1) Структурная схема эвм. Назначение базовых узлов и их функции.

- •Тема 2.2 Арифметическое логическое устройство (алу)

- •1) Формы представления информации в эвм

- •2) Представление алфавитно-цифровой информации и десятичных чисел

- •1 Классификация алу

- •2 Структура алу

- •Тема 2.3 Центральный процессор (цп)

- •2) Организация работы цп и оп

- •3) Система команд.

- •4) Программы и микропрограммное управления.

- •Тема 2.4 Устройство управления (уу)

- •2) Структурная схема уу

- •3) Способы адресации.

- •1. Прямая адресация.

- •4. Укороченная адресация.

- •4) Принцип организации системы прерываний

- •2. Характеристики системы прерываний

- •6) Маска прерываний

- •5) Прямой доступ к памяти

- •6) Интерфейс системной шины

- •Тема 2.5 Системная память

- •1) Иерархическая организация памяти в эвм.

- •2) Оперативная память

- •5) Основная память

- •6) Виртуальная память

- •1 Основные понятия

- •2 Виртуальная память при страничной организации.

- •3 Виртуальная память при сегментно-страничной организации.

- •7) Постоянная память для хранения bios

- •8) Защита памяти

- •Раздел 3 современные микро эвм

- •Тема 3.1 Технология сверхбыстрых ис и их влияние на архитектуру эвм

- •1) Архитектура эвм Фон-Неймана.

- •2 Раздельное кэширование кода и данных.

- •3 Введение блока предсказания перехода

- •2) Мп и микро эвм

- •3) Структура микро эвм

- •4) Особенности реализации оп в современных микро эвм

- •5) Периферийная организация эвм.

- •6) Мультипроцессорные системы

- •7) Системные ресурсы компьютера

- •Тема 3.2 Многопроцессорные и многомашинные вычислительные системы.

- •1) Общие сведения

- •2) Классификация вс

- •Тема 3.3 Архитектура памяти

- •1) Проблемы короткого машинного слова и архитектурные методы решения этих проблем.

- •2) Архитектура памяти (См. Раздел 2)

- •3) Форматы команд (См. Раздел 3)

- •Тема 3.4 Организация ввода/вывода и системы прерываний

- •1) Пространство ввода/вывода

- •2) Программное управление вводом/выводом

- •3) Ввод/вывод по прерываниям

- •4) Организация пдп

- •Раздел 4. Базовая архитектура 32 разрядных мп на примере i486

- •Тема 4.1 Регистровая структура мп

- •1) Пользовательские регистры мп (16 штук)

- •2) Сегментные регистры

- •3) Указатель команды eip/ip

- •4) Регистр флагов

- •Системные регистры мп i486 (15 штук)

- •1 Регистры pm

- •2 Регистры управления cr0 - cr3

- •3 Регистры отладки dr0 – dr7 – (Debug Registers)

- •4 Регистры проверки tr3-tr5, tr6, tr7.

- •Тема 4.2 Кодирование режимов адресации

- •1) 16 Битная адресация

- •2) 32 Битная адресация – применяется в защищённом режиме

- •Тема 4.3 Управление памятью

- •1 Сегментная организация памяти.

- •1) Общие понятия о сегментации.

- •2) Формат дескриптора сегмента

- •3) Права доступа сегмента ar

- •4) Дескрипторные таблицы

- •5) Селекторы сегментов

- •6) Образование линейного адреса

- •7) Локальная дескрипторная таблица (ldt)

- •8) Особенности сегментации

- •2) Страничная организация памяти

- •1 Структура страниц (лист 7)

- •2 Страничное преобразование адреса.

- •3 Формат элемента таблицы страниц pte

- •Тема 4.4 Защита по привилегиям

- •1) Уровни привилегий

- •2) Определение уровней привилегий

- •3) Привилегированные команды

- •4) Защита доступа к данным

7) Системные ресурсы компьютера

Обмен информацией между различными устройствами компьютера осуществляется под управлением BIOS и соответствующих драйверов уст-

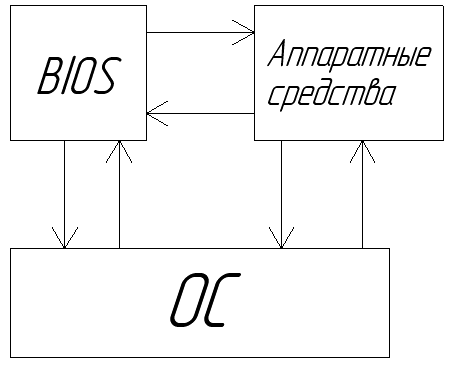

ройств с использованием системных ресурсов: а) Линий запросов прерываний IRQi; б) Каналов ПДП (DMAi); в) Базовых адресов портов ввода вывода в общем диапазоне 000-3FFh; г) Физической памяти, установленной в слоты MB. Каждому из устройств, установленных в ПК, присваивается уникальное значение этих параметров, и никакое другое устройство не должно их использовать. Например, флоппи дисковод имеет IRQ6, DMA2, Адреса 3F0-3F7. Неправильное использование этих ресурсов ведёт к конфликту оборудования, в результате которого система будет работать непредсказуемо или неправильно. Конфликты устраняются путём грамотной настройки программно-аппаратных средств, называемой конфигурированием. Настройка производится BIOS Setup. Современные ПЗУ BIOS поддерживают стандарт автоматической настройки Plug & Play, который разработан фирмой Intel и позволяет системам и адаптерам автоматически настроить друг друга. Для этого в BIOS включены специальные 13 системных функций. В реализации стандарта Plug & Play принимает участие аппаратные средства, BIOS и ОС

Рисунок 23 – Реализация Plug & Play

Аппаратные средства информируют BIOS и ОС о необходимых ресурсах и в свою очередь самонастраиваются на основании полученной информации. BIOS распознаёт установленные устройства из программы POST, анализирует распределение ресурсов и настраивает адаптеры Plug & Play. Этот режим поддерживают все Windows, начиная Win95, Unix, Linux, OS/2.

Тема 3.2 Многопроцессорные и многомашинные вычислительные системы.

1) Общие сведения

Вычислительная система (ВС) – это сложный комплекс, состоящий из разнообразных технических средств, и соответствующего ПО. Технические и программные средства имеют модульную структуру, позволяющую ремон-

тировать или наращивать её в зависимости от назначения и условий эксплуатации ВС. Первые ВС были однопроцессорными, но имели мультипрограммное управление, то есть основные устройства систем распределялись во времени между отдельными программами. Далее стали применять мультиобработку программ, то есть программа развивалась на отдельные блоки, которые параллельно обрабатывались на несколько устройствах, входящих в ВС. В вычислительную систему могли объединяться различные ЭВМ с классической структурой, либо несколько МП.

2) Классификация вс

а) По назначению: универсальные, решающие широкий круг задач; специализированный – для определённого круга задач.

б) По типу оборудования: однородные (однотипные ЭВМ или МП) – (-) Неполная загруженность; Неоднородные (разнотипные ЭВМ и процессоры) – в них центральная ЭВМ более производительная, выполняющая основную обработку, а ввод/вывод осуществляет менее производительная ЭВМ.

в) По типу структуры:

- с постоянной структурой

- с переменной структурой (адаптивная), где структура изменяется на основе анализа текущей информации.

г) По степени централизации управления ВС

- централизованные, где все функции управления выполняет ЦП

- децентрализованные, где каждый процессор или ЭВМ работает автономно.

- смешанное управление, где ВС разбивается на группы ЭВМ или процессоров, в каждой из которых- централизованное управление, а между группами- децентрализованное.

д) По типу организации

- не связанные ВС. Состоят из центральной и периферийной ЭВМ, между которыми нет прямого физического соединения. Операции ввода/вывода и вычисления совмещаются во времени.

- связанные, где несколько ЭВМ совместно используют общие аппаратные средства.

3) Архитектура ВС.

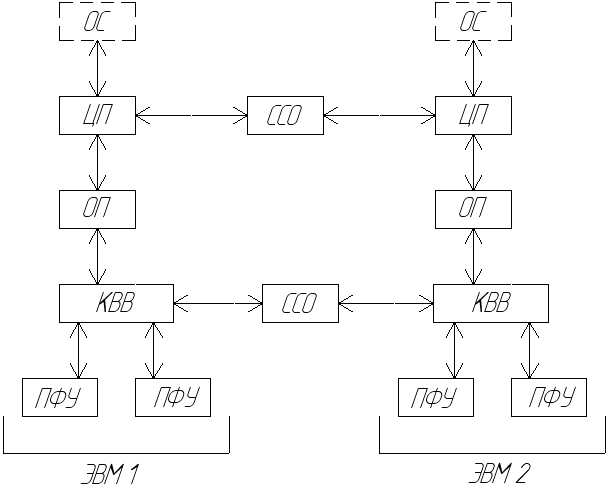

1 Двухмашинная ВС

Рисунок 24 - Двухмашинная ВС

Это универсальная однородная с постоянной структурой, децентрализованная, связанная ВС.

Каждая ЭВМ имеет ОП, ВЗУ, ПФУ, подключённых к ЦП с помощью КВВ и работает каждая под управлением ОС. ССО – это системные средства обмена, через которые идёт обмен информацией между ЭВМ1 и ЭВМ2 в результате взаимодействия ОС обеих ЭВМ.

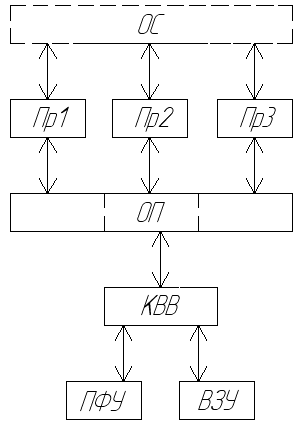

2 Многопроцессорная ВС с мультиобработкой

Рисунок 25 - Многопроцессорная ВС с мультиобработкой

Единая ОС автоматически распределяет ресурсы системы между процессорами, что ведёт к долговечности системы. Недостаток: трудности в разработке единой ОС.

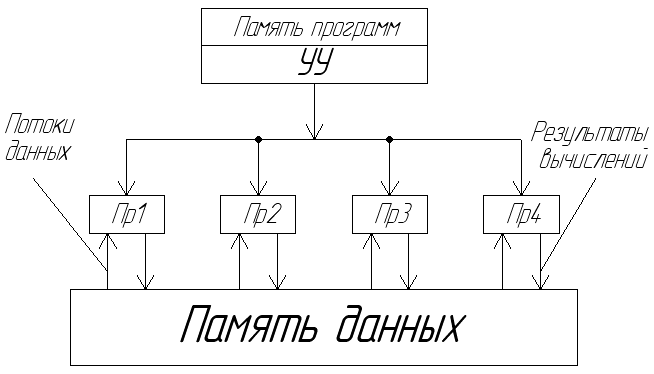

3 Высокопараллельные ВС

а) Высокопараллельные ВС типа ОКМД

Одиночный поток команд – множественный поток данных

Рисунок – 26 Высокопараллельные ВС типа ОКМД

Процессор 1-4 соединены так, что создают сетку (матрицу). Все процессоры выполняют одну и ту же команду, но над разными операндами, доставленными из памяти несколькими потоками данных.

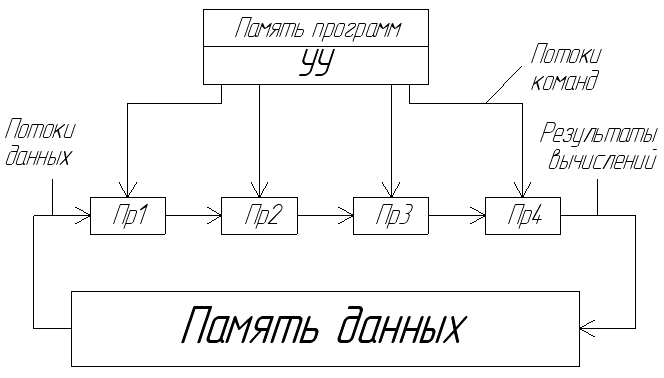

б) Конвейерные ВС типа МКОД

Множественный поток команд, одиночный – данных

Рисунок 27 - Конвейерные ВС типа МКОД

Процессоры 1-4 соединены последовательно так, что информация на выходе одного процессора является входной для другого. Каждый процессор обрабатывает соответствующую часть задачи, передавая результаты соседнему процессору и так далее. Например, сложение чисел с ПЗ: 4 этапа: 1) сравнение порядков; 2) выравнивание порядков; 3) сложение мантисс; 4) нормализация результата. (+): высокое быстродействие; (-): Трудность программирования, малая загрузка системы, дорогие системы. Поэтому применяются как специализированные.