- •2. Теоретические сведения

- •2.1 Основные сведения о логических элементах

- •2.2 Общие сведения об устройствах для обработки информации

- •2.2.1 Компараторы и триггеры Шмита

- •2.3 Практические схемы логических элементов и цифровые микросхемы

- •2.3.1 Цифровые микросхемы на ттл - элементах

- •2.3.2 Программируемые устройства. Микропроцессоры

- •3. Экспериментальная часть

- •3.1 Оборудование рабочего места

ЛАБОРАТОРНАЯ РАБОТА №6

Изучение основ цифровой техники

1. Цель работы: ознакомиться с основными характеристиками простейших логических элементов, микросхем, которые вместе с запоминающими элементами составляют основу устройств цифровой (дискретной) техники обработки информации.

2. Теоретические сведения

2.1 Основные сведения о логических элементах

Логические элементы в отличие от аналоговых устройств (усилителей и др.) допускают в качестве значений входных и выходных напряжений лишь два уровня: «высокий» — «1» и «низкий» — «О». В транзисторно-транзиторной логике (ТТЛ) напряжение логическое «0» U0 составляет десятые доли вольт, и напряжение логической «1»U1≥2,4 В. Логические элементы реализуют простейшие функции или систему функций алгебры логики.

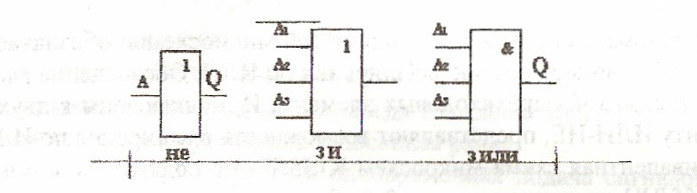

Будем обозначать входные величины буквой А, а выходные — Q. Простейшие функции алгебры логики: НЕ, ИЛИ, И. Логическая операция преобразует по определённым правилам входную информацию в выходную. Логические преобразования двоичных сигналов включают три элементарных операции:

1. Логическое сложение (дизъюнкцию), или операцию ИЛИ, обозначаемую знаками «+» или V : F=х1+х2+х3+ ... + х n

2. Логическое умножение (конъюнкцию), или операцию И, обозначаемую знаками «*» или, А: F= х1*х2*хз* ... * хn;.

З. Логическое отрицание (инверсию), или оператор НЕ: F = ˉx

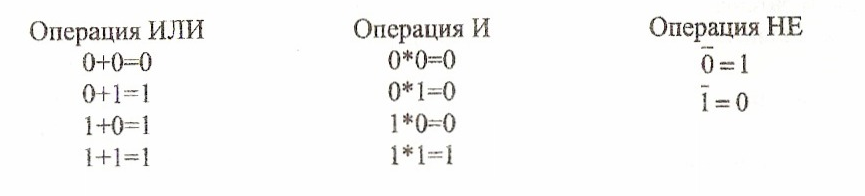

Правила выполнения логических операций над двоичными переменными для случаев двух переменных имеют вид:

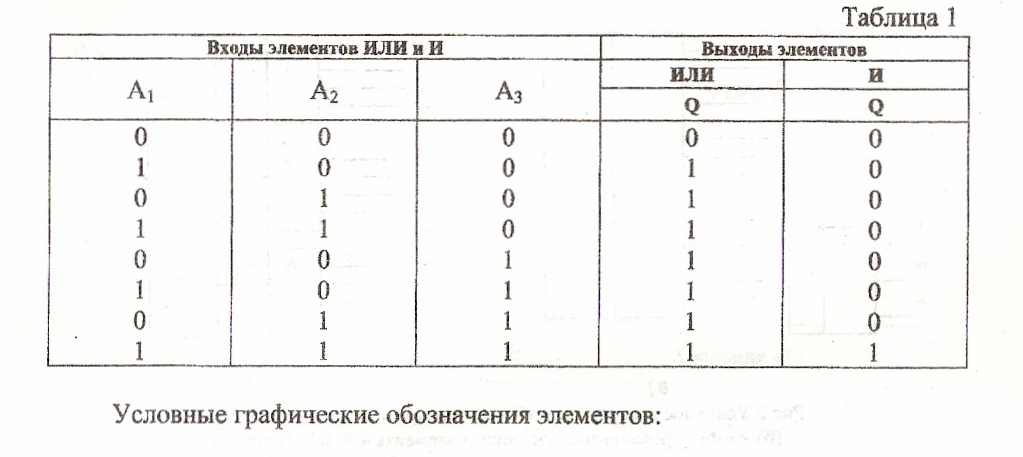

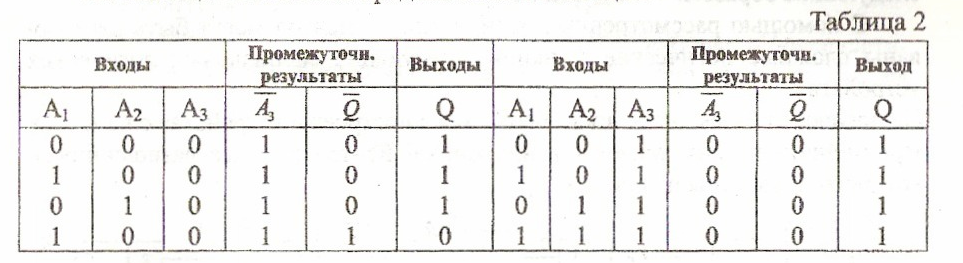

Таблицы истинности для этих элементов однозначно связывают значение выходной величины Q со значениями трёх (или более) входных величин А1, А2, А3, ... (табл. 1).

Аналогично производиться анализ (соответственные таблицы истинности) и более сложных логических схем, например ИЛИ — НЕ элемент Пирса, И — НЕ — элемент Шеффилда.

Однако на практике в одной микросхеме встречаются комбинации различных элементов, что позволяет с меньшими затратами реализовать часто встречающиеся логические функции.

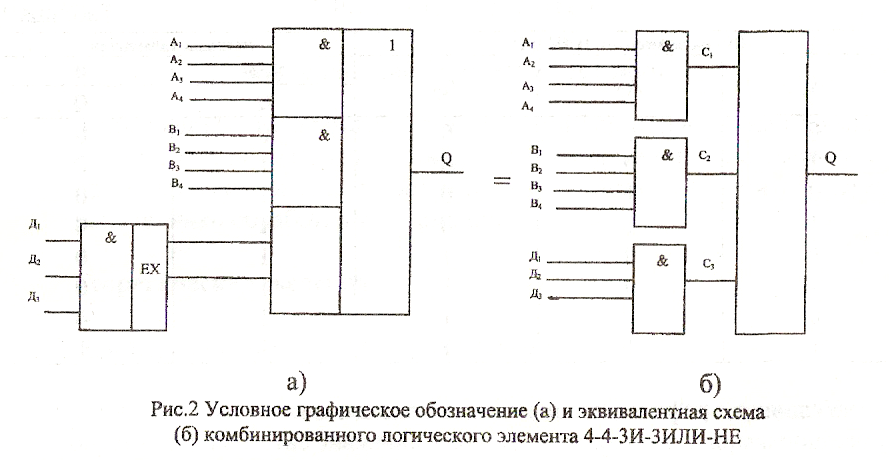

На рис. 1 приведено условное графическое обозначение микросхемы К155ЛР-4, состоящей из двух элементов И (каждый с четырьмя входами), подключенных выходами к элементу ИЛИ - НЕ, и добавочных двух входов ЕХ, к которым может подключаться только специальная микросхема, так называемый четырёхвходовый расширитель по ИЛИ (микросхема К1555Лд1).

36

36

Микросхема в соответствии с принятой мнемосхемой обозначается 4-4- ЗИ-ЗИЛИ-НЕ с возможностью расширения по ИЛИ. Обозначение расшифровывается так: два четырёхвходовых элемента И, подключены к двухвходному элементу ИЛИ-НЕ, представляют возможность расширения по ИЛИ (вход ЕХ). Эквивалентная схема микросхем КI55ЛР-4 с подключённым расширителем К 155ЛД 1 приведена на рис 2 6. Для этой схемы мнемоника выглядит следующим образом: 4-4-ЗИ-ЗИЛИ-НЕ.

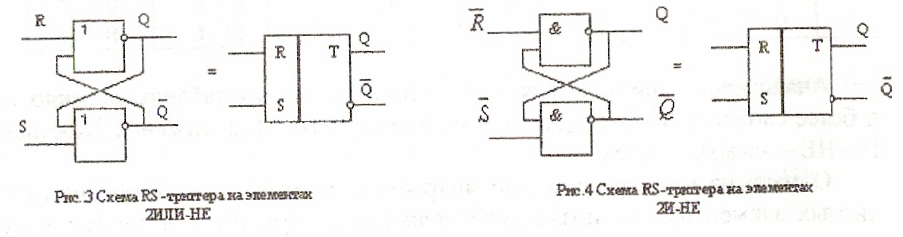

С помощью рассмотренных логических элементов могут быть реализованы сложные логические функции, требующие специальных логических устройств. На логических элементах могут быть также построены устройства с памятью. Простейшим из них является асинхронный Р.S-триггер, две разновидности которого приведены на рис.3,4.

Триггер на элементах ИЛИ-НЕ (рис.3) имеет прямые входы R и S, триггер на элементах И-НЕ (рис.4) . инверсные входы R и S и два выхода: прямой Q и инверсный Q. Таблица истинности для RS — триггера (табл.3) составлена для перебора строк в порядке возрастания номеров При изменении порядка перебора строк таблица может существенно измениться.

Как видно из таблицы З, при R=1, S=0 (R=0,S= 1) триггер устанавливается в состояние «0» (Q = 0,Q = 1), при R = 0, S = 1 — в состояние «1». Поэтому вход R называется входом установки нуля, а вход S— Входом установки единицы. Отсутствие входных сигналов (R= 0, S = 0, R = 1,S = 1) обеспечивает режим хранения информации, когда состояние триггера остаётся без изменения и хранится информация, записанная ранее.

Для асинхронного RS триггера одновременная подача сигналов на два входа запрещена и состояние триггера становиться непредсказуемым.

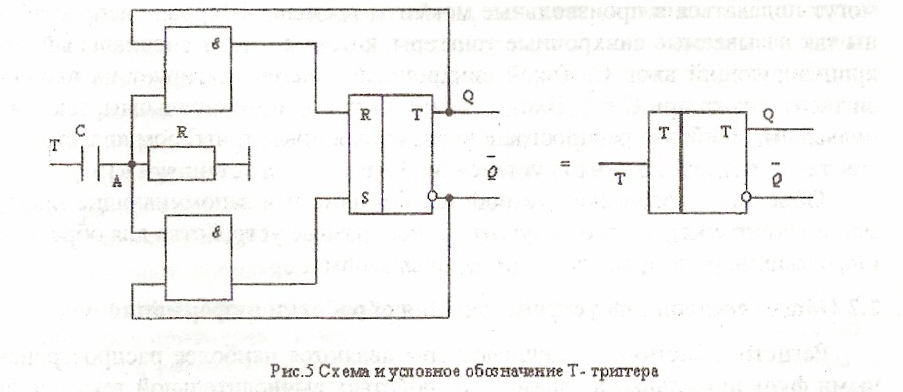

Простейший RS триггер легко может быть преобразован в более сложный Т-триггер. Схема и условное обозначение Т триггера показаны на рис.5.

Здесь входной сигнал через дифференцирующую RС-цепь подается на вход двух элементов И, управляющих входными сигналами R и S RS- триггера. В зависимости от текущего состояния RS-триггера сигнал поступает на один вход: R или S. Подача входных сигналов ( и осуществляется так, что входной сигнал всякий раз осуществляет переключение RSтриггера.

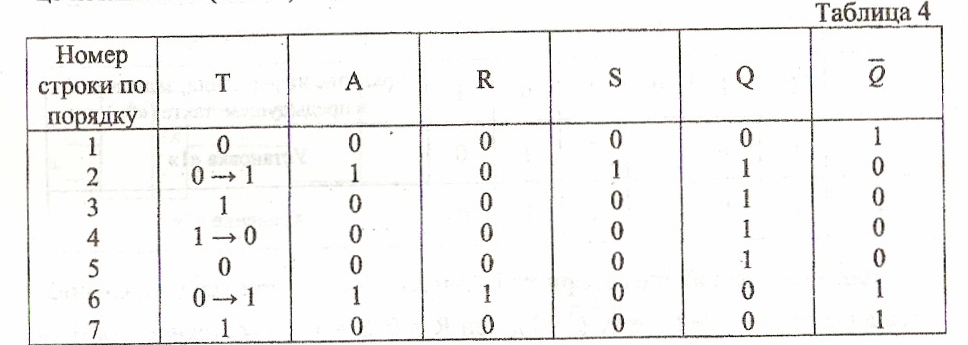

Для предотвращения повторного переключения триггера при изменении его входных сигналов ( и длительность входного сигнала ограничивается дифференцирующей RС-цепью. Логика работы Т-триггера показана в таблице истинности (табл.4)

Таблица 4

Именно при переходе входной величины Т из состояния «0» в состояния «1» в течение короткого времени (5 — 20 мс) А = 1 и триггер изменяет своё состояние. Во всех остальных режимах А = О и состояние триггера неизменно.

В обозначении триггера на рис.5 учтено, что он реагирует на положительный перепад входной величины. Такой вход носит название динамического или импульсного.

На практике в Т-триггере обычно присутствуют и входы R, S для установки в состояние «0» и «1», т.е. получается RSТ-триггер.

Рассмотренные триггеры являются асинхронными, т.е. входные сигналы могут подаваться в произвольные моменты времени. Широко распространены так называемые синхронные триггеры, которые имеют специальный синхронизирующий вход С. Такой синхронный триггер реагирует на входные сигналы только при С = 1. Вход С может быть как потенциальным, так и импульсным. Наиболее распространённым синхронным триггером является JK-триггер, у которого К — вход установки «0» и J—вход установки «1».

Объединяя логические устройства без памяти и запоминающие информацию (триггеры), можно получить разнообразные устройства для обработки информации: регистры, счётчики, дешифраторы и др.