- •1. Структура многоуровневой системы управления. Решаемые задачи и требования к системе.

- •2. Структура и устройства управляющей микропроцессорной системы. Способы аналоговой обработки данных.

- •4. Схемы сопряжения устройств озу, пзу и портов ввода/вывода с шинами системной магистрали. Управление доступом к устройствам мп-системы:

- •5. Применение дешифраторов, ппзу и плм в схемах выборки устройств мп-системы.

- •6. Структура и интерфейс 8-разрядного микропроцессора.

- •7. Цикл выполнения команды 8-разрядного микропроцессора.

- •8. Диаграмма машинного цикла 8-разрядного микропроцессора. Типы машинных циклов, используемых при выполнении команд. Диаграмма цикла микроконтроллера mcs-51.

- •9. Системный контроллер мп – системы и системные сигналы управления.

- •10. Программистские модели 8-разрядных микропроцессоров (ресурсы, способы представления данных и виды адресации, слово состояния программы). Работа со стеком.

- •11. Структура и интерфейс микроконтроллеров с архитектурой cisc (на примере mcs-51).

- •12. Логическая организация памяти микроконтроллера mcs-51.

- •13. Характеристика системы команд микроконтроллера мcs-51. Слово состояния программы, типы данных, способы адресации. Организация ветвлений в программах.

- •15. Операции умножения/деления двоичных чисел.

- •Программная процедура деления:

- •16. Арифметическая обработка многобайтных операндов в микропроцессорах и микроконтроллерах с 8 – разрядной архитектурой.

- •17. Сложение-вычитание многобайтных 2-10 чисел в 8-разрядных микропроцессорах и микроконтроллерах.

- •19. Программная реализация временной задержки с заданным временем (задача). Расчетные зависимости.

- •18. Логическая обработка данных в микроконтроллерах. Битовые операции. Вычисление логической функции, аргументы которой поступают по входным линиям порта (задача).

- •20. Принципы организации ввода-вывода данных в микропроцессорных системах.

- •21. Порты параллельного синхронного ввода-вывода мп систем. Программирование ввода-вывода.

- •22. Схемы портов параллельного асинхронного ввода-вывода мп – систем.

- •23. Структурная схема параллельного программируемого интерфейса. Основные режимы работы.

- •24. Организация ввода-вывода данных по запросам прерываний от схемы программируемого параллельного интерфейса.

- •25. Схемы и принципы работы двунаправленного (p0) и квазидвунаправленных портов (p1, p2, p3) микроконтроллеров mcs-51.

- •26. Режимы работы портов ввода-вывода микроконтроллеров avr.

- •27. Параллельный обмен данными с внешними устройствами в микроконтроллерных системах. Обмен с квитированием.

- •28. Схема, основные режимы работы и программирование таймера микроконтроллера mcs51.

- •29. Применение таймеров mcs51 для отсчета времени, измерения длительности сигнала, подсчета событий, формирования периодических сигналов.

- •1. Подсчет числа импульсов, поступающих на вход мк51 за 10мс.

- •2. Измерение длительности сигнала, поступающего на вход .

- •3. Организовать временную задержку длительность 500мс

- •4. Формирование пер. Сиг. (100мкс

- •30. Таймеры микроконтроллеров avr. Использование таймеров для сравнения, захвата событий, формирования шим-сигналов, в сторожевом режиме.

- •31. Основные функции системы прерываний.

- •32. Способы программной и аппаратной идентификация запроса прерываний в одноуровневых и многоуровневых системах прерываний.

- •33. Механизм обработки векторных прерываний в мп-системах с помощью команд rst n и call addr.

- •34. Контроллер прерываний. Структура, интерфейс, способы обработки прерываний.

- •35. Построение системы прерываний с несколькими контроллерами. Идентификация запроса прерываний.

- •36. Программирование контроллера прерываний. Назначение управляющих слов при инициализации контроллера и во время работы.

- •37. Система прерываний микроконтроллера mcs51. Работа со стеком.

- •38. Структура и основные режимы работы канала последовательного ввода-вывода uart микроконтроллера mcs-51.

- •39. Программирование приёма/передачи данных по каналу uart между двумя микроконтроллерами.

- •40. Организация обмена данными между микроконтроллерами при работе в сети.

- •41. Схема интерфейса микроконтроллера mcs-51 с внешней памятью программ, внешней памятью данных и дополнительными портами ввода-вывода.

- •42. Типовой цикл работы микроконтроллера mcs-51. Примеры выполнения команд 1-байтовых, 2-байтовых, с обращением к внешней памяти данных.

- •43. Применение ацп и цап в мп-системах.

- •44. Устройства энергонезависимой памяти с последовательным интерфейсом (на примере at25, at45).

- •45. Память DataFlash -структура, операции, применение.

- •47. Организация адресного пространства микроконтроллеров avr, способы адресации памяти программ и памяти данных.

- •48. Интерфейсы последовательной связи spi.

- •Интерфейс spi.

- •Схемотехника spi:

- •Использование spi в приложениях

- •49. Интерфейсы последовательной связи i2c. Программная и аппаратная реализация в микроконтроллерах avr.

- •Схемотехника i2c

- •50. Системы на кристалле.

- •Структурная схема Triscend es:

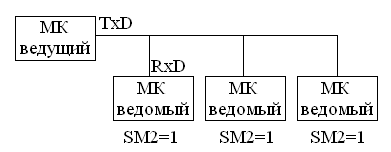

40. Организация обмена данными между микроконтроллерами при работе в сети.

Используется широковещательный 11-битовый формат с ТВ8=1.

Пусть ведущему МК требуется передать блок данных некоторому (или нескольким) ведомому МК. С этой целью ведущий МК в протокольном режиме "широковещательной" передачи (всем ведомым МК) выдает в моноканал байт-идентификатор абонента (код адреса МК-получателя), который отличается от байтов данных только тем, что в его девятом бите содержится 1 (TB8 = 1 – широковещательный кадр). Программа реализации протокола сетевого обмена информацией должна быть построена таким образом, чтобы при получении байта-идентификатора (RB8 = 1) во всех ведомых МК произошли прерывание прикладных программ и вызов подпрограммы сравнения байта-идентификатора с кодом собственного сетевого адреса. Адресуемый МК сбрасывает свой управляющий бит SM2 и готовится к приему блока данных. Остальные ведомые МК, адрес которых не совпал с кодом байта-идентификатора, оставляют неизменным состояние SM2 = 1 и передают управление основной программе. При SM2 = 1 информационные байты, передаваемые по моноканалу и поступающие в УАПП ведомых МК, прерывания не вызывают, т.е. игнорируются. После приема сообщения адресуемый МК устанавливает свой управляющий бит SM2 в «1».

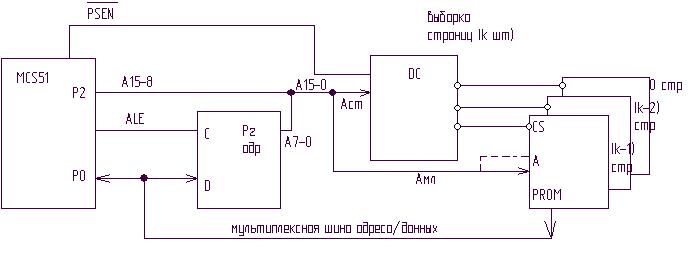

41. Схема интерфейса микроконтроллера mcs-51 с внешней памятью программ, внешней памятью данных и дополнительными портами ввода-вывода.

Интерфейс с внешней памятью программ:

PSEN – разрешение работы с памятью программ, ALE – стробирование адреса

Интерфейс с внешней памятью данных и дополнительными портами ввода-вывода:

Можно применять команду movx для пересылки данных в или из адресованной ячейки (это может быть порт или память данных).

42. Типовой цикл работы микроконтроллера mcs-51. Примеры выполнения команд 1-байтовых, 2-байтовых, с обращением к внешней памяти данных.

43. Применение ацп и цап в мп-системах.

Аналоговый компаратор (на примере ATmega128)

Аналоговый компаратор сравнивает уровни напряжений на неинвертирующем входе AIN0 и инвертирующем входе AIN1. Если напряжение на неинвертирующем входе AIN0 превышает напряжение на инвертирующем входе AIN1, то выход аналогового компаратора ACO принимает единичное состояние. Выход компаратора может быть настроен для использования в качестве источника входного сигнала для схемы захвата фронтов таймера-счетчика 1. Кроме того, компаратор может генерировать собственный запрос на обработку прерывания. Пользователь может выбрать несколько событий, по которым возникает прерывание: нарастающий, падающий фронт на выходе компаратора или любое его изменение.

Включение АК осуществляется установкой бита ADEN регистра ADCSRA. Кроме того, если бит ACME регистра SFIOR установлен (и ADEN=0), то к инвертирующему входу аналогового компаратора подключается выход аналогового мультиплексора АЦП. Сброс данного бита приведет к подключению инвертирующего входа аналогового компаратора к выводу микроконтроллера AIN1. Для управления АК используется регистр ACSR (регистр состояния и управления аналогового компаратора). Его разряды: 7 – ACD: Отключение АК; 6 – ACBG: Подключение источника опорного напряжения к аналоговому компаратору; 5 – ACO: Выход аналогового компаратора; 4 – ACI: Флаг прерывания аналогового компаратора; 3 – ACIE: Разрешение прерывания аналогового компаратора; 2 – ACIC: Подключение аналогового компаратора к схеме захвата фронтов; 1, 0 – ACIS1, ACIS0: Выбор события прерывания аналогового компаратора.

Имеется возможность использовать выводы ADC7..0 в качестве неинвертирующих входов аналогового компаратора. Для организации такого ввода используется мультиплексор АЦП и, следовательно, в этом случае АЦП должен быть отключен. Если установлен бит разрешения подключения мультиплексора к аналоговому компаратору (бит ACME в SFIOR) и выключен АЦП (ADEN=0 в регистре ADCSRA), то состояние разрядов MUX2..0 регистра ADMUX определяют какой вывод микроконтроллера подключен к неинвертирующему входу аналогового компаратора. Если ACME сброшен или установлен ADEN, то в качестве неинвертирующего входа аналогового компаратора используется вывод микроконтроллера AIN1.

Аналого-цифровой преобразователь (на примере ATmega128)

ATmega128 содержит 10-разр. АЦП последовательного приближения. АЦП связан с 8-канальным аналоговым мультиплексором, 8 однополярных входов которого связаны с линиями порта F. Общий входных сигналов должен иметь потенциал 0В (т.е. связан с GND). АЦП также поддерживает ввод 16 дифференциальных напряжений. Два дифференциальных входа (ADC1, ADC0 и ADC3, ADC2) содержат каскад со ступенчатым программируемым усилением: 0 дБ (1x), 20 дБ (10x), или 46 дБ (200x). Семь дифференциальных аналоговых каналов используют общий инвертирующий вход (ADC1), а все остальные входы АЦП выполняют функцию неинвертирующих входов. Если выбрано усиление 1x или 10x, то можно ожидать 8-разр. разрешение, а если 200x, то 7-разрядное. АЦП содержит УВХ (устройство выборки-хранения), которое поддерживает на постоянном уровне напряжение на входе АЦП во время преобразования. АЦП имеет отдельный вывод питания AVCC (аналоговое питание). AVCC не должен отличаться более чем на ± 0.3В от VCC.

В качестве внутреннего опорного напряжения может выступать напряжение от внутреннего ИОНа на 2.56В или напряжение AVCC. Если требуется использование внешнего ИОН, то он должен быть подключен к выводу AREF с подключением к этому выводу блокировочного конденсатора для улучшения шумовых характеристик.

АЦП преобразовывает входное аналоговое напряжение в 10-разр. код методом последовательных приближений. Минимальное значение соответствует уровню GND, а максимальное уровню AREF минус 1 мл. разр.

Канал аналогового ввода и каскад дифференциального усиления выбираются путем записи бит MUX в регистр ADMUX. В качестве однополярного аналогового входа АЦП может быть выбран один из входов ADC0…ADC7, а также GND и выход фиксированного источника опорного напряжения 1,22 В. В режиме дифференциального ввода предусмотрена возможность выбора инвертирующих и неинвертирующих входов к дифференциальному усилителю.

Если выбран дифференциальный режим аналогового ввода, то дифференциальный усилитель будет усиливать разность напряжений между выбранной парой входов на заданный коэффициент усиления. Усиленное таким образом значение поступает на аналоговый вход АЦП. Если выбирается однополярный режим аналогового ввода, то каскад усиления пропускается

Работа АЦП разрешается путем установки бита ADEN в ADCSRA. Выбор опорного источника и канала преобразования не возможно выполнить до установки ADEN. Если ADEN = 0, то АЦП не потребляет ток, поэтому, при переводе в экономичные режимы сна рекомендуется предварительно отключить АЦП.

АЦП генерирует 10-разрядный результат, который помещается в пару регистров данных АЦП ADCH и ADCL.

АЦП генерирует собственный запрос на прерывание по завершении преобразования. Если между чтением регистров ADCH и ADCL запрещен доступ к данным для АЦП, то прерывание возникнет, даже если результат преобразования будет потерян.

Одиночное преобразование запускается путем записи лог. 1 в бит запуска преобразования АЦП ADSC. Данный бит остается в высоком состоянии в процессе преобразования и сбрасывается по завершении преобразования. Если в процессе преобразования переключается канал аналогового ввода, то АЦП автоматически завершит текущее преобразование прежде, чем переключит канал.

В режиме автоматического перезапуска АЦП непрерывно оцифровывает аналоговый сигнал и обновляет регистр данных АЦП. Данный режим задается путем записи лог. 1 в бит ADFR регистра ADCSRA. Первое преобразование инициируется путем записи лог. 1 в бит ADSC регистра ADCSRA. В данном режиме АЦП выполняет последовательные преобразования, независимо от того сбрасывается флаг прерывания АЦП ADIF или нет.

Включение AD78 в систему МК51

Временные диаграммы

Количество каналов для АЦП:

Для ЦАП: , где n – количество разрядов преобразователя, - формирующий сигнал

Аналоговый компаратор в составе AVR