- •Список принятых сокращений

- •Список рисунков

- •Содержание

- •Введение

- •1. Основные понятия и определения

- •2. История развития производства микропроцессоров

- •3. Основные принципы построения процессоров

- •3.1. Микропрограммное управление.

- •3.2. Модульный принцип построения.

- •3.3. Магистральный принцип обмена информацией.

- •3.4. Наращиваемость вычислительной мощности мпс.

- •4. Достигнутый уровень и перспективы развития микроэлектронного производства

- •4.1. Процесс изготовления мп

- •4.2. Закон Мура

- •4.3. Перспективы развития микроэлектроники

- •5. Архитектурные особенности современных микропроцессоров

- •5.1. Типы микропроцессоров

- •5.2. Архитектура процессоров обработки сигналов

- •5.2.1. Архитектура фон Неймана

- •Конвейерная архитектура

- •Суперскалярная архитектура

- •Cisc-процессоры

- •Risc-процессоры

- •Misc-процессоры

- •Vliw-процессоры

- •Многоядерные процессоры

- •Кэширование

- •5.2.2. Гарвардская архитектура

- •5.2.3. Параллельная архитектура

- •6. Развитие архитектур микропроцессоров

- •6.1. Экстенсивные направления развития микропроцессорной техники

- •6.2. Новые направления развития микропроцессорной техники

- •Заключение

- •Тактовая частота — частота синхронизирующих импульсов синхронной электронной схемы, то есть количество синхронизирующих тактов, поступающих извне на вход схемы за одну секунду.

- •Список используемой литературы

5.2.2. Гарвардская архитектура

Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете.

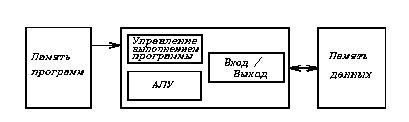

Данная архитектура отличается от архитектуры фон Неймана тем, что программный код и данные хранятся в разной памяти (см. рис.5.7.). В такой архитектуре невозможны многие методы программирования (например, программа не может во время выполнения менять свой код; невозможно динамически перераспределять память между программным кодом и данными); зато гарвардская архитектура позволяет более эффективно выполнять работу в случае ограниченных ресурсов, поэтому она часто применяется во встраиваемых системах.

Рисунок 5.7 - структура Гарвардской архитектуры.

5.2.3. Параллельная архитектура

Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана.

Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах.

Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна):

-

SISD — один поток команд, один поток данных;

-

SIMD — один поток команд, много потоков данных;

-

MISD — много потоков команд, один поток данных;

-

MIMD — много потоков команд, много потоков данных.

Для цифровой обработки сигналов, особенно при ограниченном времени обработки, применяют специализированные высокопроизводительные сигнальные микропроцессоры (DSP) с параллельной архитектурой.

6. Развитие архитектур микропроцессоров

Развитие микропроцессорной техники в области универсальных микропроцессоров идет по пути постоянного повышения их производительности.

6.1. Экстенсивные направления развития микропроцессорной техники

Традиционными направлениями развития микропроцессорной техники являются повышение тактовой частоты работы МП и увеличение количества одновременно выполняемых команд за счет увеличения числа конвейеров (исполнительных устройств) в МП.

Однако оба эти направления следует признать экстенсивными, имеющими естественные ограничения.

Повышение тактовой частоты, которое в основном обеспечивается путем увеличения количества ступеней в конвейере, приводит к большим потерям времени при необходимости перезагрузки конвейера вследствие конфликтов по управлению или при переключении на новую задачу. Такое увеличение имеет также и физические ограничения, связанные со схемотехникой кристалла БИС. Ограничения определяются также влиянием накладных расходов при передаче частично обработанной команды на следующую ступень конвейера (значение t при определении длительности такта). На больших частотах эти расходы становятся соизмеримыми с длительностью обработки на очередном этапе. Во многом это направление исчерпало себя в микропроцессоре Pentium 4, работающем на частотах, близких к 4 ГГц.

Повышение производительности за счет увеличения числа конвейеров в микропроцессоре можно оценить увеличением числа команд, выполняемых программами за такт (IPC - INsTRuctions Per Cycle). Так, для МП Alpha 21264 этот показатель равен 6, столько же микроопераций за такт может выдать Pentium 4. Но это предельные значения, а реальные программные коды, в частности, из-за различных взаимозависимостей, дают гораздо более низкое значение IPC. Дальнейшее увеличение числа исполнительных устройств ведет к усложнению расположенного в БИС устройства управления, распределяющего команды по конвейерам, а также к сложным взаимозависимостям между данными. К тому же реальные коды программ не позволяют обеспечить эффективную загрузку всех имеющихся в МП исполнительных устройств, что приводит к их простоям. Следует отметить также, что рост производительности микропроцессора не является прямо пропорциональным росту количества конвейеров, а обычно существенно ниже.